Способ и устройство суммирования и вычитания двоично-десятичных кодов

Иллюстрации

Показать всеИзобретение относится к области цифровой вычислительной техники и может быть использовано в процессорах ЭВМ и в устройствах цифровой автоматики. Технический результат - повышение быстродействия выполнения операций при минимальных затратах оборудования. Указанный результат достигается за счет того, что устройство в каждом десятичном разряде содержит два RS-триггера (1, 2), логические элементы И (3-33, 48), логические элементы ИЛИ (34-47), логические элементы НЕ (49-53), матрицу сложения 54, одноразрядный трехвходовый сумматор 55, четыре входа управления (56-59). 2 н.п. ф-лы, 1 ил., 3 табл.

Реферат

Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики.

Известны способы и устройства сложения двоично-десятичных кодов, содержащие триггерные регистры, схемы формирования сквозного переноса и суммы, логические элементы И, ИЛИ, НЕ и входы управления работой устройства. Варианты таких устройств детально рассмотрены в книге М.А.Карцева «Арифметика цифровых машин». - М.: Наука, 1969, стр.164-186. Известные устройства обладают определенными недостатками, т.к. требуют больших затрат времени для выполнения корректировки результата суммирования. Известны также способы и устройства «прямого» суммирования десятичных кодов с применением квадратной матрицы сложения в каждом десятичном разряде. Описание работы такого устройства приведено в указанной выше книге М.А.Карцева «Арифметика цифровых машин», стр.176, рис. 2-21. Большим недостатком такого устройства является применение матрицы сложения, требующей не менее 100 элементов И-ИЛИ, что увеличивает оборудование, потребление электропитания и повышает стоимость устройства в целом. Это устройство является ближайшим прототипом предлагаемого способа и устройства сложения и вычитания двоично-десятичных кодов (далее объект). Предлагаемый объект устраняет недостатки известных устройств и прототипа.

Целью предлагаемого объекта является повышение быстродействия выполнения сложения и вычитания за счет исключения операций корректировки суммы и снижение оборудования матрицы сложения. Для этого предложены способ, отличающийся тем, что при выполнении сложения по первому временному такту принимают код второго слагаемого во второй триггерный регистр, преобразуют двоично-десятичные коды второго и третьего двоичных разрядов каждого десятичного разряда первого и второго слагаемых в четные десятичные числа 6, 4, 2, определяют наличие нулевых значений кодов во втором, третьем и четвертом двоичных разрядах слагаемых, по второму временному такту выполняют сложение четных десятичных чисел с помощью матрицы сложения на пять входов первого слагаемого и на пять входов второго слагаемого, при этом коды первого двоичного разряда слагаемых и сигнал переноса из младшего десятичного разряда суммируют с помощью трехвходового одноразрядного сумматора, по значениям суммы матрицы сложения и сигнала переноса из сумматора первого двоичного разряда формируют значение десятичного кода суммы во втором, третьем и четвертом двоичных разрядах и сигнал переноса в старший десятичный разряд, преобразуют результат суммирования матрицы сложения и переноса из первого двоичного разряда из десятичного кода в двоично-десятичный код 8, 4, 2, и по третьему временному такту заносят результат суммирования в триггеры первого регистра, при выполнении операции вычитания одновременно с приемом кода во второй триггерный регистр выполняют преобразование двоично-десятичных кодов второго и третьего двоичных разрядов каждой тетрады упомянутых регистров из двоично-десятичного кода в четные десятичные числа 6, 4, 2, определяют нулевое значение кодов второго-четвертого двоичных разрядов каждой тетрады регистров и формируют дополнение до девяти одного из десятичных чисел 8, 6, 4, 2, 0 и инверсный код первого двоичного разряда каждой тетрады первого регистра, по второму временному такту производят формирование суммы в каждом десятичном разряде с помощью матрицы сложения на пять вертикальных входов, соответствующих значениям одного из десятичных чисел 8, 6, 4, 2, 0 тетрад В, на пять горизонтальных входов, соответствующих значениям дополнения до девяти одного из десятичных чисел 8, 6, 4, 2, 0 тетрад А, полученное в каждом десятичном разряде одно из четных чисел 16, 14, 12, 10, 8, 6, 4, 2, 0, при наличии переноса из первого двоичного разряда, увеличивают на две единицы, формируют сигнал переноса в старший десятичный разряд при сумме, равной 18, 16, 12 и 10, по третьему временному такту заносят результат суммирования в дополнительном коде в первый триггерный регистр, при этом, если сигнал переноса из старшего разряда устройства равен нулю, то знак результата положительный, при наличии упомянутого сигнала переноса результат операции вычитания отрицательный, по этому же такту в триггер признака кода регистра А всегда заносится код единицы, на этом выполнение операции вычитание завершают, а также предложено устройство, отличающееся тем, что каждый двоичный разряд содержит первый и второй RS-триггеры, при этом первый RS-триггер содержит первый-четвертый элементы НЕ, первый-третий элементы И, первый элемент ИЛИ, нулевой и единичный входы первого RS-триггера соединены с выходами первого и второго элементов НЕ, выход первого элемента И через первый элемент ИЛИ соединен с первым входом третьего элемента И, второй вход этого элемента соединен с выходом второго элемента НЕ, единичный выход первого RS-триггера подключен к второму входу первого элемента ИЛИ, выход третьего элемента И соединен с первым входом первого элемента И и с входом третьего элемента НЕ, выход которого связан с первым входом второго элемента И, вторые входы первого и второго элементов И соединены с выходом и входом четвертого элемента НЕ соответственно, третьи входы упомянутых элементов И соединены с входом управления приемом суммы в первый триггерный регистр, каждый десятичный разряд содержит четырехразрядные регистры первого и второго слагаемых - тетрады А и В, логические элементы И преобразования двоично-десятичных кодов тетрад А и В второго и третьего разрядов в десятичные числа 6, 4, 2, матрицу сложения четных десятичных чисел, содержащую шестнадцать элементов И-ИЛИ, пять горизонтальных и пять вертикальных входов, соответствующих значениям десятичных чисел тетрад А и В, входы каждого элемента И подключены к упомянутым входам десятичных чисел, выходы элементов И-ИЛИ, расположенных на диагональных линиях матрицы, соединены между собой и являются значениями суммы двух десятичных чисел тетрад А и В, схемы формирования сигнала переноса в старший десятичный разряд и преобразования четных десятичных чисел в двоично-десятичный код, схему сложения десятичных чисел матрицы сложения с сигналом переноса из первого двоичного разряда, соответствующему десятичному числу два, на элементах И-ИЛИ, элементы И выдачи кода тетрад А и В на входы матрицы сложения, элементы И-ИЛИ выдачи кода дополнения до девяти регистра А на горизонтальные входы матрицы сложения, логические элементы И, ИЛИ, НЕ определения нулевых значений кодов второго-четвертого разрядов тетрад А и В, первый вход управления выдачей кода тетрады В на вертикальные входы матрицы, второй вход управления приемом суммы в тетраду А, третий и четвертый входы управления выполнением операции сложения и вычитания соответственно, при этом четвертый, пятый и шестой элементы И образуют схему преобразования кода второго и третьего двоичных разрядов тетрады А в четные десятичные числа 6, 4, и 2, входы четвертого элемента И связаны с выходами третьих элементов И второго и третьего разрядов, входы пятого элемента И соединены с выходами третьих элементов И и НЕ третьего и второго разрядов, входы шестого элемента И связаны с выходами третьих элементов НЕ и И третьего и второго разрядов, седьмой, восьмой и девятый элементы И образуют схему преобразования кодов второго и третьего разрядов тетрады В в четное десятичное число 6, 4 и 2, входы седьмого элемента И соединены с единичными выходами вторых триггеров второго и третьего разрядов, входы восьмого элемента И связаны с единичным и нулевым выходами триггеров третьего и второго разряда, входы девятого элемента И подключены к нулевому и единичному выходам триггеров третьего и второго разрядов тетрады В, выходы седьмого-девятого элементов И соединены с девятым, восьмым и седьмым входами матрицы сложения соответственно, единичный выход второго триггера четвертого разряда подключен к первому входу десятого элемента И, второй вход которого соединен с первым входом управления сложения, выход десятого элемента И подключен к десятому входу матрицы сложения, вход одиннадцатого элемента И соединен с нулевыми выходами вторых триггеров второго-четвертого разрядов, выход упомянутого элемента И подключен к шестому входу матрицы сложения, единичный выход второго триггера первого разряда тетрады В подключен к первому входу двенадцатого элемента И, второй вход которого соединен с первым входом управления, выход упомянутого элемента И соединен с первым входом сумматора первого двоичного разряда, второй и третий входы которого связаны с входом переноса из младшего десятичного разряда и выходом одиннадцатого элемента ИЛИ, выход суммы упомянутого сумматора соединен с входом четвертого элемента НЕ первого разряда тетрады В, третьи входы седьмого-девятого элементов И соединены с первым входом управления, первые входы тринадцатого и четырнадцатого элемента И соединены с выходами третьих элементов НЕ, И первого разряда тетрады А, их выходы подключены к входам одиннадцатого элемента ИЛИ, первые входы пятнадцатого-семнадцатого элементов И соединены с выходами шестого-четвертого элементов И, выходы пятнадцатого и шестнадцатого элементов И связаны с входами двенадцатого и тринадцатого элементов ИЛИ, первые входы восемнадцатого-двадцатого элементов И соединены с выходами шестого, пятого и четвертого элементов И соответственно, выход восемнадцатого И связан с входами двенадцатого и тринадцатого элементов ИЛИ, выход девятнадцатого И соединен с входом тринадцатого ИЛИ, выход двадцатого И подключен к входу двенадцатого ИЛИ, первый вход двадцать первого И соединен с выходом двадцать третьего элемента И, первый вход двадцать второго И подключен к выходу третьего И, выходы двадцать первого и двадцать второго элементов И подключены к входам четырнадцатого элемента ИЛИ, вторые входы четырнадцатого-семнадцатого и двадцать второго элементов И соединены с третьим входом управления, вторые входы тринадцатого, восемнадцатого, девятнадцатого, двадцатого и двадцать первого И соединены с четвертым входом управления, входы двадцать третьего И подключены к выходам третьих элементов НЕ второго-четвертого разрядов тетрады А, выходы двенадцатого, тринадцатого ИЛИ, семнадцатого И, четырнадцатого ИЛИ соединены с 2, 3, 4, и 5 горизонтальными входами матрицы сложения соответственно и с входами второго элемента ИЛИ, выход которого через пятый элемент НЕ соединен с первым входом матрицы сложения, первый выход упомянутой матрицы связан с первым входом двадцать пятого элемента И, второй-четвертый выходы матрицы соединены с входами четвертого-шестого элементов ИЛИ, пятый выход связан первыми входами тридцатого и тридцать второго элементов И, шестой выход соединен с входом третьего элемента ИЛИ, седьмой выход соединен с входами третьего и четвертого элементов ИЛИ, восьмой выход связан с третьим и пятым элементами ИЛИ, девятый выход подключен к входам третьего и шестого элементов ИЛИ, выход четвертого ИЛИ связан с первыми входами двадцать четвертого и двадцать седьмого элементов И, выход пятого ИЛИ подключен к входам двадцать шестого и двадцать девятого элементов И, выход шестого ИЛИ соединен с входами двадцать восьмого и тридцать первого элементов И, вторые входы двадцать четвертого, двадцать шестого, двадцать восьмого и тридцатого элементов И подключены к третьему выходу сумматора первого разряда, вторые входы двадцать пятого, двадцать седьмого, двадцать девятого, тридцать первого и тридцать второго элементов И подключены к второму выходу упомянутого сумматора, выходы двадцать четвертого и двадцать пятого элементов И через седьмой элемент ИЛИ соединены с входом четвертого НЕ второго разряда, выходы двадцать шестого и двадцать седьмого элементов И через восьмой элемент ИЛИ соединена с входом четвертого НЕ третьего разряда, выходы двадцать восьмого и двадцать девятого элементов И подключены к входом восьмого и седьмого элементов ИЛИ, выходы тридцатого и тридцать первого элементов И через десятый элемент ИЛИ подключены к входу четвертого элемента НЕ четвертого разряда, выход тридцать второго И соединен с входом третьего ИЛИ, выход которого является выходом переноса из i-го десятичного разряда в старший разряд, кроме того, в триггерный регистр А введен триггер признака дополнительного кода, хранящегося в упомянутом регистре, при значении кода триггера, равного единице, в регистре А хранится дополнение до девяти результата выполнения операции вычитания.

Рассмотрим основные отличительные характеристики объекта и что конкретно они обеспечивают.

1. По предлагаемому способу по первому временному такту преобразуют коды слагаемых из кода «8, 4, 2, 1» в код «8, 6, 4, 2, 1» и суммируют десятичные числа 8, 6, 4, 2 и нулевое значение триггеров второго, третьего и четвертого разрядов слагаемых с помощью матрицы сложения (МС), а коды слагаемых первого двоичного разряда суммируют с помощью одноразрядного трехвходового сумматора (ОТС).

2. Предложенный способ позволяет повысить быстродействие выполнения операции сложения и вычитания в два-три раза и снизить число логических элементов И-ИЛИ для построения матрицы сложения одного десятичного разряда приблизительно в четыре раза, снизить число RS-триггеров для построения каждого десятичного разряда с двенадцати до восьми, снизить временную задержку сигнала переноса в каждом десятичном разряде с 9τ до 5τ, т.е. почти в два раза.

3. Выполнение операции вычитания сводится к сложению дополнения до девяти десятичных чисел, хранящихся во втором-четвертом разрядах тетрад А, с десятичными числами, хранящимися в упомянутых разрядах тетрад В, при этом в первых разрядах всех тетрад суммируют инверсный код триггеров тетрад А с прямым кодом триггеров тетрад В.

Основные характеристики трех сравниваемых устройств (устройство с использованием сумматоров комбинационного типа, прототипа и предлагаемого объекта) приведены в таблице 1.

| Таблица 1 | |||||

| № | Наименование характеристик | Устройство комбинационного типа | Прототип | Предлагаемый объект | Примечание |

| 1 | Операция преобразования десятичного кода в двоичный и наоборот | Есть | Нет | Нет | Повышается быстродействие по сравнению с устройствами комбинационного типа |

| 2 | Операция корректировки кода при сложении двоично-десятичных чисел | Есть | Нет | Нет | Повышается быстродействие по сравнению с устройствами комбинационного типа |

| 3 | Наличие матрицы сложения в каждом десятичном разряде | - | Есть | Есть | |

| 4 | Число элементов И-ИЛИ для построения матрицы, в ед. | - | 100 | 25 | |

| 5 | Число RS-триггеров для построения одного десятичного разряда, в ед. | 12 | 12 | 8 | |

| 6 | Время выполнения операции сложения и вычитания (прием, формирование переноса, запоминание суммы), в тактах, ед. | 6 | 4 | 3 | |

| 7 | Максимальное число времен, задержек сигнала переноса на элементах И (ИЛИ) в одном десятичном разряде, ед. | 9τ | 4τ | 5τ | |

| 8 | Число одноразрядных двоичных сумматоров в десятичном разряде, ед. | 4 | - | 1 | |

| 9 | Оценка оборудования одного десятичного разряда (цена Квайна) | 250 (100%) | 456 (180%) | 325 (130%) |

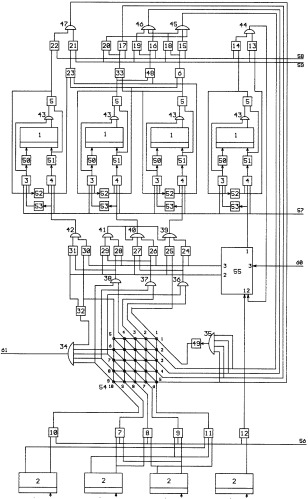

Для пояснения работы предлагаемого объекта на чертеже приведена функциональная схема одного десятичного разряда устройства.

На чертеже приняты следующие обозначения: RS-триггеры (Tr) 1, 2, элементы И 3-33, 48; элементы ИЛИ 34-47; элементы НЕ 49-53, матрица сложения (МС) 54, одноразрядный трехвходовый сумматор (ОТС) 55, первый-четвертый входы управления (ВУ) 56, 57, 58, 59 соответственно, вход сигнала переноса из младшего десятичного разряда 60, выход сигнала переноса из i-го десятичного разряда 61.

Предложенный объект осуществляется следующим образом. В каждом двоичном разряде единичный выход Tr1 через ИЛИ 43, И 5 соединен с входами И 3, НЕ 52, выход НЕ 52 соединен с И 4, выход и вход НЕ 53 соединены с вторыми входами И 3, 4, третьи входы этих элементов соединены с ВУ 57. Выходы И 3, 4 через НЕ 50, 51 соединены с нулевым и единичным входами Tr1. Выход И3 связан с ИЛИ 43, выход НЕ 51 соединен с И 5. В каждом десятичном разряде выходы И 5 и НЕ 52 второго и третьего двоичных разрядов соединены с входами И 6, выходы НЕ 52 второго разряда и И 5 третьего разряда связаны с входами И 48, выходы И 5 второго и третьего разрядов подключены к входам И 33, выходы элементов И 6, 48, 33 соединенны с входами И 15, 18, с входами И 16, 19 и с входами И 17, 20 соответственно, первый вход И 22 связан с выходом И 5 четвертого разряда, вторые входы И 14-17, 22 подключены к ВУ 58, вторые входы И 13, 18, 19, 20 и 21 подключены к ВУ 59, первый вход И 21 соединен с выходом И 23, выходы И 15, 18, 20 подключены к ИЛИ 45, выходы И 16, 18, 19 подключены к ИЛИ 46, выходы И 21, 22 подключены к ИЛИ 47, выходы ИЛИ 45, 46, И 17, ИЛИ 47 соединены с входами ИЛИ 35 и с 2, 3, 4, и 5 входами МС 54, выход ИЛИ 35 через НЕ 49 подключен к первому входу МС 54, первые входы И 13, 14 связаны с НЕ 52, И 5 первого разряда соответственно, выходы И 13, 14 подключены к ИЛИ 44, выход которого соединен с вторым входом ОТС 55. Входы И 23 соединенны с выходами НЕ 52 второго-четвертого разрядов тетрады А. Третий вход ОТС 55 соединен с входом 60, единичные выходы Tr 2 первого-четвертого разрядов соединены соответственно с И 12, с И 9, 7, с И 8, 7 и с И 10, ВУ 56 соединен с вторыми входами И 10, 12 и с третьими входами И 7-9. Нулевые выходы Tr 2 второго и третьего разрядов соединены с И 8, 9. Нулевые выходы Tr2 второго-четвертого разрядов соединены с входами И 11, выход которых подключен к 6 входу МС 54. Выход И 7 соединен с девятым входом МС 54, выход И 8 связан с восьмым входом матрицы, выход И 9 соединен с седьмым входом матрицы, выход И 10 подключен к 10 входу МС 54. Первый выход МС 54 соединен с И 25, второй-четвертый выходы связаны с ИЛИ 36, 37, 38, пятый выход подключен к входам И 30, 32, шестой выход соединен с ИЛИ 34, седьмой-девятый выходы соединены с ИЛИ 34 и ИЛИ 36-38 соответственно. Выходы ИЛИ 36-38 связаны соответственно с И 24, 27, с И 26, 29 и с И 28, 31; вторые входы И 24, 26, 28, 30 соединены с третьим выходом ОТС 55, второй выход ОТС 55 соединен с И 25, 27, 29, 31, 32, выходы И 24, 25 и 26, 27 и 28, 29 и 30 и 31 подключены к входам ИЛИ 39, 40, 41 и 42 соответственно, выход ИЛИ 42 связан с входом НЕ 53 четвертого двоичного разряда, выход ИЛИ 41 соединен с ИЛИ 40, 39, выходы ИЛИ 40, 39 связаны с входами НЕ 53 третьего и второго разрядов соответственно. Первый выход ОТС 55 соединен с входом НЕ 53 первого разряда, первый вход упомянутого сумматора подключены к выходу И 12, выход И 32 соединен с ИЛИ 34.

Рассмотрим работу устройства при выполнении операций сложения и вычитания.

1. Операция сложения. В исходном положении код первого слагаемого хранится в Tr1 первого-четвертого двоичных разрядов. По первому временному и до конца выполнения сложения на второй, третий, четвертый и пятый входы МС 54 и второй вход ОТС 55 поступает прямой код с Tr1 тетрады А. Для этого на ВУ 58 подается высокий потенциал, который по цепи элементов И 14-17 и 22, через ИЛИ 44-47 и И 17 поступает на горизонтальные входы МС 54 и второй вход ОТС 55. По этому же временному такту код второго слагаемого принимается в Tr2, одновременно на ВУ 56 поступает потенциал, разрешающий выдачу кода Tr2 на вертикальные входы МС 54 и первый вход ОТС 55. Второй временной такт отводится для формирования суммы каждого двоичного разряда и максимального по суммарным временным задержкам сигнала переноса, равного 4 nτ (n - число десятичных разрядов, τ - задержка сигнала переноса на одном элементе И (ИЛИ)). После завершения формирования переноса и суммы в каждом десятичном разряде, по третьему временному такту на ВУ 57 поступает потенциал управления приемом суммы в Tr1, сформированной на первом-девятом выходах МС 54, на выходах ИЛИ 36, 37, 38 и на 1, 2 и 3 выходах ОТС 54. При этом, если на втором выходе ОТС 54 отсутствует, а на третьем выходе присутствует высокий потенциал, т.е. из первого двоичного разряда не поступил перенос на входы И 25, 27, 29, 31 и 32, то сигнал, соответствующий четному десятичному числу, передается по цепи элементов И 24, 26, 28, 30, ИЛИ 39, 40, 42, И 4 и НЕ 51 на вход Tr1 второго, третьего или четвертого разрядов и с первого выхода ОТС 55 через И 4, НЕ 51 на вход Tr1 первого разряда. В том случае, если с второго выхода ОТС 55 в старшие двоичные разряды поступил сигнал переноса, то сумма, полученная с выходов ИЛИ 36-38, увеличивается на две единицы. Для выполнения элементарной операции занесения суммы в Tr1 по ВУ 57 на входы И 3, 4 всех двоичных разрядов поступает потенциал управления приемом суммы. Если на выходах ИЛИ 39, 40, 42 и первом выходе ОТС 55 присутствуют высокие потенциалы, то импульс проходит по цепи элементов И 4, НЕ 51 на единичный вход Tr1 и установит его в единицу. При этом с выхода И 5 высокий потенциал на вход МС 54 будет поступать с задержкой по времени, равной длительности импульса, поступившего по ВУ 57. Это обеспечивается отключенном И 5 при установке Tr1 в единицу за счет связи с выхода НЕ 51 с входом И 5 и искусственном поддержании высокого потенциала с И 5 за счет поступления импульса с выхода И 3 на вход И 5. Примеры выполнения операции сложения приведены в таблице 2.

| Таблица 2 | |||||

| Регистр | А>В | А=В | А<В | Примечания | |

| сложение | |||||

| Первое слагаемое | А | Прямой код | |||

| Второе слагаемое | В | Прямой код | |||

| Сумма | А' | 601 | 306 | 870 | Прямой код |

| вычитание | |||||

| Уменьшаемое | А | ||||

| Вычитаемое | В | ||||

| Разность | А' | 209 | 000 | -848 | |

| Дополнение до девяти | А | ||||

| Вычитаемое | В | Прямой код | |||

| Разность | A' | [1] 790 | [1] 999 | [1] 1151 | Дополнительный код |

| Разность | A” | [0] 209 | [0] 000 | [0] -848 | Прямой код |

| Таблица 3 | |||

| Десятичное число | Двоично десятичный код | Дополнение до 9 десятичного числа | Двоично десятичный код дополнения |

| 0 | 0000 | 9 | 1001 |

| 1 | 0001 | 8 | 1001 |

| 2 | 0010 | 7 | 0111 |

| 3 | 0011 | 6 | 0110 |

| 4 | 0100 | 5 | 0101 |

| 5 | 0101 | 4 | 0100 |

| 6 | 0110 | 3 | 0011 |

| 7 | 0111 | 2 | 0010 |

| 8 | 1000 | 1 | 0001 |

| 9 | 100 1 | 0 | 0000 |

2. Операция вычитания. Работа устройства при выполнении операции вычитания аналогична выполнению операции сложения. Отличие состоит в том, что в течение всей операции на ВУ 59 поступает высокий потенциал, обеспечивающий выдачу дополнительного кода тетрады А на входы 2, 3, 4, 5 МС 54 и инверсного кода Tr1 первого разряда на второй вход ОТС 55. В таблице 3 приведены прямые и дополнительные коды одного десятичного разряда. По первому временному такту в Tr1 принимается код вычитаемого, одновременно на ВУ 56 поступает высокий потенциал, разрешающий преобразование кодов второго и третьего разрядов тетрад В в десятичное число 6, 4, 2 и выдачу этих значений на входы 9, 8, 7 МС 54. Значение кодов первого и четвертого разрядов через И 12, И 10 передается на первый вход ОТС 55 и десятый вход упомянутой матрицы. Второй временной такт отводится для формирования переносов и суммы во всех десятичных разрядах. По третьему временному такту результат суммирования дополнительного кода тетрады А с прямым кодом тетрады В заносится в триггеры тетрад А. Одновременно в триггерном регистре А устанавливается в единицу триггер, сигнализирующий о занесении в регистр А дополнительного кода разности (на функциональной схеме одного десятичного разряда триггер не приводится). Примеры выполнения операции вычитания приведены в таблице 3.

Таким образом, предложенные способ и устройство сложения и вычитания двоично-десятичных кодов обеспечивают повышение быстродействия выполнения вычислительных операций при минимальных затратах оборудования.

1. Способ суммирования и вычитания двоично-десятичных кодов, заключающийся в том, что первое слагаемое или уменьшаемому хранят в первом триггерном регистре А, второе слагаемое или вычитаемое принимают во второй триггерный регистр В, каждые четыре двоичных разряда представляют один десятичный разряд или тетраду А или В, по первому временному такту принимают второе слагаемое или вычитаемое во второй триггерный регистр В, второй временной такт отводят для формирования сигналов переноса и суммы в каждом двоичном разряде, по третьему временному такту результат суммирования или вычитания заносят в первый триггерный регистр, отличающийся тем, что при выполнении сложения по первому временному такту принимают код второго слагаемого во второй триггерный регистр, преобразуют двоично-десятичные коды второго и третьего двоичных разрядов каждого десятичного разряда первого и второго слагаемых в четные десятичные числа 6, 4, 2, определяют наличие нулевых значений кодов во втором, третьем и четвертом двоичных разрядах слагаемых, по второму временному такту выполняют сложение четных десятичных чисел с помощью матрицы сложения на пять входов первого слагаемого и на пять входов второго слагаемого, при этом коды первого двоичного разряда слагаемых и сигнал переноса из младшего десятичного разряда суммируют с помощью трехвходового одноразрядного сумматора, по значениям суммы матрицы сложения и сигнала переноса из сумматора первого двоичного разряда формируют значение десятичного кода суммы во втором, третьем и четвертом двоичных разрядах и сигнал переноса в старший десятичный разряд, преобразуют результат суммирования матрицы сложения и переноса из первого двоичного разряда из десятичного кода в двоично-десятичный код 8, 4, 2 и по третьему временному такту заносят результат суммирования в триггеры первого регистра, при выполнении операции вычитания одновременно с приемом кода во второй триггерный регистр выполняют преобразование двоично-десятичных кодов второго и третьего двоичных разрядов каждой тетрады упомянутых регистров из двоично-десятичного кода в четные десятичные числа 6, 4, 2, определяют нулевое значение кодов второго-четвертого двоичных разрядов каждой тетрады регистров и формируют дополнение до девяти одного из десятичных чисел 8, 6, 4, 2, 0 и инверсный код первого двоичного разряда каждой тетрады первого регистра, по второму временному такту производят формирование суммы в каждом десятичном разряде с помощью матрицы сложения на пять вертикальных входов, соответствующих значениям одного из десятичных чисел 8, 6, 4, 2, 0 тетрад В, на пять горизонтальных входов, соответствующих значениям дополнения до девяти одного из десятичных чисел 8, 6, 4, 2, 0 тетрад А, полученное в каждом десятичном разряде одно из четных чисел 16, 14, 12, 10, 8, 6, 4, 2, 0, при наличии переноса из первого двоичного разряда, увеличивают на две единицы, формируют сигнал переноса в старший десятичный разряд при сумме, равной 18, 16, 12 и 10, по третьему временному такту заносят результат суммирования в дополнительном коде в первый триггерный регистр, при этом если сигнал переноса из старшего разряда устройства равен нулю, то знак результата положительный, при наличии упомянутого сигнала переноса результат операции вычитания отрицательный, по этому же такту в триггер признака кода регистра А всегда заносится код единицы, на этом выполнение операции вычитание завершают.

2. Устройство суммирования и вычитания двоично-десятичных кодов, выполненное на основе логических элементов И, ИЛИ, НЕ и RS-триггеров, отличающееся тем, что каждый двоичный разряд содержит первый и второй RS-триггеры, при этом первый RS-триггер содержит первый-четвертый элементы НЕ, первый-третий элементы И, первый элемент ИЛИ, нулевой и единичный входы первого RS-триггера соединены с выходами первого и второго элементов НЕ, выход первого элемента И через первый элемент ИЛИ соединен с первым входом третьего элемента И, второй вход этого элемента соединен с выходом второго элемента НЕ, единичный выход первого RS-триггера подключен к второму входу первого элемента ИЛИ, выход третьего элемента И соединен с первым входом первого элемента И и с входом третьего элемента НЕ, выход которого связан с первым входом второго элемента И, вторые входы первого и второго элементов И соединены с выходом и входом четвертого элемента НЕ соответственно, третьи входы упомянутых элементов И соединены с входом управления приемом суммы в первый триггерный регистр, каждый десятичный разряд содержит четырехразрядные регистры первого и второго слагаемых - тетрады А и В, логические элементы И преобразования двоично-десятичных кодов тетрад А и В второго и третьего разрядов в десятичные числа 6, 4, 2, матрицу сложения четных десятичных чисел, содержащую шестнадцать элементов И-ИЛИ, пять горизонтальных и пять вертикальных входов, соответствующих значениям десятичных чисел тетрад А и В, входы каждого элемента И подключены к упомянутым входам десятичных чисел, выходы элементов И-ИЛИ, расположенных на диагональных линиях матрицы, соединены между собой и являются значениями суммы двух десятичных чисел тетрад А и В, схемы формирования сигнала переноса в старший десятичный разряд и преобразования четных десятичных чисел в двоично-десятичный код, схему сложения десятичных чисел матрицы сложения с сигналом переноса из первого двоичного разряда, соответствующего десятичному числу два, на элементах И-ИЛИ, элементы И выдачи кода тетрад А и В на входы матрицы сложения, элементы И-ИЛИ выдачи кода дополнения до девяти регистра А на горизонтальные входы матрицы сложения, логические элементы И, ИЛИ, НЕ определения нулевых значений кодов второго-четвертого разрядов тетрад А и В, первый вход управления выдачей кода тетрады В на вертикальные входы матрицы, второй вход управления приемом суммы в тетраду А, третий и четвертый входы управления выполнением операции сложения и вычитания соответственно, при этом четвертый, пятый и шестой элементы И образуют схему преобразования кода второго и третьего двоичных разрядов тетрады А в четные десятичные числа 6, 4, и 2, входы четвертого элемента И связаны с выходами третьих элементов И второго и третьего разрядов, входы пятого элемента И соединены с выходами третьих элементов И и НЕ третьего и второго разрядов, входы шестого элемента И связаны с выходами третьих элементов НЕ и И третьего и второго разрядов, седьмой, восьмой и девятый элементы И образуют схему преобразования кодов второго и третьего разрядов тетрады В в четное десятичное число 6, 4 и 2, входы седьмого элемента И соединены с единичными выходами вторых триггеров второго и третьего разрядов, входы восьмого элемента И связаны с единичным и нулевым выходами триггеров третьего и второго разрядов, входы девятого элемента И подключены к нулевому и единичному выходам триггеров третьего и второго разрядов тетрады В, выходы седьмого-девятого элементов И соединены с девятым, восьмым и седьмым входами матрицы сложения соответственно, единичный выход второго триггера четвертого разряда подключен к первому входу десятого элемента И, второй вход которого соединен с первым входом управления, выход десятого элемента И подключен к десятому входу матрицы сложения, входы одиннадцатого элемента И соединены с нулевыми выходами вторых триггеров второго-четвертого разрядов, выход упомянутого элемента И подключен к шестому входу матрицы сложения, единичный выход второго триггера первого разряда тетрады В подключен к первому входу двенадцатого элемента И, второй вход которого соединен с первым входом управления, выход упомянутого элемента И соединен с первым входом сумматора первого двоичного разряда, второй и третий входы которого связаны с входом переноса из младшего десятичного разряда и выходом одиннадцатого элемента ИЛИ, выход суммы упомянутого сумматора соединен с входом четвертого элемента НЕ первого разряда тетрады В, третьи входы седьмого-девятого элементов И соединены с первым входом управления, первые входы тринадцатого и четырнадцатого элементов И соединены с выходами третьих элементов НЕ, И первого разряда тетрады А, их выходы подключены к входам одиннадцатого элемента ИЛИ, первые входы пятнадцатого-семнадцатого элементов И соединены с выходами шестого-четвертого элементов И, выходы пятнадцатого и шестнадцатого элементов И связаны с входами двенадцатого и тринадцатого элементов ИЛИ, первые входы восемнадцатого-двадцатого элементов И соединены с выходами шестого, пятого и четвертого элементов И соответственно, выход восемнадцатого элемента И связан с входами двенадцатого и тринадцатого элементов ИЛИ, выход девятнадцатого элемента И соединен с входом тринадцатого элемента ИЛИ, выход двадцатого элемента И подключен к входу двенадцатого элемента ИЛИ, первый вход двадцать первого элемента И соединен с выходом двадцать третьего элемента И, первый вход двадцать второго элемента И подключен к выходу третьего элемента И, выходы двадцать первого и двадцать второго элементов И подключены к входам четырнадцатого элемента ИЛИ, вторые входы четырнадцатого-семнадцатого и двадцать второго элементов И соединены с третьим входом управления, вторые входы тринадцатого, восемнадцатого, девятнадцатого, двадцатого и двадцать первого элемента И соединены с четвертым входом управления, входы двадцать третьего элемента И подключены к выходам третьих элементов НЕ второго-четвертого разрядов тетрады А, выходы двенадцатого, тринадцатого элемента ИЛИ, семнадцатого элемента И, четырнадцатого элемента ИЛИ соединены с 2, 3, 4, и 5 горизонтальными входами матрицы сложения соответственно и с входами второго элемента ИЛИ, выход которого через пятый элемент НЕ соединен с первым входом матрицы сложения, первый выход упомянутой матрицы связан с первым входом двадцать пятого элемента И, второй-четвертый выходы матрицы соединены с входами четвертого-шестого элементов ИЛИ, пятый выход связан с первыми входами тридцатого и тридцать второго элементов И, шестой выход соединен с входом третьего элемента ИЛИ, седьмой выход соединен с входами третьего и четвертого элементов ИЛИ, восьмой выход связан с третьим и пятым элементами ИЛИ, девятый выход подключен к входам третьего и шестого элементов ИЛИ, выход четвертого элемента ИЛИ связан с первыми входами двадцать четвертого и двадцать седьмого элементов И, выход пятого элемента ИЛИ подключен к входам двадцать шестого и двадцать девятого элементов И, выход шестого элемента ИЛИ соединен с входами двадцать восьмого и тридцать первого элементов И, вторые входы двадцать четвертого, двадцать шестого, двадцать восьмого и тридцатого элементов И подключены к третьему выходу сумматора первого разряда, вторые входы двадцать пятого, двадцать седьмого, двадцать девятого, тридцать первого и тридцать второго элементов И подключены к второму выходу упомянутого сумматора, выходы двадцать четвертого и двадцать пятого элементов И через седьмой элемент ИЛИ соединены с входом четвертого элемента НЕ второго разряда, выходы двадцать шестого и двадцать седьмого элементов И через восьмой элемент ИЛИ соединены с входом четвертого элемента НЕ третьего разряда, выходы двадцать восьмого и двадцать девятого элементов И подключены к входом восьмого и седьмого элементов ИЛИ, выходы тридцатого и тридцать первого элементов И через десятый элемент ИЛИ подключены к входу четвертого элемента НЕ четвертого разряда, выход тридцать второго элемента И соединен с входом третьего элемента ИЛИ, выход которого является выходом переноса из i-го десятичного разряда в старший разряд, кроме того, в триггерный регистр А введен триггер признака дополнительного кода, хранящегося в упомянуто