Аналого-цифровой преобразователь напряженияв код

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

И АВТОРСИОЗМУ СВЙДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республин

Зависимое от авт. свидетельства ¹

1ХГI 1 !11,. O ;!

Заявлено 21.Ч1.1967 (¹ 1167S96 18-24) с присоединением заявки ¹

:, .11;х .т 66! !

Приоритет

Комитет по делам ввойретений и открытий пои Совете Министров

СССР

Опубликовано 10.111.1969. Вюллcтeш, № 10

Дата опубликования описания 14Л 111.1969

У.J 1х 631. l25(0SS.S) . "Й еГ. ЗДЩ, Авторы изобретения

Ю. П. Жарков и Г. И. Кузнецов

ЗяяВитсль

Специальное конструкторское бюро математических машин и тензометрических приборов

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕН И>1

В КОД

Известны аналого-цифровые преобразователи напря>кения в код поразрядного I ozIIpoвания, содержащие регистр, к выходам которого подключены управляемый делитель напряжения и выключающий дешифратор, подсоединенный своими входами к схеме сравнения и регистру, а также синхронизирующее устройство. Зги устройства сложны по конструкции, содержат большое число элементов и имеют недостаточное быстродействие, так как для включения разрядов них применяются коммутаторы.

Предлагаемый преобразователь отличается тем, что он содер>кит включающий дешифратор, подключенный своим выходом ко входу регистра, а входами — к синхронизирующему устройству и регистру. Это упрощает преобразователь и увеличивает его быстродействие.

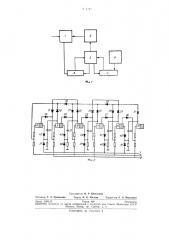

На фиг. 1 приведена блок-схема преобразователя; на фиг. 2 — разряды регистра с подсоединенными к нему элементами дешифраторов.

Преобразователь состоит из схемы сравнения 1, управляемого делителя напряжения 2, регистра 3, синхронизирующего устройства 4, включа!ощего 5 и выключающего б дешифраторов.

Синхронизирующее устройство вырабатывает нечетные и четные синхроимпульсы, под воз!действием которых переключаются тригГеры рсГистрЯ 8, а ттlкжс имп1 льс!э! Сброса, Возвращающие тр;и>геры регистра псрсд кяжДЫМ ИЗМЕРСiiiiCМ В IICX03IIOC СОСТО>1;1ИС, COOTвс Гст В1 !Ощее кбдх «О» ВО Всех p33pH3:.I> .

5 Управляемый делитель напряжения под

Hpï0cpcäc Iâåííûì Воздействием три!>герои регисгра Вырабатывает эталонное компcIIciiph щес напри; eiiiie, подавасмое ня схему срявН С;1:1Я.

10 Схс.ця сравнения 1 сравнивает измсрясмое напряжение с компенсиру10щим и в случае превышеiiiiil ком пснсир ющсГО на!1ряжеllilH выда<т по шине (сигнал (Отрilцательное Ii;IIlpH>i<сние), по которому производится сброс д трип ера регистра, выззавшего псребаланс

ПР ВКЛЮЧЕНИИ.

Количество триггеров в регистрс равно коaI,HccTâó разрядов кода. Для простоты ня

С Х С M < !13 0 0 P B >I P i i Н! Е С Т И 1> Я 3 Р 51 Д и Ы и PCI i i C T P Н Я

20 тр! Пера.; 8 — -13.

Нс ieiные синхроимпульсы отр;1цaTc,ai iloI пол ipiiocTII TiocTx TIaIOT с устройства синхрони: aiiHII по шине И, четные — по ш:1не !5. Под

ИХ B03QCIICTBIICAI В КЯЖДЫИ TPIII ГСР ПОО !С25 редно заппсывастс>! код "i». l як как сипхроIIМП\ ЛЬСЫ ПОДЯIOТCЯ ЛНОО Н i ВСС НСЧЕT1ibiс,, 111ОО На ВСЕ ЧЕТНЫЕ ТРИГГСРЫ, d 1 >IЖДЫИ CIIIIXPO импульс должен записывать «1» только в один триггер (очередной), то для поочередного

30 В к л 10 ч е н i l я т p i I Г Ге р О В 11 со х р а н е 1111. к од . 1 «О >>

238909

45 в разрядах, уже участвовавших в измерении, применен включающий дешифратор на схемах совпадения, состоящих из диодов 1б — 81.

Цепочка схем совпадения разрешает или запрещает запись «1» в некоторый триггер в зависимости от состояния предыдущего и всех последующих триггеров, т. е. запись «1» разрешается, если в предыдущем триггере записана «1», а во всех последующих «0».

Это условие выполняется поочередно для каждого триггера, «Единичные» входы триггеров, для которых у.словие включения не выполняется, блокируются диодами схем совпадения. Схема совпадения диодов повторяется через каждые два триггера, кроме первого и последнего.

Сброс очередного триггера, при включении которого наступил перебаланс, производится отрицательным импульсом, подаваемым через конденсаторы 82 — 36 с последующего триггера в момент включения последнего. Упомянутый импульс проходит через выключающий дешифратор, построенный на диодах 87 — 41.

В случае перебаланса диоды закрыты (ключи открыты) сигналом со сравнивающего устройства, в случае недобаланса открыты (ключи закрыты) . Диоды 42 — 4б предотвращают прохождение положительных импульсов.

Резисторы управляемого делителя напряжения подключены к коллекторам триодов правых половин триггеров. B данном преобразователе применена звездообразная схема делителя напряжения.

Сбросовый импульс устанавливает регистр в исходное состояние — во всех разрядах записан «0». Первый нечетный синхроимпульс запишет «1» в первый разряд, так как предыдущего разряда нет, а во всех последующих записан «О» (диоды 18, 22, 25, 29, 31 закрыты). Для остальных нечетных разрядов условие включения не выполняется, в предыдущих разрядах записан «0» (диоды 20, 27 открыты) .

После включения триггера 8 созданы условия для записи «1» во второй разряд: в

30 предыдущем разряде записана «1», во всех последующих «0». Очередной (четный) синхроимпульс записывает в триггер 9 «1». В момент переключения через конденсатор 32 поступает импульс для сброса триггера 8.

Если при включении первого разряда наступил перебаланс, то диод 87 будет закрыт сигналом со сравнивающего устройства и «1» в первом разряде сбрасывается.

В результате включения триггера 9 созданы условия для включения триггера 10, который включается очередным (нечетным) синхроимпульсом и подает импульс сброса на триггер 9. Лналогично включаются все после. дующие разряды.

Последний разряд в случае перебаланса сбрасывать нет необходимости, если код снимается в последовательном виде. Код, записанный в триггерах, не изменяется от воздействия последующих синхроимпульсов.

Если код снимается в параллельном виде с триггеров регистра, то необходимо поставить аналогичную сбросовую цепочку и в последний триггер, используя для сброса импульс конца измерения с синхронизирующего устройства,. При этом подача синхроимпульсов прекращается. Следующее измерение возможно только после сброса триггеров в исходное состояние, Предмет изобретения

Лналого-цифровой преобразователь напряжения в код поразрядного кодирования, содержащий регистр, к выходам которого подключены управляемый делитель напряжения и выключающий дешифратор, подсоединенный своими входами к схеме сравнения и управляющему регистру, синхронизирующее устройство, отличающийся тем, что, с целью упрощения и повышения быстродействия устройства, он содержит включающий дешифратор, подсоединенный своим выходом ко входу регистра, а входами — к синхронизирующему устройству и регистру.

5 Ь г

Составитель М. P. Штильман

Редактор Т. 3. Орловская Техред Л, К. Малова Корректор А. А. Березуева

Заказ 1665)13 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2