Каскодный дифференциальный усилитель с управляемым усилением

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в устройствах автоматической регулировки усиления, фазовых детекторах и модуляторах, в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Управляемый усилитель является базовым узлом современных систем приема и обработки сигналов ВЧ и СВЧ-диапазонов, аналоговой вычислительной и измерительной техники. Технический результат: снижение напряжения питания, расширение функциональных возможностей усилителя, как смесителя. Каскодный дифференциальный усилитель (КДУ) с управляемым усилением содержит первый (1) и второй (2) входные транзисторы, эмиттеры которых связаны с источником опорного тока (3), первый (4) и второй (5) выходные составные транзисторы, основные эмиттеры которых (6, 7) соединены с соответствующими коллекторами первого (1) и второго (2) входных транзисторов, коллекторы - связаны цепью нагрузки (8), а базы - подключены к источнику напряжения смещения (9). В схему введен дополнительный транзистор (10), эмиттер которого соединен с дополнительным источником опорного тока (11) и через дополнительный резистор (12) связан с объединенными эмиттерами первого (1) и второго (2) входных транзисторов, база - соединена с управляющим входом (13) КДУ с управляемым усилением, причем в качестве первого (3) и второго (4) выходных составных транзисторов используются составные транзисторы с основными (6, 7) и дополнительными (14, 15) эмиттерами, которые объединены друг с другом и соединены с коллектором дополнительного транзистора (10). 4 з.п. ф-лы, 13 ил.

Реферат

Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в устройствах автоматической регулировки усиления, фазовых детекторах и модуляторах, в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Управляемый усилитель является базовым узлом современных систем приема и обработки сигналов ВЧ и СВЧ-диапазонов, аналоговой вычислительной и измерительной техники.

В современной ВЧ и СВЧ микросхемотехнике находят широкое применение каскодные дифференциальные усилители (КДУ), которые благодаря слабой внутренней обратной связи относятся к числу наиболее высокочастотных. Все известные КДУ можно разделить на два больших подкласса - классические КДУ на однотипных транзисторах [1-15], и на так называемые «перегнутые» каскоды, у которых выходные транзисторы имеют (в сравнении с входными транзисторами) другой тип проводимости [16-55].

Ближайшим прототипом (фиг.1) заявляемого устройства является КДУ, описанный в патенте фирмы General Electric (США) №3.482.177 (фиг.5). Он содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны с источником опорного тока 3, первый 4 и второй 5 выходные составные транзисторы, основные эмиттеры которых 6 и 7 соединены с соответствующими коллекторами первого 1 и второго 2 входных транзисторов, коллекторы - связаны цепью нагрузки 8, а базы -подключены к источнику напряжения смещения 9.

Следует также отметить, что в микросхемотехнике известны и другие модификации КДУ с другими вариантами построения выходных составных транзисторов 3 и 4 (патент США №5.185.582, ав. свид. СССР №1385255, патент Англии №1.520.085, кл. Н3Т.

Существенный недостаток известного КДУ состоит в том, что он не имеет специального входа «У» для электронного управления коэффициентом усиления по напряжению. Это существенно сужает область его использования, не позволяет реализовывать на его основе адаптивные функциональные узлы систем на кристалле, например СВЧ-операционные усилители, у которых петлевое усиление изменяется по заданному алгоритму в зависимости от свойств источников сигнала и цепей обратных связей (см., например, патент РФ №2307393 «Способ управления коэффициентом передачи решающего усилителя с глубокой отрицательной обратной связью»).

Основная цель предлагаемого изобретения состоит в создании условий для электронного управления коэффициентом усиления по напряжению КДУ. Реализация этой цели позволяет выполнять на базе заявляемого устройства не только широкополосные ВЧ и СВЧ-усилители с регулируемыми параметрами, но создавать на его основе более сложные функциональные узлы, например аналоговые перемножители сигналов по техпроцессу SG25H2.

Первая дополнительная цель - создание архитектуры КДУ с малым напряжением питания и электронным управлением его коэффициента усиления по напряжению, а также обеспечение возможности практической реализации устройств по технологии SG25H2 (рабочее напряжение для n-р-n транзисторов Up=1,9 В, p-n-р транзисторов Un=2,8 В).

Дополнительная цель - реализация на базе известного КДУ функции аналогового смесителя и/или аналогового перемножителя двух напряжений.

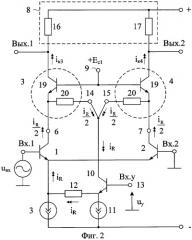

Поставленные цели достигаются тем, что в каскодном дифференциальном усилителе (фиг.2), содержащем первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны с источником опорного тока 3, первый 4 и второй 5 выходные составные транзисторы, основные эмиттеры которых 6 и 7 соединены с соответствующими коллекторами первого 1 и второго 2 входных транзисторов, коллекторы - связаны цепью нагрузки 8, а базы - подключены к источнику напряжения смещения 9, предусмотрены новые элементы и связи - в схему введен дополнительный транзистор 10, эмиттер которого соединен с дополнительным источником опорного тока 11 и через дополнительный резистор 12 связан с объединенными эмиттерами первого 1 и второго 2 входных транзисторов, база - соединена с управляющим входом 13 каскодного дифференциального усилителя с управляемым усилением, причем в качестве первого 3 и второго

4 выходных составных транзисторов используются составные транзисторы с основными 6, 7 и дополнительными 14, 15 эмиттерами, которые объединены друг с другом и соединены с коллектором дополнительного транзистора 10.

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 показано заявляемое устройство в соответствии с п.1 формулы изобретения. В данной схеме выходные составные транзисторы 4 и 5 выполнены в соответствии с п.3 формулы изобретения.

На фиг.3 так же показано заявляемое устройство в соответствии с п.1 формулы изобретения. Однако в данной схеме выходные составные транзисторы 4 и 5 выполнены в соответствии с п.2 формулы изобретения.

На фиг.4 представлены варианты построения выходных составных транзисторов 4 и 5 в соответствии с п.2 формулы изобретения.

На фиг.5 представлены варианты построения выходных составных транзисторов 4 и 5 в соответствии с п.3 формулы изобретения.

На фиг.6 показана схема заявляемого устройства в соответствии с п.4 формулы изобретения.

На фиг.7 представлена схема заявляемого устройства в соответствии с п.5 формулы изобретения.

На фиг.8 приведен пример использования заявляемого управляемого усилителя в составе аналогового перемножителя напряжений Ux и Uy.

На фиг.9 показана схема заявляемого устройства (фиг.7) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

Результаты компьютерного моделирования схемы (фиг.9) представлены на фиг.10-13:

- зависимость коэффициента усиления по напряжению Ku от частоты f при разных значениях напряжения управления Uy=+400 мВ÷-300 мВ (фиг.10);

- зависимость коэффициента усиления по напряжению Ku от напряжения на управляющем входе Uy при сопротивлении резистора R1=100 Ом (фиг.11);

- зависимость коэффициента усиления по напряжению Ku от напряжения на управляющем входе Uy при сопротивлении резистора R1=500 Ом (фиг.12);

- зависимость выходного симфазного напряжения КДУ от напряжения на направляющем входе Uy при сопротивлении резистора R1=500 Ом (фиг.13).

Каскодный дифференциальный усилитель (фиг.2) содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны с источником опорного тока 3, первый 4 и второй 5 выходные составные транзисторы, основные эмиттеры которых 6 и 7 соединены с соответствующими коллекторами первого 1 и второго 2 входных транзисторов, коллекторы - связаны цепью нагрузки 8, а базы - подключены к источнику напряжения смещения 9. В схему введен дополнительный транзистор 10, эмиттер которого соединен с дополнительным источником опорного тока 11 и через дополнительный резистор 12 связан с объединенными эмиттерами первого 1 и второго 2 входных транзисторов, база - соединена с управляющим входом 13 каскодного дифференциального усилителя с управляемым усилением, причем в качестве первого 3 и второго 4 выходных составных транзисторов используются составные транзисторы с основными 6, 7 и дополнительными 14, 15 эмиттерами, которые объединены друг с другом и соединены с коллектором дополнительного транзистора 10.

В схеме (фиг.4) в соответствии с п.2 формулы изобретения каждый первый 3 и второй 4 выходной составной транзистор содержит двухэмиттерный транзистор 18, причем первый эмиттер двухэмиттерного транзистора является основным эмиттером 6, 7 выходного составного транзистора, а второй эмиттер - дополнительным эмиттером 14 (15) выходного составного транзистора.

В схеме (фиг.5) в соответствии с п.3 формулы изобретения каждый первый 3 и второй 4 выходной составной транзистор содержит вспомогательный транзистор 19, эмиттер которого является основным эмиттером 6 (7) выходного составного транзистора, а дополнительный эмиттер 14 (15) выходного составного транзистора соединен с эмиттером вспомогательного транзистора 19 через вспомогательный резистор 20.

В схеме (фиг.6) в соответствии с п.4 формулы изобретения проводимость первого 3 и второго 4 выходных составных транзисторов противоположна проводимости первого 1 и второго 2 входных транзисторов, причем основные 6 (7) и объединенные дополнительные 14 (15) эмиттеры выходных составных транзисторов связаны соответственно с первым 21, вторым 22 и третьим 23 вспомогательными источниками опорного тока.

В схеме (фиг.7) в соответствии с п.5 формулы изобретения проводимость первого 3 и второго 4 выходных составных транзисторов противоположна проводимости первого 1 и второго 2 входных транзисторов, причем основные 6, 7 эмиттеры выходных составных транзисторов связаны соответственно с четвертым 24 и пятым 25 вспомогательными источниками опорного тока.

Рассмотрим работу заявляемого устройства (фиг.3).

В статическом режиме при нулевом напряжении управления (uy=0) ток через резистор 12 близок к нулю.

Коэффициент усиления по напряжению Ku для дифференциального выхода определяется формулой

где RH - эквивалентное сопротивление резисторов нагрузки 16 и 17;

SΣ - крутизна преобразования напряжения uвх в токи коллекторов транзисторов 3 и 4.

Причем крутизна

где φт≈26 мВ - температурный потенциал;

I3 - суммарный статистический ток эмиттерной цепи первого (1) второго (2) транзисторов (Iэ1+Iэ2=I3);

rэ1=φт/Iэ1 - дифференциальное сопротивление эмиттерного перехода i-го транзистора (i=1.2) схемы при статистическом токе эмиттера Iэi=I3/2.

Таким образом, при uy=0 для схемы (фиг.3).

Если управляющее напряжение Uy на управляющем входе 13 получает положительное () приращение, то это приводит к изменению тока iR через резистор 12:

где R12 - сопротивление резистора 12 (R12>>rэ31=rэ32).

Этот ток вызывает уменьшение тока в общей эмиттерной цепи транзисторов 1 и 2 на величину iR/2, что приводит к уменьшению коэффициента усиления по напряжению со входов «Вх.1», «Вх.2»:

При другой фазе напряжения uy коэффициент Ku увеличивается пропорционально величине Uy.

Замечательная особенность схемы (фиг.2) - подавление передачи сигнала управления uy со входа «Вх.у» на выход КДУ. Действительно, коллекторные токи транзисторов 3 и 4.

где iэ6, iэ14 - эмиттерные токи составных транзисторов по входам 6 и 14 (7 и 15).

Таким образом, ток на выходе КДУ не зависит от сигнала управления Uy. Это является необходимым условием подавления сигнала по входу 13 (uy) в смесителях напряжений Uвх и Uy.

Полученные выше аналитические соотношения подтверждаются результатами компьютерного моделирования предлагаемых схем КДУ.

Коэффициент усиления Ku по напряжению КДУ (фиг.9) изменяется (при резисторах нагрузки R4=R5=1 кОм) в диапазоне 0÷32 (фиг.11, 12). При увеличении сопротивления резистора R1 схемы (фиг.9) до 500 Ом повышается линейность характеристики управления Ku=f(Uy) и ее масштаб по оси Uy (фиг.12).

Характеристика (фиг.12) показывает, что при изменении Uy в диапазоне -1 В÷+1 В выходное синфазное напряжение Uвых.с изменяются незначительно (на 2 мВ или менее чем на 0,02%). Это свидетельствует о высоком подавлении сигнала управления Uy, который, однако, оказывает существенное влияние на коэффициент усиления Ku схемы.

На базе заявляемого КДУ (фиг.2, 3, 6, 7) могут быть созданы перемножающие ячейки, которые в отличие от хорошо известных перемножителей Джильберта, имеют более широкий частотный диапазон и меньшее напряжение питания (фиг.7, Пример построения перемножителя, в основу которого положены две идентичные схемы (фиг.2), приведен на фиг.8.

Таким образом, заявляемый комплементарный дифференциальный усилитель имеет электронное управление коэффициентами усиления. Причем сигнал управления uy, как и входной сигнал ux подаются на соответствующие входы относительно общей шины (без разделительных конденсаторов). Кроме этого, при использовании резисторов в качестве двухполюсников 21, 22, 23, 24, 25 схемы (фиг.6-7) могут иметь напряжение питания на уровне ±1,5 В, что позволяет рекомендовать их для использования в ВЧ и СВЧ интегральных микросхемах на базе техпроцесса SG25H2.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №3.660.773.

2. Патент Франции №1.484.340.

3. Патент ФРГ №1.214.775.

4. Патент Англии №1520085.

5. Патент США №3.482.177.

6. Патент Англии №1212342.

7. Патент ФРГ №1537590.

8. Патент Франции №1548008.

9. Патентная заявка ФРГ №2418455.

10. Патент Франции №2227574.

11. Ав. свид. СССР №970638.

12. Патент Швеции №359989.

13. Патент Англии №1500993.

14. Ав. свид. СССР №276170.

15. Патент Англии №1334759.

16. Патент США №6.304.143.

17. Патент США №5.418.491.

18. Патент США №4.463.319.

19. Патент США №6.717.474.

20. Патент США №6.734.720.

21. Патент США №4.723.111.

22. Патент США №4.293.824.

23. Патент США №5.323.121.

24. Патент США №5.091.701.

25. Патент США №4.406.990.

26. Патент США №5.422.600.

27. Патент США №6.788.143.

28. Патент США №4.274.061.

29. Патент США №5.327.100.

30. Патент США №5.786.729.

31. Патент США №3.644.838.

32. Патент США №4.600.893.

33. Патент США №4.390.850.

34. Патент США №6.628.168.

35. Матавкин В.В. Быстродействующие операционные усилители. М.: Радио и связь, 1989, - с.74, рис. 4.15, стр.98, рис. 6.7.

36. Патент США №6.218.900, фиг.1.

37. Патентная заявка US 2002/0196079.

38. Патент США Re 30.587.

39. Патент ЕР 1.227.580.

40. Патент США №6.714.076.

41. Патентная заявка US 2004/0090268 А1.

42. Патент США №4.959.622, фиг.1.

43. Патент США №6.018.268.

44. Патент США №5.952.882.

45. Патент США №6.580.325.

46. Патент США №6.965.266.

47. Патент США №6.867.643.

48. Патент США №6.236.270.

49. Патент США №6.229.394.

50. Патент США №5.734.296.

51. Патент США №5.477.190.

52. Патент США №6.084.475.

53. Патент США №3.733.559.

54. Патентная заявка US 2005/0001682 А1.

55. Патент США №6.300.831.

1. Каскодный дифференциальный усилитель с управляемым усилением, содержащий первый (1) и второй (2) входные транзисторы, эмиттеры которых связаны с источником опорного тока (3), первый (4) и второй (5) выходные составные транзисторы, основные эмиттеры которых (6) и (7) соединены с соответствующими коллекторами первого (1) и второго (2) входных транзисторов, коллекторы связаны цепью нагрузки (8), а базы подключены к источнику напряжения смещения (9), отличающийся тем, что в схему введен дополнительный транзистор (10), эмиттер которого соединен с дополнительным источником опорного тока (11) и через дополнительный резистор (12) связан с объединенными эмиттерами первого (1) и второго (2) входных транзисторов, база соединена с управляющим входом (13) каскодного дифференциального усилителя с управляемым усилением, причем в качестве первого (3) и второго (4) выходных составных транзисторов используются составные транзисторы с основными (6, 7) и дополнительными (14, 15) эмиттерами, которые объединены друг с другом и соединены с коллектором дополнительного транзистора (10).

2. Устройство по п.1, отличающееся тем, что каждый из первого (3) и второго (4) выходных составных транзисторов содержит двухэмиттерный транзистор (18), причем первый эмиттер двухэмиттерного транзистора является основным эмиттером (6, 7) выходного составного транзистора, а второй эмиттер - дополнительным эмиттером (14, 15) выходного составного транзистора.

3. Устройство п.1, отличающееся тем, что каждый из первого (3) и второго (4) выходных составных транзисторов содержит вспомогательный транзистор (19), эмиттер которого является основным эмиттером (6, 7) выходного составного транзистора, а дополнительный эмиттер (14, 15) выходного составного транзистора соединен с эмиттером вспомогательного транзистора (19) через вспомогательный резистор (20).

4. Устройство по п.1 или 2, отличающееся тем, что проводимость первого (3) и второго (4) выходных составных транзисторов противоположна проводимости первого (1) и второго (2) входных транзисторов, причем основные (6, 7) и объединенные дополнительные (14, 15) эмиттеры выходных составных транзисторов связаны соответственно с первым (21), вторым (22) и третьим (23) вспомогательными источниками опорного тока.

5. Устройство по п.1 или 3, отличающееся тем, что проводимость первого (3) и второго (4) выходных составных транзисторов противоположна проводимости первого (1) и второго (2) входных транзисторов, причем основные (6, 7) эмиттеры выходных составных транзисторов связаны соответственно с четвертым (24) и пятым (25) вспомогательными источниками опорного тока.