Адаптивное цифровое свертывающее устройство

Иллюстрации

Показать всеИзобретение относится к области радиотехники и предназначено для цифровой свертки сигналов во временной области. Использование - в комплексах скрытной радиолокации, в радиолокационных системах с разнесенными приемными и передающими позициями и в других областях. Достигаемым техническим результатом изобретения является расширение функциональных возможностей за счет адаптации к изменению параметров и вида модуляции сигналов опорного передатчика. Указанный результат достигается за счет того, что устройство содержит запоминающее устройство (ЗУ) входного сигнала, вход которого является входом устройства, блок умножения, входы которого соединены с выходами ЗУ входного сигнала, сумматор, входы которого соединены с выходами блока умножения, блок адаптации и ЗУ прямого сигнала, при этом вход блока адаптации является вторым входом устройства, первый выход соединен со вторым входом ЗУ входного сигнала, второй выход соединен с первым входом ЗУ прямого сигнала, третий выход соединен с вторым входом ЗУ прямого сигнала, выходы ЗУ прямого сигнала соединены со вторыми входами блока умножения. 2 ил.

Реферат

Изобретение относится к области радиотехники и предназначено для цифровой свертки сигналов во временной области. Оно может использоваться в комплексах скрытной радиолокации, в радиолокационных системах с разнесенными приемными и передающими позициями и в других областях.

Из [1], с.126 рис.2.18 известно цифровое устройство, предназначенное для выполнения операции свертки радиолокационных сигналов во временной области. Оно содержит ЗУ входного сигнала, представляющее собой блок регистров сдвига, ЗУ импульсной характеристики, представляющее собой блок ПЗУ, и параллельный сумматор. Выполнение операции свертки происходит следующим образом. С одинаковых по номеру разрядов всех регистров сдвига код величины принятого сигнала подается на адресные входы своего ПЗУ. По адресу, соответствующему коду величины сигнала, в ПЗУ записан код результата перемножения коэффициентов импульсной характеристики на величину принятого сигнала. Со всех ПЗУ коды результатов перемножения поступают на параллельный сумматор, на выходе которого в каждом периоде дискретизации получается результат свертки.

Недостатком устройства является невозможность применения его для обработки сигналов с неизвестными параметрами модуляции, что обуславливается жесткой прошивкой кодов результата перемножения коэффициентов импульсной характеристики на величину принятого сигнала в ПЗУ.

Из известных свертывающих устройств наиболее близким по технической сущности к заявленному является цифровое свертывающее устройство, описанное в [2] на с.41 рис.1.6. В его состав входят запоминающее устройство (ЗУ) 1 входного сигнала, блок 2 умножения, сумматор 3, ЗУ 4 импульсной характеристики.

Устройство работает следующим образом. Цифровой код дискретизированного и квантованного принятого сигнала поступает на ЗУ 1 входного сигнала. В ЗУ 4 импульсной характеристики хранятся коды коэффициентов импульсной характеристики. С одинаковых по номеру выходов ЗУ 1 входного сигнала и ЗУ 4 импульсной характеристики поступают цифровые коды принятого сигнала на первые входы умножителей блока 2 умножения и цифровые коды коэффициентов импульсной характеристики на вторые входы умножителей блока 2 умножения. С выходов блока 2 умножения коды результатов перемножения поступают на входы сумматора 3. На выходе сумматора 3 формируется код результата свертки для данного периода дискретизации.

Недостатком устройства является невозможность применения его для обработки сигналов с неизвестными параметрами модуляции из-за отсутствия внешнего управления ЗУ 4 импульсной характеристики.

Полезными сигналами, поступающими на входы приемников в комплексах скрытной радиолокации, являются сигналы, отраженные от воздушных целей, облученных опорными импульсными передатчиками, и прямые сигналы этих передатчиков. Опорными могут быть передатчики РЛС авиационных комплексов ДРЛО или другие передатчики.

Целью изобретения является расширение функциональных возможностей цифрового свертывающего устройства за счет адаптации к изменению параметров и вида модуляции сигналов опорного передатчика.

Поставленная цель достигается тем, что в известное устройство, содержащее ЗУ 1 кодов принятых отраженных сигналов (КПОС), вход которого является входом устройства, блок 2 умножения, входы которого соединены с выходами ЗУ 1 КПОС, и сумматор 3, входы которого соединены с выходами блока 2 умножения, вводятся блок 5 адаптации и ЗУ 4 кодов сигнала опорного передатчика (КСОП). Вход блока 5 адаптации является вторым входом устройства, первый выход соединен со вторым входом ЗУ 1 КПОС, второй выход соединен с первым входом ЗУ 4 КСОП, третий выход соединен со вторым входом ЗУ 4 КСОП. Выходы ЗУ 4 КСОП соединены со вторыми входами блока 2 умножения.

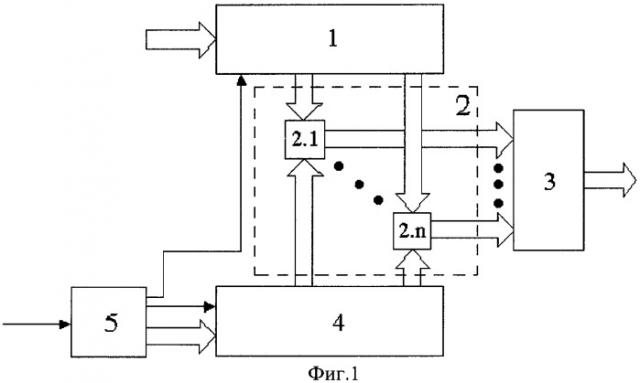

На фигуре 1 изображена структурная схема адаптивного цифрового свертывающего устройства.

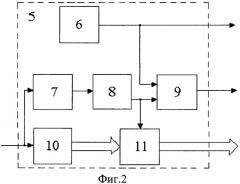

На фигуре 2 изображена структурная схема блока 5 адаптации.

Адаптивное цифровое свертывающее устройство содержит (см. фиг.1) ЗУ 1 КПОС, блок 2 умножения, сумматор 3, ЗУ 4 КСОП, блок 5 адаптации.

ЗУ 1 КПОС представляет собой блок регистров сдвига и содержит m регистров сдвига с последовательным вводом и параллельным выводом информации. Каждый регистр должен содержать n разрядов. Количество каналов m равно числу разрядов кода принятого сигнала, количество разрядов регистра n определяется частотой дискретизации принятого сигнала. Такой регистр сдвига может быть выполнен, например, на последовательных регистрах сдвига типа ИР31, принцип работы которых описан в [3], с.214.

Блок 2 умножения состоит из n умножителей. Каждый умножитель перемножает два m-разрядных числа. Умножители могут быть выполнены, например, на АЛУ с умножением типа ИК2, принцип работы которого описан в [3], с.276.

Сумматор 3 представляет собой параллельный сумматор на n входов, который может быть выполнен, например, на полном двоичном сумматоре типа ИМ6, принцип работы которого описан в [3], с.254.

ЗУ 4 КСОП имеет такую же структуру, как и ЗУ 1 КПОС.

Блок 5 адаптации содержит (см. фиг.2) генератор 6 тактовых импульсов, амплитудный детектор 7, пороговый компаратор 8, временной селектор 9, аналого-цифровой преобразователь (АЦП) 10, коммутирующее устройство 11.

Генератор 6 тактовых импульсов представляет собой генератор, формирующий импульсы с заданной частотой дискретизации принятого отраженного и опорного сигналов, и может быть выполнен, например, по схеме, описанной в [5], с.133.

Пороговый компаратор 8 может быть типа К521СА1, принцип работы которого описан в [4], с.86.

Временной селектор 9 представляет собой элемент И на два входа и может быть выполнен, например, на элементе типа ЛИ5, принцип работы которого описан в [3], с.47.

АЦП 10 представляет собой m-разрядный аналогово-цифровой преобразователь и может быть выполнен, например, на микросхеме типа К572ПВ1А, принцип работы которой описан в [4], с.115.

Коммутирующее устройство 11 может быть выполнено, например, на микросхемах КР1561ЛИ2, принцип работы которых описан в [6], с.52, причем количество задействованных элементов 2И будет равно количеству разрядов m АЦП 10.

Существенными признаками адаптивного цифрового свертывающего устройства являются входами устройства служат первые входы ЗУ 1 КПОС и вход блока 5 адаптации. Выходы разрядов регистров сдвига ЗУ 1 КПОС соединены с первыми входами соответствующих умножителей 2.1...2.п блока 2 умножения. Первый выход блока 5 адаптации соединен со вторым входом ЗУ 1 КПОС. Второй выход блока 5 адаптации соединен с первым входом ЗУ 4 КСОП. Третий выход блока 5 адаптации соединен со вторым входом ЗУ 4 КСОП. Выходы разрядов регистров сдвига ЗУ 4 КСОП соединены со вторыми входами соответствующих умножителей 2.1…2.n блока 2 умножения, выходы которых являются выходами блока 2 умножения. Выходы блока 2 умножения соединены с входами сумматора 3. Выход сумматора 3 является выходом устройства.

Элементы блока 5 адаптации соединены следующим образом: входом блока является вход АЦП 10 и соединенный с ним вход амплитудного детектора 7, выход которого соединен с входом порогового компаратора 8. Выход порогового компаратора 8 соединен со вторым входом временного селектора 9 и вторыми входами коммутирующего устройства 11. Выход генератора 6 тактовых импульсов является первым выходом блока 5 адаптации и соединен с первым входом временного селектора 9. Выход временного селектора 9 является вторым выходом блока 5 адаптации. Выход АЦП 10 соединен с первыми входами коммутирующего устройства 11. Выход коммутирующего устройства 11 является третьим выходом блока 5 адаптации.

Принцип работы адаптивного цифрового свертывающего устройства заключается в том, что ЗУ 4 КСОП заполняется во время приема прямого сигнала опорного передатчика. Записанные в него коды используются как коэффициенты импульсной характеристики для свертки отраженных от целей сигналов до прихода следующего прямого сигнала.

Адаптивное цифровое свертывающее устройство работает следующим образом. Коды отраженных от целей сигналов поступают на первый вход ЗУ 1 КПОС. С первого выхода блока 5 адаптации на второй вход ЗУ 1 КПОС непрерывно поступают тактовые импульсы с заданным периодом дискретизации. Эти импульсы обеспечивают сдвиг (продвижение) кодов принятых отраженных сигналов в регистрах сдвига ЗУ 1 КПОС.

Прямой сигнал опорного передатчика поступает на вход блока 5 адаптации. На втором выходе блока 5 адаптации тактовые импульсы появляются только во время действия прямого сигнала. Они поступают на первый вход ЗУ 4 КСОП и обеспечивают сдвиг кодов прямого сигнала, которые появляются на третьем выходе блока 5 адаптации и поступают на второй вход ЗУ 4 КСОП также во время действия прямого сигнала. После окончания прямого сигнала ЗУ 4 КСОП оказывается заполненным и до прихода следующего прямого сигнала его содержимое не изменяется.

С выходов одинаковых по номеру разрядов ЗУ 1 КПОС и ЗУ 4 КСОП цифровые коды поступают соответственно на первые и вторые входы умножителей блока 2 умножения, где происходит их перемножение. С выходов умножителей блока 2 умножения коды результатов перемножения поступают на входы сумматора 3, где происходит их сложение. На выходе сумматора 3 формируется код суммы, который является кодом результата свертки в каждом периоде дискретизации.

Блок 5 адаптации работает следующим образом. Тактовые импульсы с генератора 6 тактовых импульсов непрерывно поступают на первый выход блока 5 адаптации и на первый вход временного селектора 9. Прямой сигнал опорного передатчика поступает на АЦП 10 и на амплитудный детектор 7. На выходе АЦП 10 формируется код сигнала опорного передатчика, который является кодом коэффициентов импульсной характеристики. Этот код поступает на коммутирующее устройство 11. Амплитудный детектор 7 выделяет огибающую импульса сигнала опорного передатчика. Выделенная огибающая поступает на пороговый компаратор 8, где сравнивается с заданным порогом. При превышении огибающей порога, а это произойдет при приеме мощного прямого сигнала опорного передатчика, на выходе порогового компаратора 8 будет сформирован прямоугольный импульс, длительность которого равна длительности импульса прямого сигнала опорного передатчика. Этот импульс поступает на второй вход временного селектора 9, разрешая прохождение тактовых импульсов с генератора 6 тактовых импульсов на выход временного селектора 9, являющийся вторым выходом блока 5 адаптации, и на вторые входы коммутирующего устройства 11, открывая его. В течение длительности импульса код прямого сигнала поступает на выход коммутирующего устройства 11, являющийся третьим выходом блока 5 адаптации. После окончания импульса прямого сигнала на выходе порогового компаратора 8 появится уровень логического нуля, который запретит прохождение тактовых импульсов на второй выход блока 5 адаптации и кодов прямого сигнала на третий выход блока 5 адаптации.

В следующем периоде излучения опорного передатчика сразу после поступления первого прямого сигнала опорного передатчика блок 5 адаптации заполнит ЗУ 4 КСОП кодами, соответствующими новому импульсу прямого сигнала, чем обеспечит адаптацию цифрового свертывающего устройства к изменению вида прямого сигнала или параметров его внутриимпульсной модуляции и оптимальную обработку (свертку) отраженных от целей сигналов.

Таким образом, введение новых элементов и новых связей в предлагаемое устройство позволяет расширить функциональные возможности цифрового свертывающего устройства за счет адаптации к изменению параметров и вида модуляции сигналов опорного передатчика.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Лихарев В.А. Цифровые методы и устройства в радиолокации. - М.: Сов.радио, 1973.

2. Кузьмин С.З. Основы проектирования систем цифровой обработки радиолокационной информации. - М.: Радио и связь, 1986.

3. Цифровые интегральные микросхемы: Справочник / М.И.Богданович, И.Н.Грель, В.А.Прохоренко, В.В.Шалимо. - Мн.: Беларусь, 1991.

4. 180 аналоговых микросхем (справочник). Ю.А.Мячин. - Изд. «Патриот», МП «Символ-Р» и редакция журнала «Радио», 1993.

5. 750 практических электронных схем: Справочное руководство. Пер. с англ. / Сост.и ред. Р.Фелпс.- М.: Мир, 1986.

6. Микросхемы интегральные серии КС1543…КР1561. - СПб.: Издательство «Электростандарт», 1993.

Адаптивное цифровое свертывающее устройство, содержащее запоминающее устройство (ЗУ) кодов принятых отраженных сигналов, вход которого является входом устройства, блок умножения, входы которого соединены с выходами ЗУ кодов принятых отраженных сигналов, сумматор, входы которого соединены с выходами блока умножения, а выход является выходом устройства, отличающееся тем, что в него введены блок адаптации, вход которого является вторым входом устройства, первый выход соединен со вторым входом ЗУ кодов принятых отраженных сигналов, и ЗУ кодов сигнала опорного передатчика, первый вход которого соединен со вторым выходом блока адаптации, второй вход соединен с третьим выходом блока адаптации, а выходы ЗУ кодов сигнала опорного передатчика соединены со вторыми входами блока умножения, при этом на выходе сумматора формируется код результата свертки сигналов в каждом периоде дискретизации, а блок адаптации обеспечивает подстройку устройства к изменению вида опорного сигнала передатчика или параметров его внутриимпульсной модуляции и содержит генератор тактовых импульсов (ГТИ), амплитудный детектор, пороговый компаратор, временной селектор, аналого-цифровой преобразователь (АЦП), коммутирующее устройство, при этом вход АЦП и соединенный с ним вход амплитудного детектора являются входом сигнала опорного передатчика и вторым входом устройства, выход амплитудного детектора соединен с входом порогового компаратора, выход которого соединен со вторым входом временного селектора и вторым входом коммутирующего устройства, выход ГТИ является первым выходом блока адаптации и, кроме того, соединен с первым входом временного селектора, выход которого является вторым выходом блока адаптации, выходы АЦП соединены с первыми входами коммутирующего устройства, выходы которого являются третьим выходом блока адаптации.