Аналоговый квадратор напряжения

Иллюстрации

Показать всеИзобретение относится к измерительной технике, системам связи и радионавигации. Технический результат: расширение функциональной возможности при снижении погрешности. Аналоговый квадратор напряжения (АКН) содержит первый (1) входной транзистор, эмиттер которого соединен с эмиттером второго (2) входного транзистора, первый (3) вход АКН, связанный с входом первого (4) повторителя напряжения, третий (5) входной транзистор, эмиттер которого соединен с эмиттером четвертого (6) входного транзистора, второй (7) вход АКН, связанный с входом второго (8) повторителя напряжения, первую цепь нагрузки (9), связанную с коллектором третьего (5) входного транзистора и первым (10) выходом АКН, вторую (11) цепь нагрузки, связанную с коллектором второго (2) входного транзистора и вторым (12) выходом АКН, причем база четвертого (6) входного транзистора связана с выходом первого (4) повторителя напряжения, а база второго (2) входного транзистора соединена с выходом второго (8) повторителя напряжения. Коллектор первого (1) входного транзистора соединен с коллектором третьего (5) входного транзистора, первый (3) вход АКН связан с базой первого (1) входного транзистора, второй (7) вход АКН связан с базой третьего (5) входного транзистора. 4 з.п. ф-лы, 24 ил.

Реферат

В современной измерительной технике, системах связи и радионавигации находят применение так называемые квадраторы входных сигналов. Они используются, например, в системах сотовой связи для удвоения частоты входного сигнала. Проектирование квадраторов относится к числу одной из задач аналоговой микросхемотехники [1].

В современной радиоэлектронной аппаратуре широко используются дифференциальные входные каскады (ДК) класса АВ, которые обеспечивают высокое быстродействие операционных усилителей с непосредственной связью [2, 3]. Различные модификации таких ДК защищены патентам ведущих микроэлектронных фирм мира [4-21]. Однако авторам неизвестны способы построения на базе ДК класса АВ квадраторов напряжений, т.е. устройств, обеспечивающих возведение в квадрат входного напряжения их или увеличения его частоты fx в два раза.

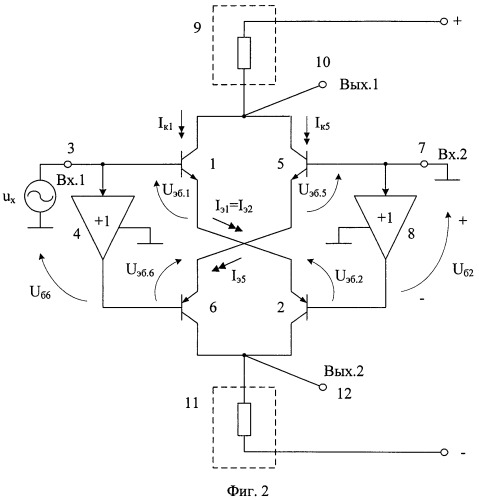

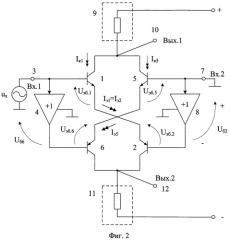

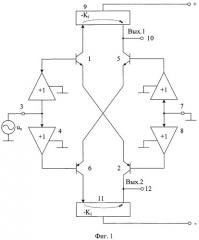

Ближайшим прототипом заявляемого устройства является дифференциальный каскад (фиг.1) в структуре операционного усилителя по патенту США №5.150.074. Он содержит первый 1 входной транзистор, эмиттер которого соединен с эмиттером второго 2 входного транзистора, первый 3 вход квадратора, связанный со входом первого 4 повторителя напряжения, третий 5 входной транзистор, эмиттер которого соединен с эмиттером четвертого 6 входного транзистора, второй 7 вход квадратора, связанный со входом второго 8 повторителя напряжения, первую цепь нагрузки 9, связанную с коллектором третьего 5 входного транзистора и первым 10 выходом квадратора, вторую 11 цепь нагрузки, связанную с коллектором второго 2 входного транзистора и вторым 12 выходом квадратора, причем база четвертого 6 входного транзистора связана с выходом первого 4 повторителя напряжения, а база второго 2 входного транзистора соединена с выходом второго 8 повторителя напряжения.

Существенный недостаток известного устройства состоит в том, что оно не обеспечивает выходное напряжение, пропорциональное квадратору входного напряжения.

Основная цель предлагаемого изобретения состоит в расширении функциональных возможностей известного дифференциального каскада - реализации на его основе нелинейного функционального узла - широкополосного квадратора входных напряжений.

Поставленная цель достигается тем, что в дифференциальном каскаде фиг.1, содержащем первый 1 входной транзистор, эмиттер которого соединен с эмиттером второго 2 входного транзистора, первый 3 вход квадратора, связанный со входом первого 4 повторителя напряжения, третий 5 входной транзистор, эмиттер которого соединен с эмиттером четвертого 6 входного транзистора, второй 7 вход квадратора, связанный со входом второго 8 повторителя напряжения, первую цепь нагрузки 9, связанную с коллектором третьего 5 входного транзистора и первым 10 выходом квадратора, вторую 11 цепь нагрузки, связанную с коллектором второго 2 входного транзистора и вторым 12 выходом квадратора, причем база четвертого 6 входного транзистора связана с выходом первого 4 повторителя напряжения, а база второго 2 входного транзистора соединена с выходом второго 8 повторителя напряжения, предусмотрены новые элементы и связи - коллектор первого 1 входного транзистора соединен с коллектором третьего 5 входного транзистора, первый 3 вход квадратора связан с базой первого 1 входного транзистора, второй 7 вход квадратора связан с базой третьего 5 входного транзистора.

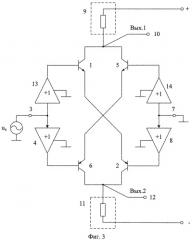

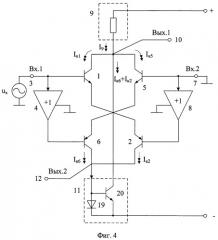

На фиг.1 показана схема аналогового квадратора - прототипа, а на фиг.2 приведена схема заявляемого устройства в соответствии с п.1 или п.2 формулы изобретения. На фиг.3 приведена схема заявляемого устройства в соответствии с п.3, а на фиг.4 и фиг.5 - в соответствии с п.4 и п.5 формулы изобретения.

На фиг.6 показан частный вариант построения повторителей напряжения 4, 8 в заявляемом АК фиг.2, фиг.4, фиг.5.

Пример выполнения токового зеркала на фиг.4 и фиг.5 приведен на фиг.7.

Повторители напряжений 13 и 14 в АК фиг.3 могут выполняться в соответствии с фиг.8, а повторители 4, 8 - в соответствии с фиг.9.

На фиг.10 и фиг.11 показаны частные случаи выполнения неинвертирующего повторителя тока 9 в схеме фиг.5.

На фиг.12 представлена в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» схема АК фиг.2 при выполнении повторителей напряжения 4 и 8 в соответствии с фиг.6. Результаты ее компьютерного моделирования приведены на фиг.13-фиг.16.

На фиг.17 представлена в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» схема АК фиг.4 при выполнении повторителей напряжения 4 и 8 в соответствии с фиг.6. Результаты ее компьютерного моделирования приведены на фиг.18-21.

На фиг.22 представлена в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» схема АК фиг.5 при выполнении повторителей напряжения 4 и 8 в соответствии с фиг.6. Результаты ее компьютерного моделирования приведены на фиг.23-24.

Заявляемый аналоговый квадратор фиг.2 содержит первый 1 входной транзистор, эмиттер которого соединен с эмиттером второго 2 входного транзистора, первый 3 вход квадратора, связанный со входом первого 4 повторителя напряжения, третий 5 входной транзистор, эмиттер которого соединен с эмиттером четвертого 6 входного транзистора, второй 7 вход квадратора, связанный со входом второго 8 повторителя напряжения, первую цепь нагрузки 9, связанную с коллектором третьего 5 входного транзистора и первым 10 выходом квадратора, вторую 11 цепь нагрузки, связанную с коллектором второго 2 входного транзистора, и вторым 12 выходом квадратора, причем база четвертого 6 входного транзистора связана с выходом первого 4 повторителя напряжения, а база второго 2 входного транзистора соединена с выходом второго 8 повторителя напряжения. Коллектор первого 1 входного транзистора соединен с коллектором третьего 5 входного транзистора, первый 3 вход квадратора связан с базой первого 1 входного транзистора, второй 7 вход квадратора связан с базой третьего 5 входного транзистора.

В схеме фиг.2 в соответствии с п.2 формулы изобретения коллектор четвертого 6 входного транзистора соединен с коллектором второго 2 входного транзистора.

В схеме фиг.3 в соответствии с п.3 формулы изобретения первый 3 вход квадратора связан с базой первого 1 входного транзистора через первый 13 дополнительный повторитель напряжения, а второй 7 вход квадратора соединен с базой третьего 5 входного транзистора через второй дополнительный 14 повторитель напряжения.

В схеме фиг.4 в соответствии с п.4 формулы изобретения в качестве второй 11 цепи нагрузки используется входная цепь первого дополнительного инвертирующего токового зеркала, выход которого соединен с объединенными коллекторами первого 1 и третьего 5 входных транзисторов.

В схеме фиг.5 в соответствии с п.5 формулы изобретения в качестве второй 11 цепи нагрузки используется входная цепь второго дополнительного инвертирующего токового зеркала, а в качестве первой 9 цепи нагрузки используется входная цепь первого неинвертирующего повторителя тока, причем выходы дополнительного инвертирующего токового зеркала и первого неинвертирующего повторителя тока соединены друг с другом и подключены к третьей цепи нагрузки 15, согласованной с общей шиной источников питания.

На фиг.6 показан частный вариант построения повторителей напряжения 4, 8 в заявляемом АК фиг.2, фиг.4, фиг.5. Схема фиг.6 содержит транзистор 16, р-n переход 17 и токостабилизирующий двухполюсник 18.

Пример выполнения токового зеркала на фиг.4 и фиг.5 приведен на фиг.7. Эта схема содержит транзистор 20 и р-n переход 19.

Повторители напряжений 13 и 14 в АК фиг.3 могут выполняться в соответствии с фиг.8, а повторители 4, 8 - в соответствии с фиг.9. Эти функциональные узлы реализованы на транзисторе 21 и двухполюснике 22 (фиг.8), а также транзисторе 23 и двухполюснике 24 (фиг.9).

На фиг.10 и фиг.11 показаны частные случаи выполнения неинвертирующего повторителя тока 9 в схеме фиг.5. Подсхема фиг.10 реализована на транзисторах 25, 26, 27 и двухполюснике 28, а подсхема на фиг.11 содержит транзистор 29 и двухполюсник 30.

На фиг.12 представлена в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» схема АК фиг.2 при выполнении повторителей напряжения 4 и 8 в соответствии с фиг.6. Результаты ее компьютерного моделирования приведены на фиг.13-16:

- зависимость модуля дифференциального коэффициента усиления по напряжению Ku от постоянного напряжения Uy на входе 7 АК при МО МГц (фиг.13);

- зависимость напряжения на выходе Out.2 (12) от ux при различных напряжениях на входе 7 (Uy) (фиг.14);

- спектр частот выходного сигнала Вых.1 при ux=50 мВ и fx=10 МГц, Uy=0 (фиг.15);

- ошибка квадрирования (%) и проходные характеристики заявляемого и идеального квадраторов напряжения ux при Uy=0 (фиг.16).

На фиг.17 представлена в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» схема АК фиг.4 при выполнении повторителей напряжения 4 и 8 в соответствии с фиг.6. Результаты ее компьютерного моделирования приведены на фиг.18-фиг.21:

- зависимость модуля дифференциального коэффициента усиления по напряжению Кu от постоянного напряжения Uy на входе 7 АК при f=10 МГц (фиг.18);

- зависимость напряжения на выходе Out.2 (12) от ux при различных напряжениях на входе 7 (Uy) (фиг.19);

- относительная погрешность возведения в квадрат напряжения ux в зависимости от напряжения Uy (фиг.20);

- спектр частот выходного сигнала Вых.1 при ux=50 мВ и fx=10 МГц, Uy=0(фиг.21).

На фиг.22 представлена в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НИИ «Пульсар» схема АК фиг.5 при выполнении повторителей напряжения 4 и 8 в соответствии с фиг.6. Результаты ее компьютерного моделирования приведены на фиг.23-24:

- зависимость напряжения на выходе Out.l (10) от ux при различных напряжениях на входе 7 (Uy) (фиг.23);

- спектр частот выходного сигнала Вых.1 при ux=50 мВ и fx=10 МГц, Uy=0 (фиг.24).

Рассмотрим работу заявляемого аналогового квадратора фиг.2.

На основании второго закона Кирхгофа при ux=0 можно записать следующие уравнения для входных цепей АК фиг.2:

где Uб6, Uб2 - статические напряжения на базах транзисторов 6 и 2;

Uэб.i - напряжение эмиттер-база i-гo транзистора.

В статическом режиме (ux=0) при идентичных р-n-переходах за счет схемотехники повторителей 4 и 8 обеспечивается равенство

где - напряжение эмиттер-база транзисторов при Iэ=Iэ.р,

Iэ.р - статический ток эмиттера.

При произвольном токе эмиттера Iэi≠Iэ.р напряжение на эмиттерном переходе отличается от :

Если на вход 3 подается небольшое напряжение ux<φт, то из уравнений (1), (2), (3), (4) можно получить следующие зависимости

Таким образом, при ux>0 ток коллектора транзистора 1 возрастает по экспоненте, а ток коллектора транзистора 5 уменьшается по экспоненте относительно статического значения Iэ.р. В результате ток в цепи нагрузки 9 является суммой двух экспонент:

где Iк1 - коллекторный ток транзистора 1;

Iк5 - коллекторный ток транзистора 5.

Функцию 7 можно разложить в ряд Тейлора в окрестностях точки статического режима Iэ.р:

где

- поправочный коэффициент, учитывающий погрешность квадрирования Δ;

При 0≤x≤1 максимальная погрешность квадрирования не превышает величины, соответствующей x=1:

Если x≤0,5, то погрешность возведения в квадрат, которую обеспечивает заявляемое устройство, Δ<0,01 (или 1%).

Таким образом, ток в цепях нагрузки 9 и 11 содержит составляющую, пропорциональную квадрату входного напряжения ux. Следовательно, заявляемое устройство выполняет функцию преобразователя ux в выходное напряжение, пропорциональное . Это позволяет использовать АК в качестве удвоителя частоты ωx=2πfx. Действительно, при синусоидальном входном сигнале ux=Uxsinωx переменный выходной сигнал uвых не содержит (в идеальном случае) первой гармоники их и имеет удвоенную частоту 2ωx:

где K1 - коэффициент пропорциональности.

Данный вывод подтверждается результатами компьютерного моделирования (фиг.15, фиг.21, фиг.24).

При выполнении АК по схеме фиг.4 увеличивается коэффициент пропорциональности K1 в формуле (1).

Схемотехническое решение фиг.5 позволяет получить напряжение в нагрузке 15 (Rн), «привязанной» к общей шине источников питания. Это создает существенное преимущество схемы фиг.5 по сравнению с фиг.2 и фиг.4.

Таким образом, за счет введения новых элементов и связей между ними заявляемое устройство выполняет функцию квадратора входных сигналов.

Библиографический список

1. Савченко Е.М. Широкополосный интегральный СВЧ-удвоитель частоты [Текст] /Е.М.Савченко. // Проблемы разработки перспективных микро- и наноэлектронных систем - 2008. Сборник научных трудов III Всероссийской научно-технической конференции. / Под общ. ред. Академика РАН А.Л.Стемпковского. - М.: Институт проблем проектирования в микроэлектронике РАН, 2008. - С.297-300.

2. Операционные усилители с непосредственной связью каскадов. / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л., 1979. - 148 с.

3. Архитектура и схемотехника быстродействующих операционных усилителей [Текст] / Прокопенко Н.Н., Будяков А.С. // Монография / ЮРГУЭС. - Шахты: ЮРГУЭС, 2006. - 231 с.

4. Патент США №6.281.752

5. Патент США №6.437.645

6. Патент США №6.249.153

7. Патент США №5.343.164

8. Патент США №3.668.538

9. Патент США №5.150.074

10. Патент США №5.399.991

11. Патент США №5.512.859

12. Патент США №5.907.262 fig.4

13. Патент США №6.468.736

14. Патент США №6.351.186

15. Патент США №6.259.280

16. Патент США №6.435.645

17. Патентная заявка США №2007/0216483

18. Патент США №5.122.759

19. Патент США №5.343.164

20. Патент США №4.797.629 fig.3

21. Патент США №4.757.273

1. Аналоговый квадратор напряжения, содержащий первый (1) входной транзистор, эмиттер которого соединен с эмиттером второго (2) входного транзистора, первый (3) вход квадратора, связанный со входом первого (4) повторителя напряжения, третий (5) входной транзистор, эмиттер которого соединен с эмиттером четвертого (6) входного транзистора, второй (7) вход квадратора, связанный со входом второго (8) повторителя напряжения, первую цепь нагрузки (9), связанную с коллектором третьего (5) входного транзистора и первым (10) выходом квадратора, вторую (11) цепь нагрузки, связанную с коллектором второго (2) входного транзистора и вторым (12) выходом квадратора, причем база четвертого (6) входного транзистора связана с выходом первого (4) повторителя напряжения, а база второго (2) входного транзистора соединена с выходом второго (8) повторителя напряжения, отличающийся тем, что коллектор первого (1) входного транзистора соединен с коллектором третьего (5) входного транзистора, первый (3) вход квадратора связан с базой первого (1) входного транзистора, второй (7) вход квадратора связан с базой третьего (5) входного транзистора.

2. Устройство по п.1, отличающееся тем, что коллектор четвертого (6) входного транзистора соединен с коллектором второго (2) входного транзистора.

3. Устройство по п.1, отличающееся тем, что первый (3) вход квадратора связан с базой первого (1) входного транзистора через первый (13) дополнительный повторитель напряжения, а второй (7) вход квадратора соединен с базой третьего (5) входного транзистора через второй дополнительный (14) повторитель напряжения.

4. Устройство по п.2, отличающееся тем, что в качестве второй (11) цепи нагрузки используется входная цепь первого дополнительного инвертирующего токового зеркала, выход которого соединен с объединенными коллекторами первого (1) и третьего (5) входных транзисторов.

5. Устройство по п.2, отличающееся тем, что в качестве второй (11) цепи нагрузки используется входная цепь второго дополнительного инвертирующего токового зеркала, а в качестве первой (9) цепи нагрузки используется входная цепь первого неинвертирующего повторителя тока, причем выходы дополнительного инвертирующего токового зеркала и первого неинвертирующего повторителя тока соединены друг с другом и подключены к третьей цепи нагрузки (15), согласованной с общей шиной источников питания.