Индикатор изменений для уменьшения потребления энергии при неудачных обращениях к кэш-памяти

Иллюстрации

Показать всеИзобретение относится к процессорам, в частности к способу уменьшения потребления энергии при кэшировании данных с отложенной записью путем проверки модифицируемого бита (GMI), указывающего, содержит ли какой-либо из элементов кэш-памяти с отложенной записью измененные данные. Техническим результатом является повышение производительности процессора и снижение потребляемой энергии. Процессор включает в себя кэш-память, имеющую по меньшей мере один элемент, управляемый по алгоритму отложенной записи. При кэш-промахе, если GMI показывает, что ни один из элементов кэш-памяти с отложенной записью в данной кэш-памяти не содержит измененных данных, данные, извлеченные из памяти записываются в выбранный элемент без предварительного считывания данного элемента. В кэш-памяти, разделенной на банки, два или более GMI банка могут быть ассоциированы с двумя или более банками. При n-мерном наборе ассоциированных кэш-памятей n GMI наборов можно ассоциировать с данными n наборами. 3 н. и 7 з.п. ф-лы, 2 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение в целом относится к области процессоров, в частности к способу уменьшения потребления энергии при кэшировании данных с отложенной записью путем проверки глобального индикатора изменений.

Микропроцессоры выполняют вычислительные задачи в широком спектре прикладных систем, включая встроенные прикладные системы, подобные переносным электронным устройствам. Постоянно увеличивающийся набор свойств и повышенная функциональность подобных устройств требует все более мощных в вычислительном отношении процессоров для предоставления дополнительной функциональности посредством программного обеспечения. Другой тенденцией переносных электронных устройств являются постоянно сокращающиеся конструктивные параметры. Последствием этой тенденции является уменьшение размера батарей, используемых для питания процессора и другой электроники в устройстве, делая коэффициент полезного действия главной задачей конструирования. Следовательно, для процессоров переносных электронных устройств желательны усовершенствования процессоров, которые увеличивают быстродействие и понижают потребление энергии.

Многие программы написаны так, словно исполняющий их компьютер имеет очень большой (идеально, неограниченный) объем быстрой памяти. Большинство современных процессоров эмулируют данные идеальные условия путем применения иерархии типов памяти, каждый из которых имеет различные скоростные и ценовые характеристики. Типы памяти в данной иерархии обычно меняются от очень быстрых и очень дорогих наверху, до все более медленных, но более экономичных видов хранения на нижних уровнях. Вследствие характеристик пространственного и временного местоположения большинства программ, команды и данные, исполняемые в любое данное время, могут статистически потребоваться в самом недалеком будущем, и могут успешно храниться в верхних, высокоскоростных уровнях, где они более доступны. По мере развития и/или ветвления кода в новые области, необходимые команды и данные можно загрузить из нижних иерархических уровней памяти в верхние уровни. Несмотря на то, что данное перемещение команд и данных между иерархическими уровнями памяти вызывает некоторое снижение производительности и может требовать сложного программного и аппаратного управления, общим результатом является чистый прирост в быстродействии памяти над использованием только медленных типов памяти, при значительном снижении затрат по сравнению с использованием только быстрых типов памяти.

Типичная иерархия памяти процессора может включаться в себя в качестве верхнего уровня банк регистров общего назначения (GPR) в ядре процессора. Это наиболее быстрая память - во многих случаях применяющая оба фронта тактирующего сигнала, и таким образом способная записывать и считывать данные в течение одного цикла. Построенные из вентилей на кристалле процессора, GPR являются дорогостоящими с точки зрения кремниевой зоны, потребления энергии и затрат, налагаемых ими с точки зрения маршрутизации, распределения синхросигнала и тому подобного.

Регистры процессора можно дополнить одним или несколькими блоками кэш-памяти на кристалле, содержащими в себе первичные команды и структуры хранения данных для активной программы; например, коэффициент попадания во многих блоках кэш-памяти команд может достигать 97-98%. Кэш-память на кристалле (так же известная в данном уровне техники как кэш-память 1 уровня или L1) является дорогостоящей по тем же самым причинам, что и описанные выше в отношении к GPR. Однако кэш-память может быть выполнена в виде структур DRAM, достигая намного большей плотности и таким образом снижая стоимость за 1 бит относительно GPR. Для хранения команд и данных можно выделить отдельные блоки кэш-памяти, и блоками кэш-памяти данных можно управлять согласно ряду способов, как описано ниже в настоящем документе.

В зависимости от реализации процессор может включать в себя один или несколько блоков внекристальной, или L2, кэш-памяти. Блоки L2 кэш-памяти часто реализованы в SRAM для быстрого времени доступа и для избегания снижающих производительность требований DRAM к обновлениям. Ниже всех блоков кэш-памяти располагается основное запоминающее устройство, обычно выполненное в DRAM для максимальной плотности и, следовательно, наименьшей стоимости за бит. Основное запоминающее устройство можно дополнить накопителем на жестком диске, обычно выполненном в виде магнитного носителя с доступом посредством датчиков с механическим приводом, и, следовательно, чрезвычайно медленным по сравнению с электронным доступом верхних уровней иерархии памяти. Кроме того, данные диски могут быть дополнены ленточным накопителем или CD, содержащим соответственно магнитный или оптический носитель. Большинство переносных электронных устройств если и имеют, то ограниченное дисковое запоминающее устройство, и не имеют ленточного/CD резервирования, и, следовательно, основное запоминающее устройство (обычно ограниченное по размерам) является низшим уровнем иерархии памяти.

В иерархии компьютерной памяти каждый более низкий уровень сохраняет полную (но возможно устаревшую) копию данных, постоянно находящихся в более высоких уровнях. То есть данные, хранящиеся в более высоких уровнях, повторяют те, что в более низких уровнях. Изменения данных, хранящихся в высших уровнях иерархии памяти, должны передаваться вниз к более низким уровням. Изменения в GRP прямо передаются в кэш-память посредством команд STORE; изменения в кэш-памяти автоматически передаются в основное запоминающее устройство под руководством управляющего устройства кэш-памяти.

В целом, в данной области техники разработаны два подхода к распространению в основное запоминающее устройство изменений в данных в кэш-памяти: c немедленной записью и с отложенной записью. В кэш-памяти с немедленной записью, когда процессор записывает измененные данные в свою L1 кэш-память, он дополнительно записывает измененные данные в основную память (любые промежуточные блоки кэш-памяти опущены в контексте данного описания). В кэш-памяти с немедленной записью, основное запоминающее устройство всегда содержит наиболее новую версию данных; следовательно, данные, хранящиеся в записи кэш-памяти можно отбросить в любое время без специальной обработки. Как описано ниже, это упрощает управление кэш-памятью.

Следуя алгоритму отложенной записи, процессор может записать измененные данные в L1 кэш-память, но это не требует немедленного обновления основного запоминающего устройства. В этом случае элемент (запись) кэш-памяти, когда содержит данные, отличающиеся от версии в основном запоминающем устройстве, часто называется "грязным" элементом. Данный элемент кэш-памяти помечается для отражения этого факта установкой "грязного бита". Измененные данные записываются в основное запоминающее устройство в более позднее время, например, когда элемент кэш-памяти заменяется при обработке кэш-промаха, или под управлением программного обеспечения. Управление кэш-памятью с отложенной записью может улучшить производительность, когда процессор выполняет много записей данных, поскольку запись в кэш-память обычно вызывает намного меньшую задержку, чем запись в основную память. Алгоритм отложенной записи также сокращает шинный трафик к основному запоминающему устройству, что может уменьшить потребление энергии. Данные два алгоритма управления кэш-памятью не являются взаимоисключающими; одна кэш-память может управлять несколькими элементами (записями) по алгоритму немедленной записи, а остальными - используя алгоритм отложенной записи.

Поскольку объем кэш-памяти ограничен по сравнению с основным запоминающим устройством, кэш-память является совместно используемой всей памятью на временной основе. То есть данные из разных областей основного запоминающего устройства в разное время могут занимать одни и те же элементы (записи) кэш-памяти. Если обращение к памяти "промахивается" в кэш-памяти, то данные извлекаются из основного запоминающего устройства и сохраняются в данной кэш-памяти. Как только данная кэш-память во время использования заполнена данными, кэш-промах, извлекающий данные из памяти, должен заместить занятый в настоящее время элемент в кэш-памяти. Элемент кэш-памяти, управляемый по алгоритму с немедленной записью, может быть заменен без какой-либо специальной обработки.

Однако элемент кэш-памяти, управляемый по алгоритму с отложенной записью, перед заменой должен быть проверен, на предмет того, являются ли данные «грязными». Строку кэш-памяти необходимо прочитать и проверить «грязный» бит. Если имеющиеся данные в выбранном элементе кэш-памяти являются «грязными» (то есть отличаются от версии в основном запоминающем устройстве), то их необходимо записать в основное запоминающее устройство, прежде чем заменить элемент кэш-памяти новыми данными, прочитанными из основного запоминающего устройства. В большинстве реализаций процессор не знает об алгоритме управления кэш-памятью существующих элементов (записей) кэш-памяти. Следовательно, если любой из элементов в кэш-памяти управляется (или может управляться) по алгоритму с отложенной записью, то при замене каждый элемент необходимо прочитать для того, чтобы выяснить, является ли данный элемент элементом с отложенной записью, и если так, то является ли он грязным (и тот и другой вопрос можно свести к простой проверке грязного бита). Чтение каждого элемента кэш-памяти на предмет проверки грязного бита при замене данного элемента потребляет энергию и является излишним, если известно, что элементы кэш-памяти не были изменены.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Согласно одному или нескольким вариантам осуществления настоящего изобретения, чтение элемента кэш-памяти, выбранного для замены при обработке кэш-промаха (неудачного обращения к кэш-памяти), в кэш-памяти, поддерживающей управление отложенной записью, по меньшей мере, для одного элемента подавляется в ответ на индикацию того, что в данной кэш-памяти не был записан ни один из элементов кэш-памяти с отложенной записью.

По одному варианту осуществления предоставлен способ управления кэш-памятью, содержащей по меньшей мере одну запись, управляемую по алгоритму отложенной записи. Глобальный индикатор изменений (модифицируемый бит, указывающий, содержит ли какой-либо из элементов кэша с отложенной записью измененные данные), связанный с кэш-памятью, обновляется при записи в любой элемент кэш-памяти с отложенной записью. Глобальный индикатор изменений проверяется при кэш-промахах. Если глобальный индикатор изменений показывает, что ни один из элементов кэш-памяти с отложенной записью не содержит измененных данных, то элемент (запись) кэш-памяти, выбранный для замены, обновляется новыми данными без предварительного чтения данного элемента.

Согласно другому варианту осуществления предоставлен процессор, включающий в себя кэш-память, содержащую по меньшей мере один элемент (запись), управляемый по алгоритму отложенной записи, и глобальный индикатор изменений, показывающий, был ли записан любой из элементов кэш-памяти с отложенной записью. Процессор также включает в себя контроллер кэш-памяти, выполненный с возможностью заменять элемент в кэш-памяти без предварительного чтения данного элемента, если глобальный индикатор изменений показывает, что ни один из элементов кэш-памяти с отложенной записью не содержит измененных данных.

По еще одному варианту осуществления предоставлен способ обработки кэш-промаха в кэш-памяти, содержащей по меньшей мере один элемент, управляемый по алгоритму отложенной записи. Промах в кэш-памяти обнаруживается, и данные считываются из памяти. Если глобальный индикатор изменений показывает, что ни один из элементов кэш-памяти с отложенной записью не содержит измененных данных, то данные, прочитанные из памяти, записываются в данный выбранный элемент кэш-памяти без чтения содержимого данного элемента.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

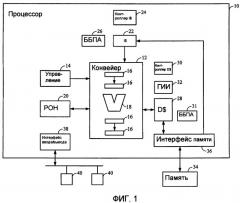

На фиг. 1 показана функциональная схема процессора.

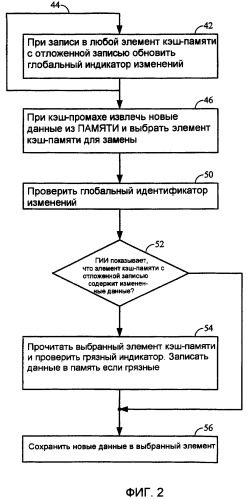

На фиг. 2 показана блок-схема способа обработки кэш-промаха.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

На фиг. 1 показана функциональная схема процессора 10. Процессор 10 исполняет команды в конвейере 12 выполнения команд согласно логической схеме 14 управления. В некоторых вариантах осуществления конвейер 12 может иметь суперскалярную архитектуру с несколькими параллельными конвейерами. Конвейер 12 включает в себя различные регистры или триггеры 16, образующие каскады (ступени) конвейера, и один или несколько арифметико-логических устройств (АЛУ) 18. Блок 20 регистров общего назначения (GPR, РОН) предоставляет регистры, представляющие верхушку иерархии памяти.

Конвейер 12 выбирает команды из кэш-памяти 22 команд (I-кэш или I$), управляемой контроллером 24 I-кэша. Трансляция и разрешения адресов памяти для команд управляется буфером 26 быстрого преобразования адресов со стороны команды (ITLB, ББПАК). Данные вызываются из кэша данных (D-кэш или D$) 28, управляемого контроллером 30 D-кэша. Глобальный индикатор 32 изменений (GMI, ГИИ) связан с D-кэшем. Как описано ниже, GMI является установленным всякий раз, когда записывается элемент кэш-памяти в D-кэше 28, и может быть очищен программным обеспечением, таким как следующее программное обеспечение очистки кэш-памяти, как описано ниже. Трансляция адресов памяти и прав доступа для данных управляется основным буфером 31 быстрого преобразования адресов (TLB, ББПА). В различных вариантах осуществления ITLB 26 может включать в себя копию части TLB 31. Альтернативно, ITLB 26 и TLB 31 можно объединить в единое целое. Подобным образом в различных вариантах осуществления можно объединить или унифицировать I-кэш 22 и D-кэш 28. Промахи в I-кэше 22 и/или D-кэше 28 вызывают обращение к основному (внекристальному) запоминающему устройству 34 под управлением интерфейса 36 памяти.

Процессор 10 может включать в себя интерфейс 38 ввода/вывода (I/O), управляющего доступом к различным периферийным устройствам 40. Специалисты в данной области техники признают, что возможны многочисленные разновидности процессора 10. Например, процессор 10 может включать в себя кэш-память второго уровня (L2) для I-кэша 22 и/или D-кэша 28. Кроме того, в отдельных вариантах осуществления, один или несколько функциональных блоков, показанных в процессоре 10, можно опустить.

Как описано выше, всякий раз, когда обращение к данным промахивается в D-кэше 28, запрашиваемые данные извлекаются из основного запоминающего устройства 34, и помещаются в D-кэш 28. Если D-кэш 28 полон (или, по некоторым алгоритмам замены, даже если нет), новые данные заменят существующий элемент в D-кэше 28. Если все элементы кэш-памяти управляются по алгоритму немедленной записи, данные можно просто записать в кэш-память, и предыдущие данные, хранящиеся в этом месте, будут перезаписаны. В этом случае не существует опасности уничтожить изменения, сделанные в данных, поскольку если процессор пользовался данными, прежде хранившимися в данном элементе кэш-памяти, то в этот момент они были незамедлительно "немедленно записаны" в основное запоминающее устройство 34.

Однако, если кэш-память поддерживает алгоритм отложенной записи, процессор 10 должен сначала считать существующую строку кэш-памяти, чтобы определить, не являются ли данные "грязными", то есть записанными без сопутствующего обновления основного запоминающего устройства 34. Процессоры предшествующего уровня техники просто выполняли это чтение всякий раз, когда заменялся элемент кэш-памяти. Однако, если известно, что ни один из элементов с отложенной записью D-кэша 28 не был записан, данную строку можно заменить без выполнения чтения для проверки грязного бита. Это увеличивает производительность процессора и уменьшает потребление энергии.

На фиг. 2 показан способ управления кэш-памятью по одному или нескольким вариантам осуществления настоящего изобретения. Каждый раз, когда процессор 10 записывает данные в любой элемент кэш-памяти с отложенной записью в кэш-памяти 28, для отражения этого факта изменяется глобальный индикатор 32 изменений (GMI) (этап 42). В простейшем случае GMI 32 может состоять из одного бита. Процессор 10 может быть осведомленным об алгоритме управления элементом (записью) кэш-памяти (немедленная или отложенная запись) посредством обращения к атрибутам страницы в просмотре TLB (таком, как при транслировании виртуального адреса в физический). Альтернативно, вся кэш-память или некоторый диапазон адресов может быть "зафиксирован" работать в одном или другом режиме, или аппаратно или посредством битов конфигурации. Согласно одному варианту осуществления GMI 32 устанавливается только при записи элемента кэш-памяти с отложенной записью; запись в элемент кэш-памяти с немедленной записью не устанавливает GMI 32. Установка GMI 32 при записи элемента кэш-памяти с отложенной записью является постоянно действующим процессом (как показано стрелкой в цикле 44).

При кэш-промахе данные извлекают из основного запоминающего устройства 34, и выбирают элемент кэш-памяти для сохранения новых данных (этап 46). Затем проверяют GMI 32 (этап 50). Если GMI 32 показывает, что данный элемент кэш-памяти прежде был записан (этап 32), например, в случае однобитного GMI 32, если данный бит установлен, то тогда данный элемент кэш-памяти заменяется по способу предшествующего уровня техники, в котором сначала читают строку для того, чтобы просмотреть, является ли она грязной, и если так, то обновляют основное запоминающее устройство (этап 54). Однако, если GMI 32 показывает, что ни один элемент кэш-памяти с отложенной записью в кэш-памяти 28 не был записан, процессор избегает этапа чтения элемента кэш-памяти, и напрямую заменяет его посредством записи в выбранный элемент кэш-памяти новых данных, извлеченных из памяти (этап 56). Таким образом, исключаются потребление энергии и дополнительная задержка на чтение элемента памяти для проверки грязного бита.

GMI 32 можно очистить или сбросить в состояние, показывающее, что ни один элемент кэш-памяти с отложенной записью не был записан, посредством программного обеспечения (дополнительно к системному сбросу). Это может произойти, например, следуя программной операции "очистки", когда данное программное обеспечение циклически проходит по кэш-памяти 28, записывая данные из всех грязных элементов кэш-памяти с отложенной записью в основное запоминающее устройство 34. Следует отметить, что одиночный GMI 32, связанный со всей кэш-памятью 28, энергосбережением и быстродействием процессора, описанными в данном документе, доступен только с момента, когда данный GMI 32 сброшен, и до момента, когда данные записаны в элемент кэш-памяти с отложенной записью. Как только элемент кэш-памяти с отложенной записью записан, все элементы кэш-памяти с отложенной записью необходимо прочитать перед заменой для проверки того, являются ли они грязными, пока программное обеспечение снова не очистит кэш-память и не сбросит данный GMI 32.

Как хорошо известно в данной области техники, кэш-память 22, 28 можно физически и логически структурировать множеством путей. Одним известным способом организации кэш-памяти является ассоциативность n-мерных наборов, в котором часть (виртуального или физического) адресного поля, называемого индексом, используют для выбора одного из n наборов элементов кэш-памяти, в который можно отобразить данные. По одному варианту осуществления каждый набор в кэш-памяти 28 может иметь ассоциированный с ним GMI 32 набора, показывающий, был ли прежде записан элемент кэш-памяти с отложенной записью из этого набора. Это позволяет процессору 10 получать энергетические и производительные преимущества для n-1 наборов в кэш-памяти 28, после того как в одном наборе был записан элемент кэш-памяти с отложенной записью.

Другой известной организацией кэш-памяти является разделение кэш-памяти 28 на два или более банка. Данные банки выбираются посредством поля выбора банка (виртуального или физического) адреса. По одному варианту осуществления каждый банк кэш-памяти 28 может иметь связанный с ними GMI 32 банка, показывающий, был ли прежде записан элемент кэш-памяти с отложенной записью из этого банка. Это позволяет процессору 10 получать энергетические и производительные преимущества для одного или более банков кэш-памяти 28, после того как в другом банке был записан элемент кэш-памяти с отложенной записью.

Несмотря на то, что настоящее изобретение было описано в настоящем документе в отношении конкретных признаков, аспектов и их вариантов осуществления, очевидно, что в широком смысле настоящего изобретения возможны многочисленные изменения, модификации, и другие варианты осуществления, и соответственно, все изменения, модификации и варианты осуществления будут считаться находящимися в объеме данного изобретения. Следовательно, настоящие варианты осуществления во всех аспектах предназначены как наглядные, а не ограничивающие, и все изменения, подпадающие под значение и эквивалентную область приложенной формулы изобретения, имеют целью быть охваченными ей.

1. Способ управления кэш-памятью, включающей в себя по меньшей мере один элемент, управляемый согласно алгоритму отложенной записи, содержащий этапы:обновление ассоциированного с упомянутой кэш-памятью модифицируемого бита, указывающего, содержит ли какой-либо из элементов кэш-памяти с отложенной записью измененные данные, после записи в любой элемент кэш-памяти с отложенной записью;проверка упомянутого модифицируемого бита при обработке неудачного обращения к кэш-памяти; изапись новых данных в выбранный элемент кэш-памяти без предварительного считывания этого элемента для определения, содержит ли он измененные данные, если упомянутый модифицируемый бит показывает, что ни один элемент кэш-памяти с отложенной записью в данной кэш-памяти не содержит измененных данных.

2. Способ по п.1, в котором кэш-память разделена на два или более банков, причем упомянутый модифицируемый бит банка ассоциирован с каждым банком, и выбранный элемент кэш-памяти заменяют без считывания, когда ассоциированный с банком упомянутый модифицируемый бит показывает, что ни один из элементов кэш-памяти с отложенной записью в данном банке не был записан.

3. Способ по п.1, в котором кэш-память является ассоциированной с n наборами кэш-памяти, причем упомянутый модифицируемый бит набора ассоциирован с каждым набором, и выбранный элемент кэш-памяти заменяют без считывания, когда упомянутый модифицируемый бит, ассоциированный с набором, указывает, что ни один из элементов кэш-памяти с отложенной записью в данном наборе не был записан.

4. Способ по п.1, в котором упомянутый модифицируемый бит может быть сброшен посредством программного обеспечения.

5. Способ по п.4, в котором программное обеспечение сбрасывает упомянутый модифицируемый бит после очистки кэш-памяти путем записи в память всех элементов с отложенной записью, содержащих измененные данные.

6. Процессор, содержащий:кэш-память, включающую в себя по меньшей мере один элемент, управляемый по алгоритму отложенной записи;модифицируемый бит, указывающий, содержит ли какой-либо из элементов кэш-памяти с отложенной записью измененные данные; иконтроллер кэш-памяти, выполненный с возможностью заменять элемент в кэш-памяти без предварительного считывания этого элемента, если упомянутый модифицируемый бит показывает, что ни один из элементов кэш-памяти с отложенной записью не содержит измененных данных.

7. Процессор по п.7, в котором кэш-память разделена на два или более банков и дополнительно содержит два или более модифицируемых битов банка, каждый из которых указывает, содержит ли какой-либо элемент кэш-памяти с отложенной записью измененные данные в ассоциированном банке, и при этом контроллер выполняет замену элемента кэш-памяти в банке без предварительного считывания этого элемента, если ассоциированный с банком упомянутый модифицируемый бит показывает, что ни один из элементов кэш-памяти с отложенной записью в данном банке не содержит измененных данных.

8. Процессор по п.7, в котором кэш-память является ассоциированной с n наборами кэш-памяти и дополнительно содержит два или более модифицируемых бита набора, каждый из которых показывает, содержит ли измененные данные какой-либо элемент кэш-памяти с отложенной записью в ассоциированном наборе кэш-памяти, и при этом контроллер выполняет замену элемента кэш-памяти в наборе без предварительного считывания этого элемента, если ассоциированный с набором упомянутый модифицируемый бит указывает, что ни один из элементов кэш-памяти с отложенной записью в данном наборе не содержит измененных данных.

9. Процессор по п.7, в котором упомянутый модифицируемый бит сбрасывают посредством программного обеспечения.

10. Способ обработки неудачного обращения к кэш-памяти в кэш-памяти, включающей в себя по меньшей мере один элемент, управляемый согласно алгоритму замещения с отложенной записью, в котором:обнаруживают неудачное обращение к кэш-памяти;считывают запрошенные данные из памяти изаписывают данные, считанные из памяти, в выбранный элемент без считывания содержимого данного элемента, если модифицируемый бит, указывающий, содержит ли измененные данные какой-либо из элементов кэш-памяти с отложенной записью, показывает, что ни один элемент кэш-памяти с отложенной записью не был записан.