Устройство восприятия изображений и система формирования изображений

Иллюстрации

Показать всеИзобретение относится к средствам формирования изображений. Техническим результатом является снижение энергопотребления при считывании сигнала пикселов на высокой скорости. Результат достигается тем, что устройство восприятия сигналов содержит пиксел, включающий в себя сигнальную шину столбцов, схему считывания, выходную шину и модуль вывода, а схема считывания включает в себя первый модуль накопления, первый модуль размыкания/замыкания, второй модуль накопления, модуль передачи и второй модуль размыкания/замыкания. Емкость первого модуля накопления меньше емкости второго модуля накопления, и сигнал, фиксируемый посредством второго модуля накопления, считывается в модуль вывода на основе емкости второго модуля накопления и емкости выходной шины. 4 н. и 10 з.п. ф-лы, 24 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к устройству восприятия изображений и системе формирования изображений.

Уровень техники

Согласно методике, раскрытой в опубликованном японском патенте № 2001-45378, в матрице пикселов, включающей в себя множество пикселов, размещенных в направлениях строк и столбцов, управляющие сигналы доставляются в пикселы посредством множества шин управления строками, идущими в направлении строк, и сигналы считываются из пикселов посредством множества сигнальных шин столбцов, идущих в направлении столбцов. Модуль накопления подключен к каждому концу сигнальной шины столбцов. Когда сигнал считывается из одного из двух модулей накопления, сигнал, выводимый из пиксела, накапливается в другом модуле накопления. Это укорачивает период гашения обратного хода (период без вывода датчика) и весь период считывания для считывания сигналов из матрицы пикселов в модули накопления.

В методике по опубликованному японскому патенту № 11-150255 два модуля накопления и два усилителя попеременно подключаются к каждой из множества сигнальных шин столбцов. Сигнал, накопленный в одном из двух модулей накопления, усиливается и выводится посредством одного из двух усилителей и затем накапливается в другом модуле накопления. Сигнал, накопленный в другом модуле накопления, усиливается посредством другого усилителя и затем считывается на выходную шину последующего каскада.

В методике, раскрытой в опубликованном японском патенте № 2001-45378, сигналы из пикселов первой строки матрицы пикселов накапливаются в одном модуле накопления, тогда как сигналы из пикселов второй строки накапливаются в другом модуле накопления. Сигнал, передаваемый из каждого модуля накопления в выходную шину последующего каскада, умножается на коэффициент усиления на основе соотношения емкостного деления, определенного посредством значения емкости каждого модуля накопления и значения емкости выходной шины. Например, когда модуль накопления имеет значение емкости C1, а выходная шина имеет значение емкости C2, коэффициент усиления задается посредством C1/(C1+C2). Значение емкости выходной шины содержит ее паразитную емкость и значение емкости, сформированное посредством емкостного элемента, предусмотренного в ней. В методике считывания согласно опубликованному японскому патенту № 2001-45378 с помощью такого емкостного деления, когда абсолютное значение емкости каждого из первого и второго модулей накопления является небольшим, усиление на основе соотношения емкостного деления между выходной шиной последующего каскада и емкостью каждого модуля накопления становится небольшим, и соотношение S/N снижается. Наоборот, когда абсолютное значение емкости каждого из одного и второго модуля накопления является значительным, усиление на основе соотношения емкостного деления между выходной шиной последующего каскада и емкостью каждого модуля накопления становится большим, и соотношение S/N растет. Тем не менее, это увеличивает площадь электродов каждого из одного и другого модулей накопления, приводя к повышению площади микросхемы.

Согласно методике по опубликованному японскому патенту № 11-150255 сигнал, накопленный в другом модуле накопления, усиливается посредством другого усилителя и считывается в последующий каскад, как описано выше. Следовательно, можно считывать сигнал на выходную шину последующего каскада без учета усиления на основе соотношения емкостного деления. Тем не менее, поскольку два усилителя подключены, для одного сигнала, к каждой из множества сигнальных шин столбцов, площадь микросхемы устройства считывания изображений может увеличиваться. Помимо этого, поскольку два усилителя работают для считывания одного сигнала, общее потребление энергии во всем периоде считывания устройства восприятия изображения может увеличиваться.

Раскрытие изобретения

Настоящее изобретение предоставляет устройство восприятия изображений и систему формирования изображений, которые позволяют уменьшать площадь микросхемы и сдерживать увеличение потребления энергии даже при считывании сигнала пикселов на высокой скорости.

Согласно первому аспекту настоящего изобретения предусмотрено устройство восприятия изображений, содержащее: пиксел, включающий в себя модуль фотоэлектрического преобразования; сигнальную шину столбцов, подключенную к пикселу; схему считывания, которая считывает сигнал из пиксела через сигнальную шину столбцов; выходную шину, подключенную к схеме считывания и имеющую емкость; и модуль вывода, который выводит сигнал изображения в соответствии с сигналом из схемы считывания через выходную шину, при этом схема считывания включает в себя первый модуль накопления, который фиксирует сигнал, считываемый в сигнальную шину столбцов, первый модуль размыкания/замыкания, который размыкает/замыкает соединение между сигнальной шиной столбцов и первым модулем накопления, второй модуль накопления, модуль передачи, который передает сигнал, зафиксированный посредством первого модуля накопления, во второй модуль накопления, и второй модуль размыкания/замыкания, который размыкает/замыкает соединение между модулем передачи и вторым модулем накопления, емкость первого модуля накопления меньше емкости второго модуля накопления, и сигнал, фиксируемый посредством второго модуля накопления, считывается в модуль вывода на основе емкости второго модуля накопления и емкости выходной шины.

Согласно второму аспекту настоящего изобретения предусмотрено устройство восприятия изображений, содержащее: первый пиксел; второй пиксел; сигнальную шину столбцов, подключенную к первому пикселу и второму пикселу; схему считывания, которая считывает сигнал из первого пиксела и второго пиксела через сигнальную шину столбцов; запускающий модуль, который запускает первый пиксел, второй пиксел и схему считывания; выходную шину, подключенную к схеме считывания и имеющую емкость; и модуль вывода, который выводит сигнал изображения в соответствии с сигналом из схемы считывания через выходную шину, при этом схема считывания включает в себя первый модуль накопления, который фиксирует сигнал, считываемый в сигнальную шину столбцов, первый модуль размыкания/замыкания, который размыкает/замыкает соединение между сигнальной шиной столбцов и первым модулем накопления, второй модуль накопления, модуль передачи, который передает сигнал, фиксируемый посредством первого модуля накопления, во второй модуль накопления, и входной контактный зажим и выходной контактный зажим которого подключены к первому модулю накопления, и выходной контактный зажим которого подключен ко второму модулю накопления, и второй модуль размыкания/замыкания, который размыкает/замыкает соединение между первым модулем накопления и модулем передачи, и вторым модулем накопления, емкость первого модуля накопления меньше емкости второго модуля накопления, сигнал, фиксируемый посредством второго модуля накопления, считывается в модуль вывода на основе емкости второго модуля накопления и емкости выходной шины, а управляющий модуль возбуждает первый пиксел, второй пиксел и схему считывания, чтобы в течение первого периода считывать сигнал первого пиксела из первого модуля накопления и передавать сигнал во второй модуль накопления посредством модуля передачи, а в течение второго периода после первого периода инструктировать первому модулю накопления накапливать сигнал второго пиксела, выводимый в сигнальную шину столбцов, и считывать сигнал первого пиксела из второго модуля накопления и передавать сигнал в модуль вывода.

Согласно третьему аспекту настоящего изобретения предусмотрена система формирования изображений, содержащая устройство восприятия изображений согласно первому и второму аспекту, оптическую систему, которая формирует изображение на плоскости формирования изображений устройства считывания изображений, и модуль обработки сигналов, который обрабатывает сигнал, выводимый из устройства считывания изображений, чтобы создать данные изображения.

Согласно настоящему изобретению можно уменьшать площадь микросхемы и сдерживать увеличение потребления энергии даже при считывании сигнала пикселов на высокой скорости.

Дополнительные признаки настоящего изобретения должны стать очевидными из последующего описания примерных вариантов осуществления со ссылкой на прилагаемые чертежи.

Краткое описание чертежей

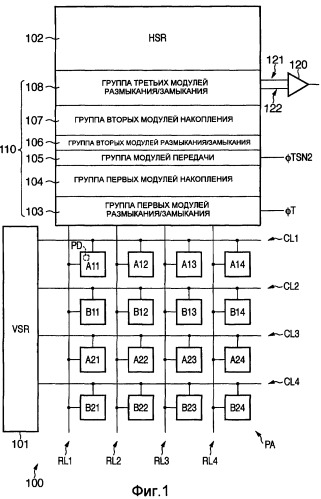

Фиг.1 - представление, показывающее компоновку устройства восприятия изображений согласно первому варианту осуществления настоящего изобретения;

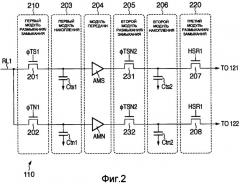

фиг.2 - принципиальная блок-схема, показывающая компоновку схемы одного столбца в схеме считывания;

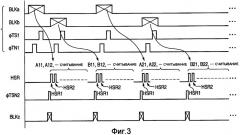

фиг.3 - временная диаграмма, показывающая работу схемы считывания;

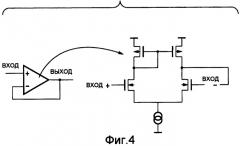

фиг.4 - принципиальная блок-схема, показывающая компоновку схемы модуля передачи;

фиг.5 - блок-схема, показывающая компоновку системы формирования изображений, использующей устройство восприятия изображений согласно первому варианту осуществления;

фиг.6 - представление, показывающее компоновку устройства 300 восприятия изображений согласно второму варианту осуществления настоящего изобретения;

фиг.7 - принципиальная блок-схема, показывающая компоновку схемы одного столбца в схеме считывания;

фиг.8 - представление, показывающее компоновку устройства 600 восприятия изображений согласно третьему варианту осуществления настоящего изобретения;

фиг.9 - принципиальная блок-схема, показывающая компоновку схемы одного столбца в схеме считывания;

фиг.10 - временная диаграмма, показывающая работу схемы считывания;

фиг.11 - представление для пояснения потенциала сброса;

фиг.12 - принципиальная блок-схема, показывающая компоновку схемы одного столбца в схеме считывания (модификация);

фиг.13 - представление, показывающее компоновку устройства 800 восприятия изображений согласно четвертому варианту осуществления настоящего изобретения;

фиг.14 - принципиальная блок-схема, показывающая компоновку схемы одного столбца в схеме считывания;

фиг.15 - временная диаграмма, показывающая работу схемы считывания;

фиг.16 - принципиальная блок-схема, показывающая компоновку модуля вывода;

фиг.17 - представление, показывающее компоновку устройства 900 восприятия изображений согласно пятому варианту осуществления настоящего изобретения;

фиг.18 - принципиальная блок-схема, показывающая компоновку схемы одного столбца в схеме считывания;

фиг.19 - временная диаграмма, показывающая работу схемы считывания;

фиг.20 - временная диаграмма, показывающая работу схемы считывания;

фиг.21 - представление, показывающее компоновку устройства 1000 восприятия изображений согласно шестому варианту осуществления настоящего изобретения;

фиг.22 - принципиальная блок-схема, показывающая компоновку схемы одного столбца в схеме считывания;

фиг.23 - временная диаграмма, показывающая работу схемы считывания; и

фиг.24 - временная диаграмма, показывающая работу схемы считывания.

Осуществление изобретения

Настоящее изобретение, в частности, направлено на устройство восприятия изображений, широко используемое в видеокамере, цифровом фотоаппарате, устройстве ввода изображений для сканера изображений и т.п.

Устройство 100 восприятия изображений согласно первому варианту осуществления описывается со ссылкой на фиг.1. Фиг.1 - это представление, показывающее компоновку устройства 100 восприятия изображений согласно первому варианту осуществления настоящего изобретения.

Устройство 100 восприятия изображений включает в себя матрицу PA пикселов, схему 101 вертикальной развертки (VSR, управляющий модуль), схему 110 считывания, схему 102 горизонтальной развертки (HSR, управляющий модуль), шины CL1-CL4 управления строками и шины RL1-RL4 управления столбцами. Устройство 100 восприятия изображений также имеет первую горизонтальную выходную шину 121, вторую горизонтальную выходную шину 122 и модуль 120 вывода.

Матрица PA пикселов включает в себя множество пикселов A11-B24, которые двумерно упорядочены (в матрице). Матрица 4×4 пикселов приведена в качестве примера в данном документе для удобства описания.

Каждый из пикселов A11-B24 включает в себя модуль PD фотоэлектрического преобразования. Модулем PD фотоэлектрического преобразования является, к примеру, фотодиод.

Схема вертикальной развертки (VSR) 101 предоставляет управляющие сигналы в пикселы A11-B24 через шины CL1-CL4 управления строками. Например, схема вертикальной развертки (VSR) 101 побуждает пиксел каждой строки в матрице PA пикселов выводить сигнал в соответствующую одну из сигнальных шин RL1-RL4 столбцов.

Схема 110 считывания считывает сигналы из пикселов A11-B24 через сигнальные шины RL1-RL4 столбцов. Схема 110 считывания включает в себя группу 103 первых модулей размыкания/замыкания, группу 104 первых модулей накопления, группу 105 модулей передачи, группу 106 вторых модулей размыкания/замыкания, группу 107 вторых модулей накопления и группу 108 третьих модулей размыкания/замыкания.

Группа 103 первых модулей размыкания/замыкания включает в себя множество первых модулей размыкания/замыкания, предусмотренных для соответствующих столбцов.

Группа 104 первых модулей накопления включает в себя множество первых модулей накопления, предусмотренных для соответствующих столбцов. Группа первых модулей накопления фиксирует сигналы, выводимые в сигнальные шины RL1-RL4 столбцов.

Группа 105 модулей передачи включает в себя множество модулей передачи, предусмотренных для соответствующих столбцов. Модули передачи передают сигналы, фиксируемые посредством первых модулей накопления, во вторые модули накопления. Модули передачи предоставляют сигналы, соответствующие электрическим зарядам, фиксируемым посредством первых модулей накопления, во вторые модули накопления.

Группа 106 вторых модулей размыкания/замыкания включает в себя множество вторых модулей размыкания/замыкания, предусмотренных для соответствующих столбцов. Группа 107 вторых модулей накопления включает в себя множество вторых модулей накопления, предусмотренных для соответствующих столбцов.

Группа 108 третьих модулей размыкания/замыкания включает в себя множество третьих модулей размыкания/замыкания, предусмотренных для соответствующих столбцов. Третьи модули размыкания/замыкания размыкают/замыкают соединение между вторыми модулями накопления и первой горизонтальной выходной шиной 121 или второй горизонтальной выходной шиной 122. Например, третьи модули размыкания/замыкания переводят вторые модули накопления и первую горизонтальную выходную шину 121 или вторую горизонтальную выходную шину 122 в состояние замыкания, тем самым электрически подключая вторые модули накопления к первой горизонтальной выходной шине 121 или второй горизонтальной выходной шине 122.

Схема горизонтальной развертки (HSR) 102 последовательно активирует сигнал горизонтальной развертки (HSR), который должен быть предоставлен в компоновку каждого столбца в схеме считывания, тем самым последовательно замыкая третий модуль размыкания/замыкания каждого столбца. С помощью этой операции схема горизонтальной развертки (HSR) 102 побуждает группу 108 третьих модулей размыкания/замыкания считывать сигнал из (вторых модулей накопления) каждого столбца схемы 110 считывания и выводить сигналы в модуль 120 вывода через первую горизонтальную выходную шину 121 и вторую горизонтальную выходную шину 122.

Каждая из первой горизонтальной выходной шины 121 и второй горизонтальной выходной шины 122 подключает (вторые модули накопления) схему 110 считывания к модулю 120 вывода.

Модуль 120 вывода выводит сигнал изображения в соответствии с сигналом, выводимым из схемы 110 считывания, через первую горизонтальную выходную шину 121 и вторую горизонтальную выходную шину 122. Т.е. модуль 120 вывода выводит сигнал изображения на основе сигналов, фиксируемых посредством вторых модулей накопления. Сигналы, фиксируемые посредством вторых модулей накопления, считываются в модуль 120 вывода посредством емкостного деления между емкостью второго модуля накопления и емкостью первой горизонтальной выходной шины 121 или второй горизонтальной выходной шины 122.

Компоновка схемы 110 считывания описывается далее со ссылкой на фиг.2. Фиг.2 - это принципиальная блок-схема, показывающая компоновку схемы одного столбца в схеме 110 считывания. Схемы, подключенные к сигнальной шине RL1 столбцов, большей частью описываются. Это также применимо к схемам, подключенным к оставшимся сигнальным шинам RL2-RL4 столбцов.

Например, первый пиксел A11 и второй пиксел B11 (фиг.1) подключены к верхней стороне сигнальной шины RL1 столбцов. Первый модуль 210 размыкания/замыкания, первый модуль 203 накопления, модуль 204 передачи, второй модуль 205 размыкания/замыкания, второй модуль накопления 206 и третий модуль 220 размыкания/замыкания подключены к нижней стороне сигнальной шины RL1 столбцов в этом порядке. Первая горизонтальная выходная шина 121 и вторая горизонтальная выходная шина 122 (фиг.1) подключены к последующему каскаду третьего модуля 220 размыкания/замыкания.

Первый модуль 210 размыкания/замыкания включает в себя переключатель 201 оптических сигналов и переключатель 202 шумовых сигналов. Первый модуль 203 накопления включает в себя модуль Cts1 накопления оптических сигналов (т.е. первый модуль накопления для оптического сигнала) и модуль Ctn1 накопления шумовых сигналов (т.е. первый модуль накопления для шумового сигнала). Модуль 204 передачи включает в себя буферный усилитель AMS оптических сигналов и буферный усилитель AMN шумовых сигналов, которые являются преобразователями полного сопротивления. Второй модуль 205 размыкания/замыкания включает в себя переключатель 231 оптических сигналов и переключатель 232 шумовых сигналов. Второй модуль 206 накопления включает в себя модуль Cts2 накопления оптических сигналов (т.е. второй модуль накопления для оптического сигнала) и модуль Ctn2 накопления шумовых сигналов (т.е. второй модуль накопления для шумового сигнала). Третий модуль 220 размыкания/замыкания включает в себя переключатель 207 оптических сигналов и переключатель 208 шумовых сигналов.

В компоновке схемы столбца, показанной на фиг.2, каждый переключатель 201 и т.п. может включать в себя либо NMOS-транзистор, либо PMOS-транзистор.

Далее описывается работа схемы 110 считывания. Фиг.3 - это временная диаграмма, показывающая работу схемы 110. Все сигналы, проиллюстрированные на фиг.3, являются активными на высоком уровне. Следует отметить, что случай, когда сигнал активен на низком уровне, может быть предусмотрен посредством инвертирования логических уровней сигнала. На фиг.3 сигналы φTS1, φTN1 и φTSN2 предоставляется из схемы вертикальной развертки (VSR) 101 в схему 110 считывания. Сигнал HSR предоставляется из схемы горизонтальной развертки (HSR) 102 в схему 110 считывания.

В течение периода BLKa (т.е. второго периода), пока φTN1 активирован, переключатель 202 включается, так что модуль Ctn1 накопления шумовых сигналов накапливает шумовой сигнал, выводимый из первого пиксела A11 в сигнальную шину RL1 столбцов. Пока φTS1 активирован, переключатель 201 включается, так что модуль Cts1 накопления оптических сигналов накапливает оптический сигнал, выводимый из первого пиксела A11 в сигнальную шину RL1 столбцов. Т.е. первый модуль 203 накопления накапливает сигнал, выводимый из первого пиксела A11 в сигнальную шину RL1 столбцов.

В течение периода BLKc (т.е. первого периода), пока φTSN2 активирован, переключатели 231 и 232 включаются. Буферный усилитель AMS оптических сигналов считывает оптический сигнал первого пиксела A11 из модуля накопления Cts1 оптических сигналов и передает его в модуль Cts2 накопления оптических сигналов. Буферный усилитель AMN шумовых сигналов считывает шумовой сигнал первого пиксела A11 из модуля Ctn1 накопления шумовых сигналов и передает его в модуль Ctn2 накопления шумовых сигналов. Т.е. модуль 204 передачи считывает сигнал первого пиксела A11 из первого модуля 203 накопления и передает его во второй модуль 206 накопления.

В течение периода BLKb (т.е. второго периода), следующего после периода BLKc, пока φTN1 активирован, переключатель 202 включается, так что модуль Ctn1 накопления шумовых сигналов накапливает шумовой сигнал, выводимый из второго пиксела B11 в сигнальную шину RL1 столбцов. Пока φTS1 активирован, переключатель 201 включается, так что модуль Cts1 накопления оптических сигналов накапливает оптический сигнал, выводимый из второго пиксела B11 в сигнальную шину RL1 столбцов. Т.е. первый модуль 203 накопления накапливает сигнал, выводимый из второго пиксела B11 в сигнальную шину RL1 столбцов.

В течение периода BLKb (т.е. второго периода), пока сигнал HSR1 для сигнальной шины RL1 столбцов в сигнале HSR горизонтальной развертки активирован, переключатели 207 и 208 включаются, чтобы считывать сигнал первого пиксела A11 из второго модуля 206 накопления. Более конкретно, оптический сигнал первого пиксела A11 считывается из модуля Cts2 накопления оптических сигналов в первую горизонтальную выходную шину 121 посредством емкостного деления между емкостью модуля Cts2 накопления оптических сигналов и емкостью первой горизонтальной выходной шины 121. Следовательно, оптический сигнал первого пиксела A11 передается в модуль 120 вывода через первую горизонтальную выходную шину 121. Шумовой сигнал первого пиксела A11 считывается из модуля Ctn2 накопления шумовых сигналов во вторую горизонтальную выходную шину 122 посредством емкостного деления между емкостью модуля Ctn2 накопления шумовых сигналов и емкостью второй горизонтальной выходной шины 122. Следовательно, шумовой сигнал первого пиксела A11 передается в модуль 120 вывода через вторую горизонтальную выходную шину 122. Модуль 120 вывода вычисляет разность между оптическим сигналом, передаваемым через первую горизонтальную выходную шину 121, и шумовым сигналом, передаваемым через вторую горизонтальную выходную шину 122, и выводит разностный сигнал между ними в последующий каскад в качестве сигнала изображения.

Вышеописанная операция повторяется.

Следует отметить, что хотя операция схемы 110 считывания описана относительно сигнальной шины RL1 столбцов, за исключением сигнала HSR горизонтальной развертки, операции схемы 110 считывания для оставшихся сигнальных шин RL2-RL4 столбцов являются такими же, как на фиг.3. В сигнале HSR горизонтальной развертки сигналы HSR2-HSR4 для оставшихся сигнальных шин RL2-RL4 столбцов (фиг.1) активируются последовательно после активного периода сигнала HSR1 для сигнальной шины RL1 столбцов.

Период BLKc, в котором сигнал, фиксируемый посредством первого модуля 203 накопления, передается во второй модуль 206 накопления, короче периода BLKa, в котором сигнал первого пиксела A11 считывается в первый модуль 203 накопления. Период BLKc, в котором сигнал, фиксируемый посредством первого модуля 203 накопления, передается во второй модуль 206 накопления, короче периода BLKb, в котором сигнал второго пиксела B11 считывается в первый модуль 203 накопления. Это обусловлено тем, что площадь схемы 110 считывания меньше площади матрицы PA пикселов (к примеру, площадь имеет сторону от нескольких мм до нескольких десятков мм длиной). Т.е. время, требуемое для передачи сигнала через площадь схемы 110 считывания, короче времени, требуемого для передачи сигнала через площадь матрицы PA пикселов.

Емкость (площадь электродов) первого модуля 203 накопления может быть меньше емкости второго модуля 206 накопления. Причина этого следующая.

В методике, раскрытой в опубликованном японском патенте № 2001-45378, один из двух модулей накопления, подключенных к каждой из множества сигнальных шин столбцов, должен иметь емкость (площадь электродов), такую как емкость другого модуля накопления, чтобы уравнять усиление для считывания, как описано выше. Когда сигнал считывается из каждого из двух модулей накопления в горизонтальную выходную шину, усиление считывания определяется в соответствии с соотношением емкостного деления между емкостью модуля накопления и емкостью горизонтальной выходной шины. Чтобы не допустить слишком низкого усиления считывания, оба из двух модулей накопления должны иметь большое сопротивление (площадь электродов). Как результат, площадь микросхемы возрастает и выход годных микросхем неизбежно падает.

Тем не менее, в этом варианте осуществления модуль 204 передачи, включающий в себя буферный усилитель AMS оптических сигналов и буферный усилитель AMN шумовых сигналов, предусмотрен между первым модулем 203 накопления и вторым модулем 206 накопления. Модуль 204 передачи предоставляет сигнал, соответствующий электрическим зарядам, фиксируемым посредством первого модуля 203 накопления, во второй модуль 206 накопления, вместо непосредственного предоставления самих электрических зарядов, фиксируемых посредством первого модуля 203 накопления, во второй модуль 206 накопления. Это предотвращает влияние емкости первого модуля 203 накопления на емкостное деление между емкостью второго модуля 206 накопления и емкостью первой горизонтальной выходной шины 121 или второй горизонтальной выходной шины 122 при считывании сигнала на модуль 120 вывода посредством емкости. Это обусловлено тем, что даже когда первый модуль 203 накопления имеет емкость меньше емкости второго модуля 206 накопления, производительность, с которой сигнал считывается из первого модуля 203 накопления во второй модуль 206 накопления, не использует емкостное деление. Как следствие, можно считывать высококачественные данные изображений на высокой скорости посредством улучшения усиления и отношения S/N без увеличения площади микросхемы и снижения выхода годных микросхем. Т.е. согласно этому изобретению можно снижать ухудшение качества изображения и уменьшать площадь микросхемы даже при считывании сигнала пикселов на высокой скорости.

В методике по опубликованному японскому патенту № 11-150255 два модуля накопления и два усилителя попеременно подключаются, в соответствии с одним сигналом, к каждой из множества сигнальных шин столбцов. Сигнал, накопленный в одном из двух модулей накопления, усиливается посредством одного из двух усилителей и затем накапливается в другом модуле накопления. Сигнал, накопленный в другом модуле накопления, усиливается посредством другого усилителя и считывается на выходную шину последующего каскада, как описано выше. В этом случае производительность, с которой сигнал считывается из двух модулей накопления, не использует емкостное деление. Поэтому можно считывать сигнал без понижения усиления независимо от емкостей двух модулей накопления. Тем не менее, поскольку два усилителя подключены к каждой из множества сигнальных шин столбцов, площадь микросхемы устройства восприятия изображений может увеличиваться. Помимо этого, поскольку два усилителя работают для считывания одного сигнала, общее потребление энергии во всем периоде считывания устройства восприятия изображения может увеличиваться.

В этом варианте осуществления, тем не менее, только один усилитель подключен, для одного сигнала, к каждой из множества сигнальных шин столбцов. По этой причине площадь микросхемы устройства восприятия изображений может быть уменьшена. Кроме того, только один усилитель работает для считывания одного сигнала (т.е. оптического сигнала или шумового сигнала). По этой причине потребление энергии в устройстве восприятия изображений может быть сдержано в сравнении с методикой по опубликованному японскому патенту № 11-150255. Т.е. можно снижать площадь микросхемы и сдерживать увеличение потребления энергии даже при считывании сигнала пикселов на высокой скорости.

Буферные усилители AMS и AMN модуля 204 передачи могут быть спроектированы так, чтобы применять усиление. Альтернативно, буфер, усиление которого равно 1, может быть использован просто для того, чтобы не допускать какого-либо увеличения соотношения емкостного деления между первым модулем 203 накопления и вторым модулем 206 накопления. Фиг.4 показывает пример буферного усилителя, выступающего в качестве повторителя напряжения, усиление которого равно 1.

Фиг.5 иллюстрирует пример системы формирования изображений, использующей устройство 100 восприятия изображений по настоящему изобретению.

Система 90 формирования изображений включает в себя главным образом оптическую систему, устройство 100 восприятия изображений и модуль обработки сигналов, как показано на фиг.5. Оптическая система включает в себя главным образом затвор 91, объектив 92 и диафрагму 93. Модуль обработки сигналов включает в себя главным образом схему 95 обработки считанных сигналов, A/D-преобразователь 96, модуль 97 обработки сигнала изображений, модуль 87 запоминающего устройства, внешний I/F-модуль 89, модуль 98 генератора синхросигналов, модуль глобального управления/арифметический модуль 99, носитель 88 записи и I/F-модуль 94 управления носителями записи. Модуль обработки сигналов не обязательно всегда должен включать в себя носитель 88 записи.

Затвор 91 находится напротив объектива 92 в оптическом пути, чтобы управлять экспозицией.

Объектив 92 преломляет падающий свет и формирует изображение объекта на плоскости формирования изображений (матрице PA пикселов) устройства 100 восприятия изображений.

Диафрагма 93 предусмотрена в оптическом пути между объективом 92 и устройством 100 восприятия изображений, чтобы регулировать количество света, которое проходит через объектив 92 и направляется в устройство 100 восприятия изображений.

Устройство 100 восприятия изображений преобразует изображение объекта, сформированное на плоскости формирования изображений (матрица PA пикселов), в сигнал изображения. Устройство 100 восприятия изображений считывает сигнал изображения из матрицы PA пикселов и выводит его.

Схема 95 обработки воспринятых сигналов подключена к устройству 100 восприятия изображений, чтобы обработать сигнал изображения, выводимый из устройства 100 восприятия изображений.

A/D-преобразователь 96 подключен к схеме 95 обработки воспринятых сигналов, чтобы преобразовывать обработанный сигнал изображения (аналоговый сигнал), выводимый из схемы 95 обработки воспринятых сигналов, в сигнал изображения (цифровой сигнал).

Модуль 97 обработки сигналов изображений подключен к A/D-преобразователю 96, чтобы выполнять арифметические процессы, такие как возможные виды поправки на сигнал изображения (цифровой сигнал), выводимый из A/D-преобразователя 96, тем самым формируя данные изображений. Данные изображений предоставляются в модуль 87 запоминающего устройства, внешний I/F-модуль 89, модуль глобального контроля/арифметический модуль 99 и I/F-модуль 94 управления носителями записи.

Модуль 87 запоминающего устройства подключен к модулю 97 обработки сигналов изображений, чтобы сохранять данные изображений, выводимые из модуля 97 обработки сигналов изображений.

Внешний I/F-модуль 89 подключен к модулю 97 обработки сигналов изображений так, чтобы данные изображений, выводимые из модуля 97 обработки сигналов изображений, передавались на внешнее устройство (к примеру, персональный компьютер) посредством внешнего I/F-модуля 89.

Модуль 98 генератора синхросигналов подключен к устройству 100 восприятия изображений, схеме 95 обработки воспринятых сигналов, A/D-преобразователю 96 и модулю 97 обработки сигналов изображений, чтобы предоставлять им синхросигнал. Устройство 100 восприятия изображений, схема 95 обработки воспринятых сигналов, A/D-преобразователь 96 и модуль 97 обработки сигналов изображений работают синхронно с синхросигналом.

Модуль глобального контроля/арифметический модуль 99 подключен к модулю 98 генератора синхросигналов, модулю 97 обработки сигналов изображений и I/F-модулю 94 управления носителем записи, чтобы полностью управлять ими.

Носитель 88 записи разъемным образом соединяется с I/F-модулем 94 управления носителем записи. Данные изображений, выводимые из модуля 97 обработки сигналов изображений, записываются на носитель 88 записи посредством I/F-модуля 94 управления носителем записи.

При вышеуказанной компоновке, когда устройство 100 восприятия изображений позволяет получать хороший сигнал изображения, хорошее изображение (данные изображения) может быть получено.

Устройство 300 восприятия изображений согласно второму варианту осуществления настоящего изобретения описывается далее со ссылкой на фиг.6 и 7. Фиг.6 - это представление, показывающее компоновку устройства 300 восприятия изображений согласно второму варианту осуществления настоящего изобретения. Фиг.7 - это принципиальная блок-схема, показывающая компоновку схемы одного столбца в схеме считывания. Части, отличающиеся от первого варианта осуществления, главным образом описываются ниже, а описание совпадающих частей опущено.

Устройство 300 восприятия изображений имеет такую же базовую компоновку, что и в первом варианте осуществления, за исключением схемы 310 считывания. Схема 310 считывания отличается от первого варианта осуществления тем, что она включает в себя группу 305 модулей передачи.

Как показано на фиг.7, модуль 504 передачи каждого столбца, включенного в группу 305 модулей передачи, включает в себя истоковый повторитель SFs оптических сигналов и истоковый повторитель SFn шумовых сигналов. Истоковый повторитель SFs оптических сигналов включает в себя NMOS-транзистор MS и источник Is постоянного тока. Истоковый повторитель SFn шумовых сигналов включает в себя NMOS-транзистор MN и источник In постоянного тока.

MOS-транзистор MS принимает, через затвор, сигнал, фиксируемый посредством модуля Cts1 накопления оптических сигналов первого модуля 203 накопления, и выводит, через исток, сигнал, соответствующий сигналу, вводимому в затвор, в модуль Cts2 накопления оптических сигналов второго модуля 206 накопления.

MOS-транзистор MN принимает, через затвор, сигнал, фиксируемый посредством модуля Ctn1 накопления шумовых сигналов первого модуля 203 накопления, и выводит, через исток, сигнал, соответствующий сигналу, вводимому через затвор, в модуль Ctn2 накопления шумовых сигналов второго модуля 206 накопления.

Модуль 504 передачи, включающий в себя истоковый повторитель SFs оптических сигналов и истоковый повторитель SFn шумовых сигналов, может повышать входное полное сопротивление и понижать выходное сопротивление за счет простой компоновки. Модуль 504 передачи предоставляет сигнал, соответствующий электрическим зарядам, фиксируемым посредством первого модуля 203 накопления, во второй модуль 206 накопления, вместо непосредственного предоставления самих электрических зарядов, фиксируемых посредством первого модуля 203 накопления, во второй модуль 206 накопления, как в первом варианте осуществления.

Каждый из истокового повторителя SFs оптических сигналов и истокового повторителя SFn шумовых сигналов модуля 504 передачи может включать в себя PMOS-транзистор вместо NMOS-транзистора (MOS-транзистора MS или MN).

Устройство 600 восприятия изображений согласно третьему варианту осуществления настоящего изобретения описывается далее со ссылкой на фиг.8-11. Фиг.8 - это представление, показывающее компоновку устройства 600 восприятия изображений согласно третьему варианту осуществления настоящего изобретения. Фиг.9 - это принципиальная блок-схема, показывающая компоновку схемы одного столбца в схеме считывания. Фиг.10 - это временная диаграмма, показывающая работу схемы считывания. Фиг.11 - это представление для пояснения потенциала сброса. Части, отличающиеся от первого и второго вариантов осуществления, главным образом описываются ниже, а описание совпадающих частей опущено.

Устройство 600 восприятия изображений имеет такую же базовую компоновку, что и в первом и втором вариантах осуществления, за исключением схемы 610 считывания. Схема 610 считывания отличается от первого и второго вариантов осуществления тем, что она включает в себя группу 609 первых модулей сброса между группой 107 вторых модулей накопления и группой 108 третьих модулей размыкания/замыкания.

Первый модуль 709 сброса каждого столбца, включенного в группу 609 первых модулей сброса, предоставляется между вторым модулем 206 накопления и третьим модулем 220 размыкания/замыкания, как показано на фиг.9. Первый модуль 709 сброса включает в себя транзистор MRS сброса оптических сигналов и транзи