Каскодный дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)). Технический результат: повышение коэффициента усиления по напряжению при сохранении высокой стабильности статического режима каскодного дифференциального усилителя (КДУ). КДУ содержит первый (1) и второй (2) входные транзисторы (Т), базы которых подключены к источнику напряжения смещения (ИНС) (3), первый (4) и второй (5) токостабилизирующие двухполюсники, связанные с соответствующими первым (6) и вторым (7) входами КДУ и эмиттерами Т (1) и Т (2), первый (8) и второй (9) двухполюсники нагрузки, подключенные к коллекторам соответствующих Т (1) и Т (2), а также базам первого (10) и второго (11) выходных Т, выходной сумматор токов (12), первый (13) и второй (14) входы которого соединены с коллекторами Т (10) и Т (11). В схему введены первый-шестой (15-20) дополнительные Т, третий (21) токостабилизирующий двухполюсник, а также первый (22) и второй (23) вспомогательные p-n переходы, причем первый (6) вход КДУ связан с эмиттером Т (1) через первый (22) дополнительный p-n переход, второй (7) вход КДУ связан с эмиттером Т (2) через второй (23) дополнительный p-n переход, база Т (15) подключена к коллектору Т (1), база Т (16) подключена к коллектору Т (2), коллектор Т (15) соединен с эмиттером Т (18), коллектор Т (16) связан с эмиттером Т (17), база Т (17) подключена к эмиттеру Т (1), база Т (18) подключена к эмиттеру Т (2), коллектор Т (17) соединен с эмиттером Т (19), база Т (19) подключена к первому входу (6) КДУ, база Т (20) соединена со вторым (7) входом КДУ, коллекторы Т (19) и Т (20) объединены и подключены к общей точке первого (4), второго (5) и третьего (21) токостабилизирующих двухполюсников, а свободный вывод третьего токостабилизирующего двухполюсника (21) связан с шиной источника питания (22). 5 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны схемы так называемых «перегнутых» каскодных дифференциальных усилителей (КДУ) на n-p-n и p-n-p транзисторах [1-40], которые стали основой более чем 20 серийных операционных усилителей, выпускаемых как зарубежными (НА2520, НА5190, AD797, AD8631, AD8632, ОР90 и др.), так и российскими (154УДЗ и др.) микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ на их модификации выдано более 50 патентов. Предлагаемое изобретение относится к данному подклассу устройств.

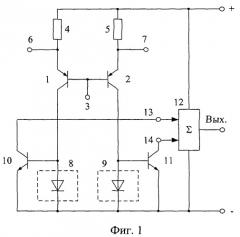

Ближайшим прототипом (фиг.1) заявляемого устройства является каскодный дифференциальный усилитель (КДУ), описанный в патенте США №3979689, содержащий первый 1 и второй 2 входные транзисторы, базы которых подключены к источнику напряжения смещения 3, первый 4 и второй 5 токостабилизирующие двухполюсники, связанные с соответствующими первым 6 и вторым 7 входами каскодного усилителя и эмиттерами первого 1 и второго 2 входных транзисторов, первый 8 и второй 9 двухполюсники нагрузки, подключенные к коллекторам соответствующих первого 1 и второго 2 входных транзисторов, а также базам первого 10 и второго 11 выходных транзисторов, выходной сумматор токов 12, первый 13 и второй 14 входы которого соединены с коллекторами первого 10 и второго 11 выходных транзисторов.

Существенный недостаток известного КДУ (фиг.1) состоит в том, что при повышении его коэффициента усиления по напряжению он не обеспечивает высокую стабильность статического режима выходного каскада («выходной сумматор токов 12 - второй выходной транзистор 11»), что отрицательно сказывается на его частотных характеристиках, а также работоспособности и токопотреблении при изменениях температуры и разбросе параметров элементов.

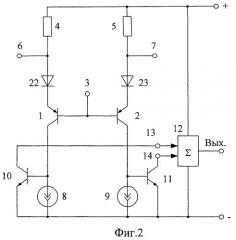

Действительно, предельно возможные (для данной архитектуры КДУ) значения коэффициента усиления по напряжению (Ку) реализуются, если в качестве двухполюсников 8 и 9 включить источники опорного тока (фиг.2). В этом случае коэффициент усиления по напряжению КДУ фиг.1 будет определяться эквивалентными сопротивлениями в коллекторной цепи транзисторов 1 и 2:

RН.ЭКВ.1≈β10rэ10,

RН.ЭКВ.2≈β11rэ11,

где β10, β11 - коэффициент усиления по току базы транзисторов 10 и 11;

rэ10, rэ11 - сопротивления эмиттерных переходов транзисторов 10 и 11.

При миллиамперных токах и β=50 имеем Rн.экв.1=Rн.экв.2≈1,2 Ком, что крайне мало для получения предельных Ку.

Таким образом, в КДУ-прототипе фиг.1 сдерживающим фактором при повышении его Ку являются низкие значения эквивалентных сопротивлений Rн.экв.1 и Rн.экв.2 в коллекторной цепи транзисторов 1 и 2.

Кроме этого введение вместо двухполюсников 8 и 9 источников опорного тока I8 и I9 (фиг.2) способствует повышению Ку до его предельного значения (Ку.max). Однако при этом известная схема КДУ становится практически неработоспособной из-за проблем со стабильностью статического режима транзисторов 10 и 11. Поэтому в микроэлектронике такой способ достижения предельного Ку в КДУ (фиг.2) не используется. Как следствие, в данной схеме в качестве двухполюсников 8 и 9 всегда применяются p-n переходы.

Рассмотренное техническое противоречие разрешается в заявляемом КДУ за счет введения новых элементов и связей между ними.

Основная задача предлагаемого изобретения состоит в повышении коэффициента усиления по напряжению при сохранении высокой стабильности статического режима КДУ.

Поставленная задача достигается тем, что в каскодном дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, базы которых подключены к источнику напряжения смещения 3, первый 4 и второй 5 токостабилизирующие двухполюсники, связанные с соответствующими первым 6 и вторым 7 входами каскодного усилителя и эмиттерами первого 1 и второго 2 входных транзисторов, первый 8 и второй 9 двухполюсники нагрузки, подключенные к коллекторам соответствующих первого 1 и второго 2 входных транзисторов, а также базам первого 10 и второго 11 выходных транзисторов, выходной сумматор токов 12, первый 13 и второй 14 входы которого соединены с коллекторами первого 10 и второго 11 выходных транзисторов, предусмотрены новые элементы и связи - в схему введены первый 15, второй 16, третий 17, четвертый 18, пятый 19 и шестой 20 дополнительные транзисторы, третий 21 токостабилизирующий двухполюсник, а также первый 22 и второй 23 вспомогательные p-n переходы, причем первый 6 вход каскодного дифференциального усилителя связан с эмиттером первого 1 входного транзистора через первый 22 дополнительный p-n переход, второй 7 вход каскодного дифференциального усилителя связан с эмиттером второго 2 входного транзистора через второй 23 дополнительный p-n переход, база первого 15 дополнительного транзистора подключена к коллектору первого 1 входного транзистора, база второго 16 дополнительного транзистора подключена к коллектору второго 2 входного транзистора, коллектор первого 15 дополнительного транзистора соединен с эмиттером четвертого 18 дополнительного транзистора, коллектор второго 16 дополнительного транзистора связан с эмиттером третьего 17 дополнительного транзистора, база третьего 17 дополнительного транзистора подключена к эмиттеру первого 1 входного транзистора, база четвертого 18 дополнительного транзистора подключена к эмиттеру второго 2 выходного транзистора, коллектор третьего 17 дополнительного транзистора соединен с эмиттером пятого 19 дополнительного транзистора, коллектор четвертого 18 дополнительного транзистора соединен с эмиттером шестого 20 дополнительного транзистора, база пятого 19 дополнительного транзистора подключена к первому 6 входу каскодного дифференциального усилителя, база шестого 20 дополнительного транзистора соединена со вторым 7 входом каскодного дифференциального усилителя, коллекторы пятого и шестого дополнительных транзисторов объединены и подключены к общей точке первого 4, второго 5 и третьего 21 токостабилизирующих двухполюсников, а свободный вывод третьего 21 токостабилизирующего двухполюсника связан с шиной источника питания 22, при этом первый 15, четвертый 18 и шестой 20 дополнительные транзисторы, а также второй 16, третий 17 и пятый 19 дополнительные транзисторы обеспечивают отрицательную обратную связь по синфазному сигналу.

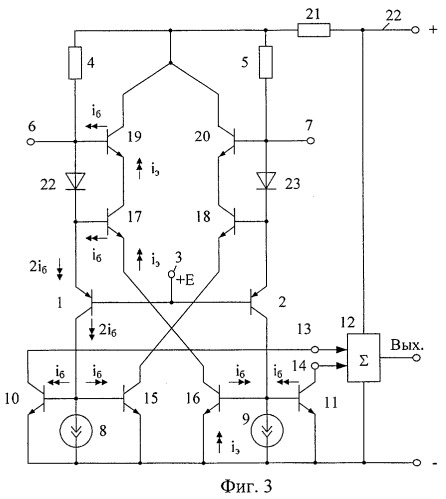

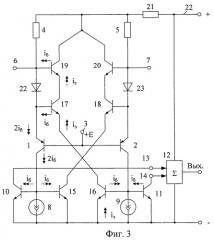

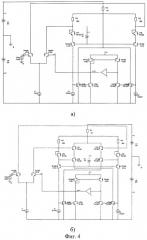

Схема усилителя-прототипа изображена на чертежах фиг.1 и фиг.2. На чертеже фиг.3 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения.

На чертеже фиг.4 показана схема заявляемого (б) и сравниваемого (а) с ним устройств в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на чертеже фиг.5 - результаты компьютерного моделирования данных схем - зависимости их коэффициента усиления Ку от частоты.

Дифференциальный усилитель фиг.3 содержит первый 1 и второй 2 входные транзисторы, базы которых подключены к источнику напряжения смещения 3, первый 4 и второй 5 токостабилизирующие двухполюсники, связанные с соответствующими первым 6 и вторым 7 входами каскодного усилителя и эмиттерами первого 1 и второго 2 входных транзисторов, первый 8 и второй 9 двухполюсники нагрузки, подключенные к коллекторам соответствующих первого 1 и второго 2 входных транзисторов, а также базам первого 10 и второго 11 выходных транзисторов, выходной сумматор токов 12, первый 13 и второй 14 входы которого соединены с коллекторами первого 10 и второго 11 выходных транзисторов. В схему введены первый 15, второй 16, третий 17, четвертый 18, пятый 19 и шестой 20 дополнительные транзисторы, третий 21 токостабилизирующий двухполюсник, а также первый 22 и второй 23 вспомогательные p-n переходы, причем первый 6 вход каскодного дифференциального усилителя связан с эмиттером первого 1 входного транзистора через первый 22 дополнительный p-n переход, второй 7 вход каскодного дифференциального усилителя связан с эмиттером второго 2 входного транзистора через второй 23 дополнительный p-n переход, база первого 15 дополнительного транзистора подключена к коллектору первого 1 входного транзистора, база второго 16 дополнительного транзистора подключена к коллектору второго 2 входного транзистора, коллектор первого 15 дополнительного транзистора соединен с эмиттером четвертого 18 дополнительного транзистора, коллектор второго 16 дополнительного транзистора связан с эмиттером третьего 17 дополнительного транзистора, база третьего 17 дополнительного транзистора подключена к эмиттеру первого 1 входного транзистора, база четвертого 18 дополнительного транзистора подключена к эмиттеру второго 2 выходного транзистора, коллектор третьего 17 дополнительного транзистора соединен с эмиттером пятого 19 дополнительного транзистора, коллектор четвертого 18 дополнительного транзистора соединен с эмиттером шестого 20 дополнительного транзистора, база пятого 19 дополнительного транзистора подключена к первому 6 входу каскодного дифференциального усилителя, база шестого 20 дополнительного транзистора соединена со вторым 7 входом каскодного дифференциального усилителя, коллекторы пятого и шестого дополнительных транзисторов объединены и подключены к общей точке первого 4, второго 5 и третьего 21 токостабилизирующих двухполюсников, а свободный вывод третьего 21 токостабилизирующего двухполюсника связан с шиной источника питания 22, при этом первый 15, четвертый 18 и шестой 20 дополнительные транзисторы, а также второй 16, третий 17 и пятый 19 дополнительные транзисторы обеспечивают отрицательную обратную связь по синфазному сигналу.

Рассмотрим вначале особенности работы КДУ-прототипа (фиг.2).

На входы 6 и 7 КДУ фиг.2 подается токовый сигнал, например, от входного дифференциального каскада, показанного на чертеже фиг.4. Первый 8 и второй 9 двухполюсники нагрузки, а также первый 4 и второй 5 токостабилизирующие двухполюсники и напряжение на базах транзисторов 1 и 2 определяют статический режим КДУ, который отличается высокой нестабильностью. Например, если ток двухполюсника в 8 (9) меньше, чем статический ток коллектора транзистора 1 (2), зависящий от численных значений тока двухполюсника 4 (5), то транзистор 10 (11) закрывается (переходит в режим микротоков). В данном состоянии все основные высокочастотные усилительные параметры транзисторов деградируют, что отрицательно сказывается на частотных характеристиках аналоговых микросхем на основе КДУ фиг.2.

С другой стороны, небольшое уменьшение тока двухполюсника 8 (9) (под действием температуры или изменения напряжений питания) относительно тока коллектора транзистора 1 (2) вызывает увеличение тока базы транзистора 10 (11). Это приращение тока базы усиливается в β10 (β11) - раз транзистором 10 (11) и передается на выход сумматора 12, где β10 (β11) >>1 - коэффициент усиления тока базы транзистора 10 (11). Однако небольшое синфазное уменьшение токов двухполюсников 8 и 9 переводит транзисторы 10 и 11 в открытое состояние, что создает большой сквозной ток между шиной положительного и отрицательного источников питания по цепи «выходной усилитель тока 12 - транзистор 11». Предельная величина этого сквозного тока может достигать десятков - сотен миллиампер, что неприемлемо для большинства применений. Следовательно, схема фиг.2 требует юстировки (обеспечения высокой идентичности) токов двухполюсников 8 и 9 (4 и 5), что также неприемлемо. Таким образом, в рамках известного технического решения (фиг.2) неудовлетворительно решается задача обеспечения высокого коэффициента усиления и диапазона рабочих частот, стабильности статического режима (сквозного тока) и, как следствие, надежности КДУ и аналоговых интерфейсов на его основе.

В заявляемой схеме созданы специальные условия, допускающие повышение Ку и стабилизирующие сквозной ток выходного каскада, а также все статические токи в транзисторах схемы.

Повышение стабильности статического режима в заявляемом КДУ фиг.3 обеспечивается отрицательной обратной связью по синфазному сигналу, которая организуется транзисторами 15 и 16, а также 17 (18), 19 (20). В результате в схеме фиг.3 гарантируется высокая стабильность токов эмиттера транзисторов 15 и 16 и, как следствие, токов эмиттера параллельно включенных транзисторов 10 и 11. При этом в схеме фиг.3 обеспечивается повышение на порядок коэффициента усиления по напряжению, и основную роль в этом играют транзисторы 17, 19 и 18, 20.

Действительно, при увеличении напряжения на двухполюснике 8 и уменьшении напряжения на двухполюснике 9 в схеме фиг.3 образуются приращения токов базы iб транзисторов 10 и 15, а также 16 и 11. В результате уменьшается ток эмиттера транзистора 16 и транзисторов 17 и 19 (iэ). При этом на величину 2iб возрастает ток эмиттера и ток коллектора транзистора 1 iк≈iэ≈2iб, что обеспечивает компенсацию токов базы транзисторов 10 и 15 в цепи двухполюсника 8.

Таким образом, в схеме фиг.3 существенно возрастает эквивалентное сопротивление в цепи коллекторной нагрузки транзисторов 1 и 2, что повышает Ку более чем на порядок (фиг.5).

Компьютерное моделирование подтверждает преимущества предлагаемого технического решения (фиг.5).

Библиографический список

1. Патент США №6.304.143.

2. Патент США №5.418.491.

3. Патент США №4.463.319.

4. Патент США №6.717.474.

5. Патент США №6.734.720.

6. Патент США №4.723.111.

7. Патент США №4.293.824.

8. Патент США №5.323.121.

9. Патент США №5.091.701.

10. Патент США №4.406.990.

11. Патент США №5.422.600.

12. Патент США №6.788.143.

13. Патент США №4.274.061.

14. Патент США №5.327.100.

15. Патент США №5.786.729.

16. Патент США №3.644.838.

17. Патент США №4.600.893.

18. Патент США №4.390.850.

19. Патент США №6.628.168.

20. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - С.74, рис.4.15, стр.98, рис.6.7.

21. Патент США №6.218.900, фиг.1.

22. Патентная заявка US 2002/0196079.

23. Патент США Re 30.587.

24. Патент ЕР 1.227.580.

25. Патент США №6.714.076.

26. Патентная заявка US 2004/0090268 A1.

27. Патент США №4.959.622, фиг.1.

28. Патент США №6.018.268.

29. Патент США №5.952.882.

30. Патент США №6.580.325.

31. Патент США №6.965.266.

32. Патент США №6.867.643.

33. Патент США №6.236.270.

34. Патент США №6.229.394.

35. Патент США №5.734.296.

36. Патент США №5.477.190.

37. Патент США №6.084.475.

38. Патент США №3.733.559.

39. Патентная заявка US 2005/0001682 A1.

40. Патент США №6.300.831.

Каскодный дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, базы которых подключены к источнику напряжения смещения (3), первый (4) и второй (5) токостабилизирующие двухполюсники, связанные с соответствующими первым (6) и вторым (7) входами каскодного усилителя и эмиттерами первого (1) и второго (2) входных транзисторов, первый (8) и второй (9) двухполюсники нагрузки, подключенные к коллекторам соответствующих первого (1) и второго (2) входных транзисторов, а также базам первого (10) и второго (11) выходных транзисторов, выходной сумматор токов (12), первый (13) и второй (14) входы которого соединены с коллекторами первого (10) и второго (11) выходных транзисторов, отличающийся тем, что в схему введены первый (15), второй (16), третий (17), четвертый (18), пятый (19) и шестой (20) дополнительные транзисторы, третий (21) токостабилизирующий двухполюсник, а также первый (22) и второй (23) вспомогательные p-n переходы, причем первый (6) вход каскодного дифференциального усилителя связан с эмиттером первого (1) входного транзистора через первый (22) дополнительный p-n переход, второй (7) вход каскодного дифференциального усилителя связан с эмиттером второго (2) входного транзистора через второй (23) дополнительный p-n переход, база первого дополнительного транзистора (15) подключена к коллектору первого (1) входного транзистора, база второго дополнительного транзистора (16) подключена к коллектору второго (2) входного транзистора, коллектор первого дополнительного транзистора (15) соединен с эмиттером четвертого (17) дополнительного транзистора, коллектор второго дополнительного транзистора (16) связан с эмиттером третьего (17) дополнительного транзистора, база третьего дополнительного транзистора (17) подключена к эмиттеру первого входного транзистора (1), база четвертого (18) дополнительного транзистора подключена к эмиттеру второго (2) выходного транзистора, коллектор третьего дополнительного транзистора (17) соединен с эмиттером пятого дополнительного транзистора (19), база пятого дополнительного транзистора (19) подключена к первому входу (6) каскодного дифференциального усилителя, база шестого дополнительного транзистора (20) соединена со вторым (7) входом каскодного дифференциального усилителя, коллекторы пятого и шестого дополнительных транзисторов объединены и подключены к общей точке первого (4), второго (5) и третьего (21) токостабилизирующих двухполюсников, а свободный вывод третьего токостабилизирующего двухполюсника (21) связан с шиной источника питания (22), при этом первый (15), четвертый (18) и шестой (20) дополнительные транзисторы, а также второй (16), третий (17) и пятый (19) дополнительные транзисторы обеспечивают отрицательную обратную связь по синфазному сигналу.