Буферный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве буферного усилителя (БУ) аналоговых микросхем различного функционального назначения (например, повторителях сигналов с высоким к.п.д. и повышенным петлевым усилением). Технический результат: увеличение петлевого усиления. БУ содержит токовое зеркало (ТЗ) (1), входной дифференциальный каскад (ДК) (2) с первым (3) и вторым (4) токовыми выходами, первый (3) токовый выход входного ДК (2) связан со входом ТЗ (1), второй (4) токовый выход входного ДК (2) связан с выходом ТЗ (1) и базой составного транзистора (Т) (5), эмиттер которого соединен с выходом устройства (6) и цепью нагрузки (7). В схему введены первый (8) и второй (9) дополнительные каскады усиления на Т, включенных по схеме с общей базой, первый (3) токовый выход входного ДК (2) связан со входом ТЗ (1) через первый (8) дополнительный каскад усиления, второй (4) токовый выход входного ДК (2) связан с выходом ТЗ (1) через второй (9) дополнительный каскад усиления, причем общие выводы (10) и (11) первого (8) и второго (9) дополнительных каскадов усиления соединены друг с другом и подключены к эмиттеру выходного составного Т (5). 2 з.п. ф-лы, 9 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве буферного усилителя аналоговых интерфейсов различного функционального назначения (например, повторителях сигналов, драйверов линий связи и т.п.).

Известны схемы буферных усилителей (БУ) на основе операционных усилителей со 100% обратной связью [1-8], которые стали основой многих серийных изделий, выпускаемых как зарубежными, так и российскими микроэлектронными фирмами.

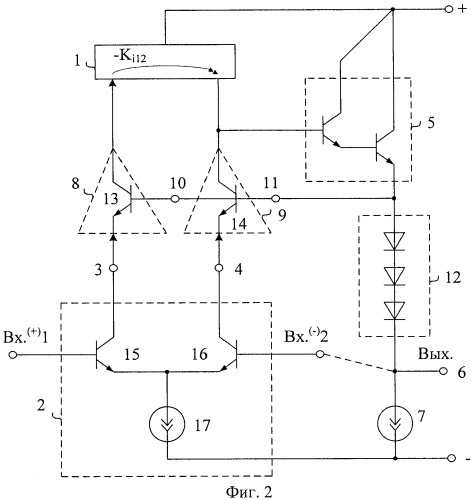

Ближайшим прототипом заявляемого устройства является буферный усилитель, описанный в патенте фирмы Motorola (США) №4.042.886 fig.1, содержащий токовое зеркало 1, входной дифференциальный каскад 2 с первым 3 и вторым 4 токовыми выходами, первый 3 токовый выход входного дифференциального каскада 2 связан со входом токового зеркала 1, второй 4 токовый выход входного дифференциального каскада 2 связан с выходом токового зеркала 1 и базой составного транзистора 5, эмиттер которого соединен с выходом устройства 6 и цепью нагрузки 7.

Существенный недостаток известного устройства состоит в том, что он характеризуется сравнительно небольшим петлевым усилением, что отрицательно сказывается на его динамических параметрах - дифференциальном выходном сопротивлении в схеме с обратной связью, динамической ошибке передачи сигнала и др. [9].

Основная цель предлагаемого изобретения состоит в увеличении петлевого усиления. Дополнительная цель - в уменьшении напряжения смещения нуля (Uсм).

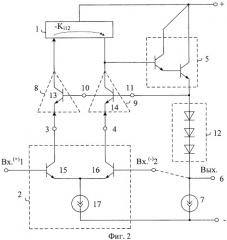

Поставленная цель достигается тем, что в известном буферном усилителе (фиг.1), содержащем токовое зеркало 1, входной дифференциальный каскад 2 с первым 3 и вторым 4 токовыми выходами, первый 3 токовый выход входного дифференциального каскада 2 связан со входом токового зеркала 1, второй 4 токовый выход входного дифференциального каскада 2 связан с выходом токового зеркала 1 и базой составного транзистора 5, эмиттер которого соединен с выходом устройства 6 и цепью нагрузки 7, предусмотрены новые элементы и связи - в схему введены первый 8 и второй 9 дополнительные каскады усиления на транзисторах по схеме с общей базой, первый 3 токовый выход входного дифференциального каскада 2 связан со входом токового зеркала 1 через первый 8 дополнительный каскад усиления на транзисторе по схеме с общей базой, второй 4 токовый выход входного дифференциального каскада 2 связан с выходом токового зеркала 1 через второй 9 дополнительный каскад усиления на транзисторе по схеме с общей базой, причем общие выводы 10 и 11 первого 8 и второго 9 дополнительных каскадов усиления на транзисторах по схеме с общей базой соединены друг с другом и подключены к эмиттеру выходного составного транзистора 5.

На фиг.1 показана схема БУ-прототипа.

На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения.

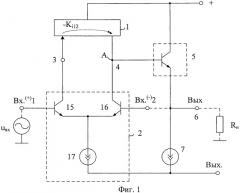

На фиг.3 показан частный случай выполнения составного транзистора 5, а также первого 8 и второго 9 дополнительных каскадов усиления на транзисторах 13 и 14 по схеме с общей базой..

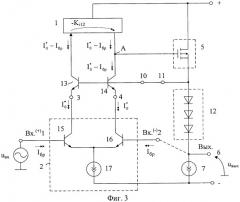

На фиг.4 показана схема фиг.2 для случая, когда входной дифференциальный каскад 2 реализован на основе «перегнутого» каскода.

На фиг.5 приведена схема БУ в соответствии с п.3 формулы изобретения.

На фиг.6 показана схема БУ-прототипа в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.7 - амплитудно-частотная характеристика его коэффициента усиления без обратной связи.

На фиг.8 показана схема заявляемого устройства в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.9 - амплитудно-частотная характеристика его коэффициента усиления без обратной связи.

Буферный усилитель (фиг.2) содержит токовое зеркало 1, входной дифференциальный каскад 2 с первым 3 и вторым 4 токовыми выходами, первый 3 токовый выход входного дифференциального каскада 2 связан со входом токового зеркала 1, второй 4 токовый выход входного дифференциального каскада 2 связан с выходом токового зеркала 1 и базой составного транзистора 5, эмиттер которого соединен с выходом устройства 6 и цепью нагрузки 7. В схему введены первый 8 и второй 9 дополнительные каскады усиления на транзисторах по схеме с общей базой, первый 3 токовый выход входного дифференциального каскада 2 связан со входом токового зеркала 1 через первый 8 дополнительный каскад усиления на транзисторе по схеме с общей базой, второй 4 токовый выход входного дифференциального каскада 2 связан с выходом токового зеркала 1 через второй 9 дополнительный каскад усиления на транзисторе по схеме с общей базой, причем общие выводы 10 и 11 первого 8 и второго 9 дополнительных каскадов усиления на транзисторах по схеме с общей базой соединены друг с другом и подключены к эмиттеру выходного составного транзистора 5.

На фиг.2, в соответствии с п.2 формулы изобретения, эмиттер выходного составного транзистора 5 соединен также с выходом устройства 6 через цепь согласования потенциалов 12.

На фиг.3 показан частный случай выполнения составного транзистора 5, а также первого 8 и второго 9 дополнительных каскадов усиления на транзисторах 13 и 14 по схеме с общей базой.

На фиг.4 показана схема (фиг.2) для случая, когда входной дифференциальный каскад 2 реализован на основе транзисторов 18-20, двухполюсников 21, 22 и выходных транзисторов 23 и 24.

На фиг.5, в соответствии с п.3 формулы изобретения, эмиттер выходного составного транзистора 5 связан с общими выводами 10 и 11 первого 8 и второго 9 дополнительных каскадов усиления на транзисторах по схеме с общей базой через вспомогательный повторитель напряжения 25, реализованный на основе элементов 26-28.

Рассмотрим причины, способствующие снижению напряжения смещения нуля Uсм схемы фиг.3.

Если принять, что ток общей эмиттерной цепи входного дифференциального каскада 2 равен 2I0, то токи выходов 3 и 4

где Iб.р - ток базы входных n-р-n-транзисторов, образующих входной дифференциальный каскад 2.

С учетом первого закона Кирхгофа можно найти токи коллектора транзисторов 13 и 14

где Iб.13(Iб.14) - ток базы транзистора 13 (14).

Поэтому сумма токов в узле «А» при коэффициенте передачи по току подсхемы 1 (например, токового зеркала Вильсона), равном единице

Учитывая, что Iб.13=Iб.14, из (4) следует, что сумма токов в узле «А» равна нулю, т.е. разностный ток Ip, являющийся причиной появления Uсм, Iр=0.

Вследствие воздействия, например, радиации, токи Iб.13 и Iб.14 изменяются в несколько раз, однако и в этом случае Ip≈0, так как изменения Iб.13 и Iб.14 одинаковы. Как следствие, это уменьшает Uсм, так как разностный ток Iр в узле «А» создает Uсм, зависящее от крутизны преобразования входного напряжения uвх ДУ (фиг.3) в выходной ток узла «А»

где rэ15=rэ16 - сопротивления эмиттерных переходов входных транзисторов дифференциального каскада 2.

Поэтому для схем (фиг.3)

где

φт≈26 мВ - температурный потенциал.

В ДУ-прототипе (фиг.1) Ip≠0 и Uсм≠0

где β5=30÷50 - коэффициент усиления по току базы транзистора 5.

Поэтому в схеме (фиг.1) систематическая составляющая Uсм получается как минимум на порядок больше (фиг.6, Uсм=534 мкВ), чем в заявляемой схеме (фиг.8, Uсм=20 мкВ).

Введение новых элементов в соответствии с формулой изобретения повышает коэффициент усиления по напряжению (без обратной связи).

Действительно, замечательной особенностью предлагаемого усилителя является повышение (более чем на порядок) коэффициента усиления БУ по напряжению Ку без обратной связи. Для БУ-прототипа (фиг.1)

где r1 - выходное сопротивление токового зеркала 1;

r4 - выходное сопротивление дифференциального каскада 2 относительно выхода 4;

Rвх.5 - эквивалентное сопротивление нагрузки Rн, приведенное к узлу «А»;

- крутизна входного дифференциального каскада 2, зависящая от сопротивлений эмиттерных переходов транзисторов 15 и 16 (rэ15, rэ16);

β5 - коэффициент усиления по току базы транзистора 5.

В связи с этим при β>50 и Rн≥1 кОм эквивалентное сопротивление Rэкв в узле «А» определяется транзисторами 15 и 16

где µ≈10-3 - коэффициент внутренней обратной связи транзистора 16.

Поэтому численные значения предельного коэффициента усиления БУ по напряжению (фиг.1)

В предлагаемом устройстве (фиг.2-5) максимально возможный коэффициент усиления Поэтому за счет минимизации влияния статического режима на разность коэффициентов внутренней обратной связи µ15-µ16 транзисторов 15 и 16 коэффициент усиления по напряжению Ky схемы фиг.2 (фиг.3-4) возрастает более чем на порядок. Действительно, компьютерное моделирование (фиг.7 и 9) показывает, что заявляемый БУ имеет более чем на 30 дБ большее усиление в схеме без обратной связи (Ky>104 или 100 дБ). Повышение Ky и, как следствие, петлевого усиления, оказывает положительное влияние на ряд динамических параметров буферного усилителя [9].

Таким образом, предлагаемое техническое решение характеризуется более высокими качественными показателями, что позволяет рекомендовать его для массового применения в архитектуре аналоговых интерфейсов (особенно в тех случаях, когда требуются десятки-сотни операционных усилителей с малой потребляемой мощностью).

Библиографический список

1. Патент США №4.042.886.

2. Патент Японии JP 10032437.

3. Патент Японии JP 2005033558.

4. Патент США №4.595.883, fig.4.

5. Патентная заявка США №2005/0063270А1, fig.2.

6. Патент США №5.166.638, fig.1.

7. Патент США №5.537.081, fig.3.

8. Патент США №6.114.904.

9. Операционные усилители с непосредственной связью каскадов / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л., 1979. - 148 с.

1. Буферный усилитель, содержащий токовое зеркало (1), входной дифференциальный каскад (2) с первым (3) и вторым (4) токовыми выходами, первый (3) токовый выход входного дифференциального каскада (2) связан со входом токового зеркала (1), второй (4) токовый выход входного дифференциального каскада (2) связан с выходом токового зеркала (1) и базой составного транзистора (5), эмиттер которого соединен с выходом устройства (6) и цепью нагрузки (7), отличающийся тем, что в схему введены первый (8) и второй (9) дополнительные каскады усиления на транзисторах по схеме с общей базой, первый (3) токовый выход входного дифференциального каскада (2) связан со входом токового зеркала (1) через первый (8) дополнительный каскад усиления на транзисторе по схеме с общей базой, второй (4) токовый выход входного дифференциального каскада (2) связан с выходом токового зеркала (1) через второй (9) дополнительный каскад усиления на транзисторе по схеме с общей базой, причем общие выводы (10) и (11) первого (8) и второго (9) дополнительных каскадов усиления на транзисторах по схеме с общей базой соединены друг с другом и подключены к эмиттеру выходного составного транзистора (5).

2. Устройство по п.1, отличающееся тем, что эмиттер выходного составного транзистора (5) соединен с выходом устройства (6) через цепь согласования потенциалов (12).

3. Устройство по п.1, отличающееся тем, что эмиттер выходного составного транзистора (5) связан с общими выводами (10) и (11) первого (8) и второго (9) дополнительных каскадов усиления на транзисторах по схеме с общей базой через вспомогательный повторитель напряжения (25).