Управляемый усилитель переменного тока

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве широкополосного усилителя, коэффициент передачи, по напряжению которого зависит от уровня сигнала управления (uy). Такие устройства применяются в структуре аналоговых микросхем различного функционального назначения, системах автоматической регулировки усиления, аналоговых перемножителях сигналов и т.д. Управляемый усилитель переменного тока (УУПТ) содержит первый (1) входной транзистор (Т), база которого соединена с основным (2) входом УУПТ, второй (3) входной Т, база которого соединена с управляющим входом (4) УУПТ, двухполюсник (5) местной отрицательной обратной связи (ООС), включенный между эмиттерами первого (1) и второго (3) Т, цепь нагрузки (6), связанную с коллектором первого (1) и второго (3) Т и выходом (7) УУПТ, первый (8) блокирующий конденсатор, включенный по переменному току между эмиттером первого (1) Т и общей шиной (9) источников питания (ИП), первый (10) стабилизатор тока, связанный с эмиттером первого (1) Т, второй (11) стабилизатор тока, соединенный с эмиттером второго (3) Т, второй блокирующий конденсатор (12). В схему введены первый (13) и второй (14) дополнительные Т, эмиттеры которых соединены друг с другом через дополнительный двухполюсник (15) ООС и подключены к соответствующим первому (16) и второму (17) стабилизаторам тока, база первого (13) дополнительного Т соединена с управляющим входом (4) УУПТ, база второго 14 дополнительного транзистора связана с общей шиной (9) ИП, причем первый (10) стабилизатор тока выполнен в виде управляемого стабилизатора тока, имеющего неинвертирующий вход (18), а второй (12) блокирующий конденсатор включен между эмиттером второго (14) дополнительного Т и неинвертирующим входом (18) первого (10) стабилизатора тока. 7 ил.

Реферат

Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в качестве усилителя переменного тока, коэффициент передачи по напряжению которого Кu зависит от уровня сигнала управления (uу). Такие устройства применяются в структуре аналоговых микросхем различного функционального назначения, системах автоматической регулировки усиления, аналоговых перемножителях сигналов и т.п.

В современных адаптивных СФ-блоках систем связи и телекоммуникаций широко используется в качестве управляемого усилителя классический дифференциальный каскад с резистором местной отрицательной обратной связи. При этом на его основе выполняются разные модификации управляемых усилителей [1-26].

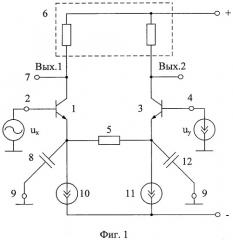

Наиболее близким по технической сущности к заявляемому устройству относится управляемый дифференциальный каскад, описанный в патенте США №5.126.586, фиг.1. Он содержит первый 1 входной транзистор, база которого соединена с основным 2 входом управляемого усилителя, второй 3 входной транзистор, база которого соединена с управляющим входом 4 управляемого усилителя, двухполюсник 5 местной отрицательной обратной связи, включенный между эмиттерами первого 1 и второго 3 входных транзисторов, цепь нагрузки 6, связанную с коллектором первого 1 и второго 3 входных транзисторов и выходом 7 управляемого усилителя, первый 8 блокирующий конденсатор, включенный по переменному току между эмиттером первого 1 входного транзистора и общей шиной 9 источников питания, первый 10 стабилизатор тока, связанный с эмиттером первого 1 входного транзистора, второй 11 стабилизатор тока, соединенный с эмиттером второго 3 входного транзистора, второй блокирующий конденсатор 12.

Существенный недостаток известного управляемого усилителя (УУ) состоит в том, что в нем не обеспечивается эффективное подавление сигнала управления ни на низких, ни на высоких частотах. Это не позволяет выполнять на его основе различные функциональные узлы современных систем связи, для которых характерно одно из важнейших требований - отсутствие гармонических составляющих сигнала управления uу на выходе.

Основная цель предлагаемого изобретения состоит в повышении на несколько порядков коэффициента подавления сигнала управления в широком диапазоне частот.

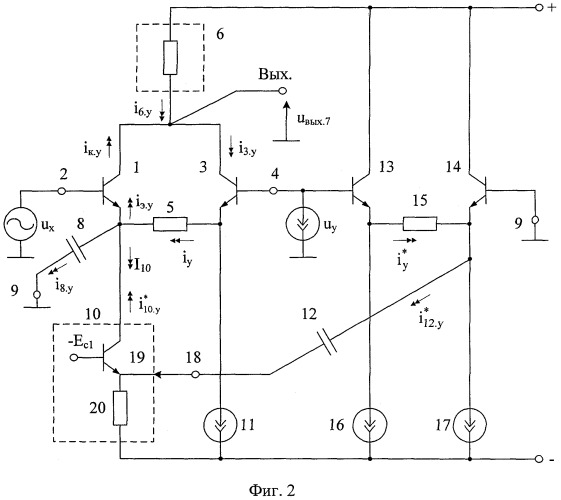

Поставленная цель достигается тем, что в управляемом усилителе переменного тока (фиг.1), содержащем первый 1 входной транзистор, база которого соединена с основным 2 входом управляемого усилителя, второй 3 входной транзистор, база которого соединена с управляющим входом 4 управляемого усилителя, двухполюсник 5 местной отрицательной обратной связи, включенный между эмиттерами первого 1 и второго 3 входных транзисторов, цепь нагрузки 6, связанную с коллектором первого 1 и второго 3 входных транзисторов и выходом 7 управляемого усилителя, первый 8 блокирующий конденсатор, включенный по переменному току между эмиттером первого 1 входного транзистора и общей шиной 9 источников питания, первый 10 стабилизатор тока, связанный с эмиттером первого 1 входного транзистора, второй 11 стабилизатор тока, соединенный с эмиттером второго 3 входного транзистора, второй блокирующий конденсатор 12, предусмотрены новые элементы и связи - в схему введены первый 13 и второй 14 дополнительные транзисторы, эмиттеры которых соединены друг с другом через дополнительный двухполюсник 15 отрицательной обратной связи и подключены к соответствующим первому 16 и второму 17 дополнительным стабилизаторам тока, база первого 13 дополнительного транзистора соединена с управляющим входом 4 управляемого усилителя, база второго 14 дополнительного транзистора связана с общей шиной 9 источников питания, причем первый 10 стабилизатор тока выполнен в виде управляемого стабилизатора тока, имеющего неинвертирующий вход 18, а второй 12 блокирующий конденсатор включен между эмиттером второго 14 дополнительного транзистора и неинвертирующим входом 18 первого 10 стабилизатора тока.

На фиг.1 показана схема УУ-прототипа, а на фиг.2 - схема заявляемого УУ в соответствии с формулой изобретения.

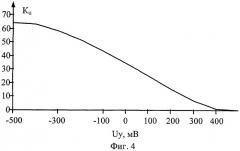

На фиг.3 приведена схема УУ фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». Результаты ее моделирования показаны на фиг.4 - 7:

- зависимость коэффициента усиления по напряжению Кu от напряжения управления Uy (фиг.4) в диапазоне средних частот;

- зависимость коэффициента усиления по напряжению Кu от частоты при разных значениях напряжения управления Uy (фиг.5);

- зависимость выходного синусоидального напряжения УУ от времени при разных значениях переменного управляющего напряжения uy=Uysinωyt;

- зависимость коэффициента подавления напряжения управления (Kп=uвых/uу) от частоты.

Управляемый усилитель переменного тока (фиг.2) содержит первый 1 входной транзистор, база которого соединена с основным 2 входом управляемого усилителя, второй 3 входной транзистор, база которого соединена с управляющим входом 4 управляемого усилителя, двухполюсник 5 местной отрицательной обратной связи, включенный между эмиттерами первого 1 и второго 3 входных транзисторов, цепь нагрузки 6, связанную с коллектором первого 1 и второго 3 входных транзисторов и выходом 7 управляемого усилителя, первый 8 блокирующий конденсатор, включенный по переменному току между эмиттером первого 1 входного транзистора и общей шиной 9 источников питания, первый 10 стабилизатор тока, связанный с эмиттером первого 1 входного транзистора, второй 11 стабилизатор тока, соединенный с эмиттером второго 3 входного транзистора, второй блокирующий конденсатор 12. В схему введены первый 13 и второй 14 дополнительные транзисторы, эмиттеры которых соединены друг с другом через дополнительный двухполюсник 15 отрицательной обратной связи и подключены к соответствующим первому 16 и второму 17 дополнительным стабилизаторам тока, база первого 13 дополнительного транзистора соединена с управляющим входом 4 управляемого усилителя, база второго 14 дополнительного транзистора связана с общей шиной 9 источников питания, причем первый 10 стабилизатор тока выполнен в виде управляемого стабилизатора тока, имеющего неинвертирующий вход 18, а второй 12 блокирующий конденсатор включен между эмиттером второго 14 дополнительного транзистора и неинвертирующим входом 18 первого 10 стабилизатора тока. В частном случае стабилизатор тока 10 выполнен на транзисторе 19 и резисторе 20.

Рассмотрим работу управляемого усилителя (фиг.2).

В диапазоне средних частот усиление сигнала uх по основному входу 2 при uy=0 обеспечивается транзистором 1, включенном по традиционной

схеме с общим эмиттером:

где Rн.экв - эквивалентное сопротивление цепи нагрузки 6;

φт≈25 мВ - температурный потенциал;

I10 - статический ток эмиттера транзистора 1;

rэ1=φт/I10 - сопротивление эмиттерного перехода транзистора 1.

Если напряжение Uy на управляющем входе 4 и изменяется на величину uу, то при этом изменяется и ток через двухполюсник 5:

где R5 - сопротивление двухполюсника 5.

На очень низких частотах (fy<<fx) приращении тока iy полностью поступает в эмиттер транзистора 1, и далее - в цепь нагрузки 6. Как следствие, при медленных изменениях uу в нагрузке 6 обеспечивается полная компенсация близких по величине токов i3.y и iк.y, «порождаемых» сигналами управления uу:

Поэтому в схеме фиг.2 при медленных изменениях uу обеспечивается высокий уровень подавления сигнала управления uу, что является одним из необходимых условий построения на ее основе высококачественных управляемых усилителей, модуляторов, аналоговых перемножителей и т.п. Однако с повышением частоты ωу сигнала управления (uy=Uysinωyt) не все приращение iy полностью передается в эмиттер транзистора 1 - часть этого тока i8.y «ответвляется» в блокирующий конденсатор 8. Как следствие, второе слагаемое в уравнении (3) уменьшается, что ухудшает подавление сигнала управления uу в выходной цепи.

В заявляемом устройстве за счет новых элементов и связей между ними в эмиттерную цепь транзистора 1 добавляется ток , близкий по величине току i8.y, причем

где Ki10≈1 - коэффициент передачи тока стабилизатора тока 10 по входу 18.

Если учесть, что при одинаковых сопротивлениях двухполюсников 5 и 15, одинаковых конденсаторах 8 и 12, а также в единичном усилении Ki10=1 выполняется равенство , то на основании первого закона Кирхгофа для эмиттерной цепи транзистора 1 можно получить, что комплекс тока эмиттера

Следовательно, ток в резисторе нагрузки 6, обусловленный напряжением uу, близок к нулю

i6.у=iк.у-i3.у≈0.

Таким образом, в схеме фиг.2 компенсируется частотная зависимость коэффициента подавления сигнала управления Кп, который остается достаточно малым в более широком диапазоне частот, чем в схеме фиг.1.

Данный теоретический вывод подтверждается результатами компьютерного моделирования схемы фиг.2, показанными на фиг.7.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патентная заявка США №2004/0183599.

2. Патентная заявка США №2004/0178850.

3. Патентная заявка США №2006/0044064.

4. Патентная заявка США №2008/0088374.

5. Патент США №4.575.687.

6. Патентная заявка США №2005/0179493.

7. Патент США №6.456.142.

8. Патент США №5.184.088.

9. Патент США №6.703.899.

10. Патентная заявка США №2008/0191803.

11. Патент США №6.525.606, фиг.6.

12. Патент США №6.980.054, фиг.4.

13. Патент США №6.980.053.

14. Патентная заявка США №2005/0258900.

15. Патентная заявка США №2003/0011429.

16. Патент США №6.972.625.

17. Патентная заявка США №2006/0022748.

18. Патент США №5.157.360.

19. Патентная заявка США №2005/0038615.

20. Патент GB 2.318.470.

21. Патент США №5.126.586.

22. Патент США 4.511.852.

23. Патент США 4.881.043.

24. Патент США №6.891.436, фиг.1.

25. Патент США №6.933.783, фиг.20, 21.

26. Патент США №4.267.518.

Управляемый усилитель переменного тока, содержащий первый (1) входной транзистор, база которого соединена с основным (2) входом управляемого усилителя, второй (3) входной транзистор, база которого соединена с управляющим входом (4) управляемого усилителя, двухполюсник (5) местной отрицательной обратной связи, включенный между эмиттерами первого (1) и второго (3) входных транзисторов, цепь нагрузки (6), связанную с коллектором первого (1) и второго (3) входных транзисторов и выходом (7) управляемого усилителя, первый (8) блокирующий конденсатор, включенный по переменному току между эмиттером первого (1) входного транзистора и общей шиной (9) источников питания, первый (10) стабилизатор тока, связанный с эмиттером первого (1) входного транзистора, второй (11) стабилизатор тока, соединенный с эмиттером второго (3) входного транзистора, второй блокирующий конденсатор (12), отличающийся тем, что в схему введены первый (13) и второй (14) дополнительные транзисторы, эмиттеры которых соединены друг с другом через дополнительный двухполюсник (15) отрицательной обратной связи и подключены к соответствующим первому (16) и второму (17) дополнительным стабилизаторам тока, база первого (13) дополнительного транзистора соединена с управляющим входом (4) управляемого усилителя, база второго (14) дополнительного транзистора связана с общей шиной (9) источников питания, причем первый (10) стабилизатор тока выполнен в виде управляемого стабилизатора тока, имеющего неинвертирующий вход (18), а второй (12) блокирующий конденсатор включен между эмиттером второго (14) дополнительного транзистора и неинвертирующим входом (18) первого (10) стабилизатора тока.