Операционный усилитель с малым напряжением смещения нуля

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в решающих усилителях (ОУ) с малыми значениями напряжения смещения нуля UСМ в условиях воздействия радиации или температуры). Технический результат: уменьшение напряжения смещения нуля. ОУ содержит входной дифференциальный каскад (ДК) (1), имеющий первый (2) и второй (3) токовые выходы, p-n переход активной нагрузки (4), связанный с базами первого (5) и второго (6) выходных транзисторов (Т), третий (7) выходной Т, база которого связана со вторым (3) токовым выходом ДК (1) и коллектором первого (5) выходного Т, а коллектор соединен с выходом первого токового зеркала (8) и цепью нагрузки (9). Коллектор второго (6) выходного Т соединен с эмиттером дополнительного Т (10), база дополнительного Т (10) соединена со входом дополнительного токового зеркала (11), коллектор подключен ко входу первого (8) токового зеркала, а выход дополнительного токового зеркала (11) соединен с первым (2) выходом ДК 1. 1 з.п. ф-лы, 5 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функциональною назначения (например, в решающих усилителях с малыми значениями напряжения смещения нуля Uсм в условиях воздействия радиации или температуры).

В структуре аналоговых интерфейсов различного назначения находят широкое применение операционные усилители (ОУ), характеризующиеся двухканальной передачей выходных токов входного дифференциального каскада на вход буферного усилителя [1-8]. Их основное достоинство - исключение нелинейных режимов промежуточного каскада, что способствует повышению быстродействия в схемах с нелинейной коррекцией [7, 8]. Следует отметить, что по такой архитектуре выполняются ОУ как на биполярных [2, 4, 6], так и на полевых [1, 3] транзисторах.

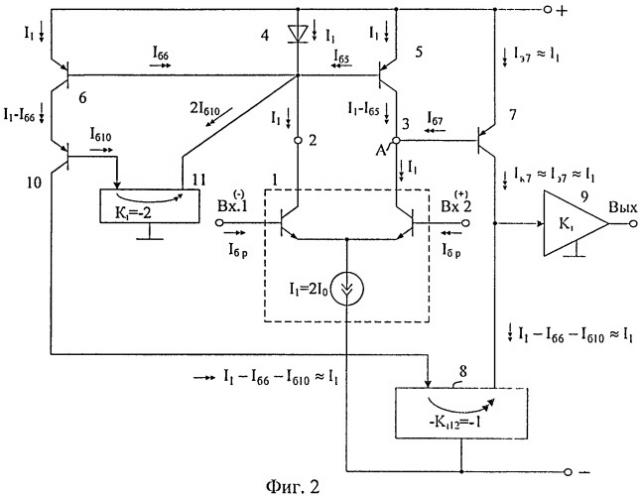

Наиболее близкой по технической сущности к заявляемому устройству является классическая схема ОУ фиг.1, представленная в патенте США №5.512.857 фиг.3, которая стала основой построения различных аналоговых устройств, например [1-8].

Существенный недостаток ОУ-прототипа состоит в повышенном напряжении смещения нуля Uсм, что обусловлено свойствами его архитектуры.

Основная цель предлагаемого изобретения состоит в уменьшении систематической составляющей напряжения смещения нуля Uсм.

Поставленная цель достигается тем, что в операционном усилителе фиг.1, содержащем входной дифференциальный каскад 1, имеющий первый 2 и второй 3 токовые выходы, p-n переход активной нагрузки 4, связанный с базами первого 5 и второго 6 выходных транзисторов, третий 7 выходной транзистор, база которого связана со вторым 3 токовым выходом входного дифференциального каскада 1 и коллектором первого 5 выходного транзистора, а коллектор соединен с выходом первого токового зеркала 8 и цепью нагрузки 9, предусмотрены новые элементы и связи - коллектор второго 6 выходного транзистора соединен с эмиттером дополнительного транзистора 10, база дополнительного транзистора 10 соединена со входом дополнительного токового зеркала 11, коллектор подключен ко входу первого 8 токового зеркала, а выход дополнительного токового зеркала 11 соединен с первым 2 выходом входного дифференциального каскада 1.

Схема усилителя-прототипа показана на фиг.1.

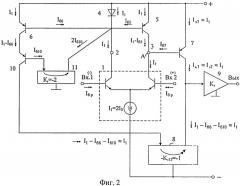

На фиг.2 представлена схема заявляемого устройства в соответствии с формулой изобретения.

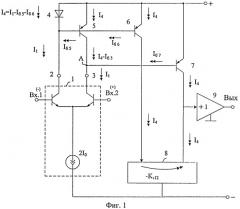

На фиг.3 представлена схема фиг.1 в среде компьютерного моделирования PSpice па моделях интегральных транзисторов ФГУП НЛП «Пульсар».

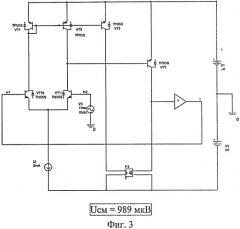

На фиг.4 представлена схема фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.5 представлены графики температурной зависимости Uсм ОУ-прототипа (фиг.3) и заявляемого ОУ (фиг.4), полученные в результате моделирования сравниваемых схем.

Операционный усилитель фиг.2 содержит входной дифференциальный каскад 1, имеющий первый 2 и второй 3 токовые выходы, p-n переход активной нагрузки 4, связанный с базами первого 5 и второго 6 выходных транзисторов, третий 7 выходной транзистор, база которого связана со вторым 3 токовым выходом входного дифференциального каскада 1 и коллектором первого 5 выходного транзистора, а коллектор соединен с выходом первого токового зеркала 8 и цепью нагрузки 9. Коллектор второго 6 выходного транзистора соединен с эмиттером дополнительного транзистора 10, база дополнительного транзистора 10 соединена со входом дополнительного токового зеркала 11, коллектор подключен ко входу первого 8 токового зеркала, а выход дополнительного токового зеркала 11 соединен с первым 2 выходом входного дифференциального каскада 1.

На фиг.2, в соответствии с п.2 формулы изобретения, коэффициент передачи по току первого токового зеркала 8 выбран близким к единице, а коэффициент передачи по току дополнительного токового зеркала 11 - близким к двум.

Рассмотрим работу схемы фиг.2 на постоянном токе.

Если принять, что ток общей эмиттерной цепи входного дифференциального каскада 1 равен 2I0, то токи выходов 2 и 3

где Iб.р - ток базы входных n-p-n транзисторов, образующих входной дифференциальный каскад 1.

С учетом первого закона Кирхгофа можно найти ток через р-n переход 4:

где Iб.i - ток базы i-го транзистора;

Ki - коэффициент передачи по току дополнительного токового зеркала 11.

Если выбрать Ki=2 и учесть, что токи эмиттера Iэi транзисторов 5 и 6 равны току через p-n переход 4, а коэффициент усиления по току базы β транзисторов 6, 10, 5 и 7 одинаковы (β6=β10=β5=β7=β), то из (3) можно найти, что

Поэтому сумма токов в узле «A» близка к нулю

.

Вследствие воздействия, например, радиации или температуры токи Iб.7 и Iб.5 изменяются в несколько раз, однако и в этом случае Ip≈0, так как изменения Iб.7 и Iб.5 одинаковы. Как следствие, это уменьшает Uсм, так как разностный ток Ip в узле «A» создает Uсм, зависящее от крутизны преобразования входного напряжения uвх ОУ фиг.2 в выходной ток узла «A»

где rэ1=rэ2 - сопротивления эмиттерных переходов входных транзисторов дифференциального каскада 1.

Поэтому для схемы фиг.2

где ;

φт - температурный потенциал.

В ОУ-прототипе фиг.1 разностный ток Iр≠0:

Ip=-2Iб.5-Iб.6+Iб.7≈-2Iб.5

или

где β5 - коэффициент усиления по току базы транзистора 5.

Как следствие напряжение смещения нуля

Если β=100, то Uсм≈1 мВ, поэтому здесь систематическая составляющая Uсм получается как минимум на порядок больше (фиг.3, Uсм=989 мкВ), чем в заявляемой схеме (фиг.4, Uсм=84 мкВ). Компьютерное моделирование (фиг.5) подтверждает данные выводы.

Таким образом, заявляемое устройство имеет существенное преимущество в сравнении с прототипом по статической точности.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №6.150.884.

2. Патент США №5.512.857, фиг.3.

3. Патентная заявка Японии JP 2002/043870.

4. А.св. СССР №614528, фиг.2.

5. Патент Японии JP 7-74554.

6. А.св. СССР №1396242, фиг.1.

7. Операционные усилители с непосредственной связью каскадов [Текст]. / Анисимов В.И., Капитонов М.В., Прокопенко П.П., Соколов Ю.М. - Л., 1979. - С.143. - Рис.3-37.

8. Маломощные быстродействующие операционные усилители [Текст]. / Анисимов В.И., Капитонов М.В., Прокопенко П.П., Соколов Ю.М., Югай В. // Активные избирательные системы: Межвузовский научно-технический сборник. - Таганрог: ТРТИ, 1978. - №4.

1. Операционный усилитель с малым напряжением смещения нуля, содержащий входной дифференциальный каскад (1), имеющий первый (2) и второй (3) токовые выходы, р-n переход активной нагрузки (4), связанный с базами первого (5) и второго (6) выходных транзисторов, третий (7) выходной транзистор, база которого связана со вторым (3) токовым выходом входного дифференциального каскада (1) и коллектором первого (5) выходного транзистора, а коллектор соединен с выходом первого токового зеркала (8) и цепью нагрузки (9), отличающийся тем, что коллектор второго (6) выходного транзистора соединен с эмиттером дополнительного транзистора (10), база дополнительного транзистора (10) соединена со входом дополнительного токового зеркала (11), коллектор подключен ко входу первого (8) токового зеркала, а выход дополнительного токового зеркала (11) соединен с первым (2) выходом входного дифференциального каскада (1).

2. Устройство по п.1, отличающееся тем, что коэффициент передачи по току первого токового зеркала (8) близок к единице, а коэффициент передачи по току дополнительного токового зеркала (11) близок к двум.