Двухтактный самосинхронный rs-триггер с предустановкой

Иллюстрации

Показать всеИзобретение относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации. Достигаемый технический результат - обеспечение реализации синхронной и самосинхронной предустановки в двухтактном самосинхронном RS-триггере с парафазным информационным входом со спейсером. Устройство содержит блок памяти и блок индикации. Устройство в зависимости от типа спейсера парафазного информационного входа выполнено на элементах И-ИЛИ-НЕ или ИЛИ-И-НЕ. 11 з.п. ф-лы, 12 ил.

Реферат

Двухтактный самосинхронный RS-триггер с предустановкой относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации.

Известен RS-триггер [1], содержащий два элемента ИЛИ-НЕ.

Недостаток известного устройства - отсутствие средств начальной установки и индикации окончания переходных процессов.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является двухтактный самосинхронный RS-триггер [2], содержащий блок памяти на двух бистабильных ячейках, индикаторный элемент, парафазный информационный вход, первый и второй информационные выходы и индикаторный выход.

Недостаток прототипа - отсутствие предустановки, что не позволяет обеспечить его начальную установку в определенное состояние и индикацию окончания предустановки, также невозможность его использования для работы с парафазным со спейсером информационным входным сигналом. Под предустановкой понимается процедура предварительного сброса прямого выхода триггера в состояние логического нуля или предварительной установки его в состояние логической единицы.

Задача, решаемая в изобретении, заключается в обеспечении синхронной и самосинхронной реализации предустановки двухтактного самосинхронного RS-триггера с парафазным информационным входом со спейсером.

Это достигается тем, что в двухтактный самосинхронный RS-триггер с парафазным информационным входом, содержащий блок памяти, блок индикации, первую и вторую составляющие парафазного информационного входа, первый и второй информационные выходы и индикаторный выход, причем первая составляющая парафазного информационного входа соединена с первыми входами блоков памяти и индикации, вторая составляющая парафазного информационного входа соединена со вторыми входами блоков памяти и индикации, первый информационный выход подключен к первому выходу блока памяти и третьему входу блока индикации, второй информационный выход подключен ко второму выходу блока памяти и четвертому входу блока индикации, третий и четвертый выходы блока памяти соединены с пятым и шестым входами блока индикации соответственно, индикаторный выход триггера соединен с выходом блока индикации, введены вход предустановки триггера, третий вход блока памяти и седьмой вход блока индикации, вход предустановки триггера соединен с третьим входом блока памяти и седьмым входом блока индикации, а в качестве информационного входа используется парафазный вход со спейсером.

Предлагаемое устройство удовлетворяет критерию "существенные отличия". Использование входа предустановки в синхронных триггерах известно. Однако использование его в самосинхронном RS-триггере с учетом специфики работы самосинхронных устройств позволило достичь эффекта, выраженного целью изобретения. Существенное отличие предлагаемой реализации предустановки от аналогичных решений в синхронной схемотехнике заключается в том, что в данном случае для успешной предустановки парафазный информационный вход должен находиться в спейсерном состоянии (обе составляющие парафазного входа имеют одинаковое значение). Это позволяет упростить предустановку и обеспечить ее самосинхронность при использовании дополнительного элемента фиксации окончания предустановки, как описано ниже.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, устройство может считаться имеющим существенные отличия.

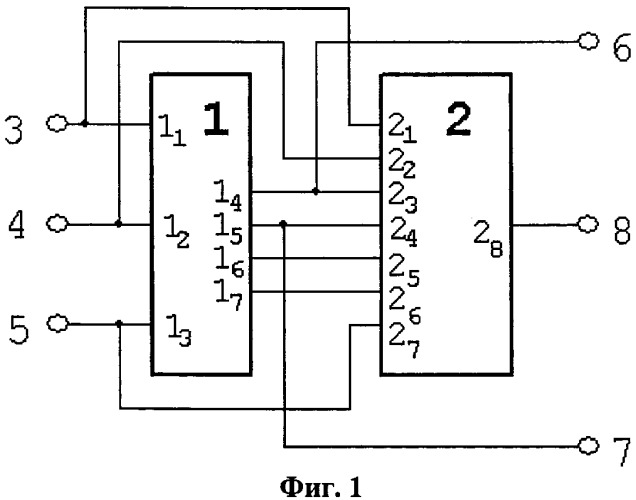

На фиг.1 изображена схема двухтактного самосинхронного RS-триггера с предустановкой и парафазным информационным входом со спейсером. Схема содержит блок памяти 1, блок индикации 2, первую 3 и вторую 4 составляющие парафазного информационного входа со спейсером, вход предустановки 5, первый 6 и второй 7 информационные выходы, индикаторный выход 8, первая 3 составляющая парафазного информационного входа со спейсером соединена с первым 11 входом блока памяти 1 и с первым 21 входом блока индикации 2, вторая 4 составляющая парафазного информационного входа со спейсером соединена со вторым 12 входом блока памяти 1 и со вторым 22 входом блока индикации 2, первый 14 выход блока памяти 1 подключен к третьему 23 входу блока индикации 2 и первому 6 информационному выходу триггера, второй 15 выход блока памяти 1 подключен к четвертому 24 входу блока индикации 2 и второму 7 информационному выходу триггера, третий 16 и четвертый 17 выходы блока памяти 1 соединены с пятым 25 и шестым 26 входами блока индикации 2 соответственно, вход предустановки 5 соединен с третьим входом 13 блока памяти 1 и седьмым входом 27 блока индикации 2, выход 28 блока индикации 2 подключен к первому индикаторному выходу 8 триггера.

Схема работает следующим образом. Установка начального состояния происходит при спейсерном состоянии парафазного информационного входа 3, 4 триггера, обеспечивающем хранение информации в первой (входной) бистабильной ячейке блока памяти и перезапись состояния первой бистабильной ячейки во вторую бистабильную ячейку блока памяти, подачей активного уровня на вход предустановки 5. В результате сначала второй информационный выход 7 триггера переключается в требуемое состояние, а затем - первый информационный выход 6. Наличие спейсерного состояния на парафазном информационном входе требуется для обеспечения неизменного состояния на индикаторном выходе 8 в процессе предустановки, что является необходимым условием правильного функционирования самосинхронного триггера, а также для успешной записи начального состояния в обе бистабильные ячейки блока памяти. Конкретные значения спейсерного состоянии парафазного информационного входа 3, 4 триггера и входа предустановки 5, обеспечивающие предустановку, определяются базисом реализации триггера и раскрываются ниже.

Особенности данной схемы по сравнению с прототипом следующие.

Триггер имеет вход предустановки, позволяющий установить триггер в определенное состояние и создающий предпосылки для построения схемы индикации окончания предустановки самосинхронного триггера.

Таким образом, предлагаемое устройство обеспечивает предустановку двухтактного самосинхронного RS-триггера с парафазным информационным входом со спейсером. Цель изобретения достигнута.

Конкретная техническая реализация предлагаемого двухтактного самосинхронного RS-триггера с синхронной предустановкой и парафазным информационным входом со спейсером и его составных блоков зависит от типа спейсера парафазного информационного входа: высокий или низкий уровень его составляющих обеспечивает хранение состояния триггера, - и от типа предустановки триггера. Тип спейсера влияет на базис реализации бистабильных ячеек блока памяти: И-ИЛИ-НЕ или ИЛИ-И-НЕ, - и элемента фиксации окончания предустановки в вариантах с самосинхронной предустановкой: И-НЕ или ИЛИ-НЕ. Тип предустановки в совокупности с типом спейсера определяет спецификацию первой и второй составляющих парафазного информационного входа и первого и второго информационных выходов триггера.

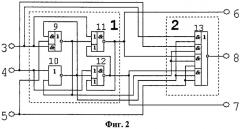

На фиг.2 представлена реализация двухтактного самосинхронного RS-триггера с синхронной предустановкой и нулевым спейсером парафазного информационного входа. Схема отличается от схемы на фиг.1 тем, что блок памяти 1 реализован на первом 9 элементе И-ИЛИ-НЕ, на элементе ИЛИ-НЕ 10 и первом 11 и втором 12 элементах ИЛИ-И-НЕ, блок индикации 2 реализован на втором элементе И-ИЛИ-НЕ 13, вход второй группы входов И первого элемента И-ИЛИ-НЕ 9 и первый вход элемента ИЛИ-НЕ 10 подключены к первому и второму входам блока памяти 1 соответственно, первые входы первых групп входов ИЛИ первого 11 и второго 12 элементов ИЛИ-И-НЕ соединены с первым и вторым входами блока памяти 1 соответственно, второй вход первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ 11 подключен к выходу первого элемента И-ИЛИ-НЕ 9, второму входу элемента ИЛИ-НЕ 10 и к третьему выходу блока памяти 1, второй вход первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ 12 подключен к выходу элемента ИЛИ-НЕ 10, первому входу первой группы входов И первого элемента И-ИЛИ-НЕ 9 и четвертому выходу блока памяти 1, выход первого элемента ИЛИ-И-НЕ 11 подключен к входу второй группы входов ИЛИ второго элемента ИЛИ-И-НЕ 12 и к первому выходу блока памяти 1, выход второго элемента ИЛИ-И-НЕ 12 подключен к входу второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ 11 и второму выходу блока памяти 1, второй вход первой группы входов И первого элемента И-ИЛИ-НЕ 9 подключен к третьему входу блока памяти 1, первые входы первой и второй групп входов И второго элемента И-ИЛИ-НЕ 13 соединены с первым и вторым входами блока индикации 2 соответственно, первые входы третьей и четвертой групп входов И второго элемента И-ИЛИ-НЕ 13 подключены к третьему и четвертому входам блока индикации 2 соответственно, вторые входы первой и четвертой групп входов И второго элемента И-ИЛИ-НЕ 13 соединены с шестым входом блока индикации 2, вторые входы второй и третьей групп входов И второго элемента И-ИЛИ-НЕ 13 подключены к пятому входу блока индикации 2, третьи входы третьей и четвертой групп входов И второго элемента И-ИЛИ-НЕ 13 соединены с седьмым входом блока индикации 2, выход второго элемента И-ИЛИ-НЕ 13 является выходом блока индикации 2.

Схема работает следующим образом. При высоком уровне сигнала на входе предустановки 5 триггер воспринимает и запоминает рабочее состояние парафазного информационного входа со спейсером 3, 4 - (0,1) или (1,0), - в бистабильной ячейке первого каскада на элементах 9 и 10, а окончание запоминания нового состояния фиксируется блоком индикации 2 на элементе 13, выход которого (и соответственно - индикаторный выход 8) переключается в логический 0 только после окончания переключения элементов 9 и 10. При этом входы второй бистабильной ячейки на элементах 11 и 12 блокированы рабочим состоянием парафазного информационного входа со спейсером 3, 4. Переход в спейсер парафазного информационного входа (логический 0 на обеих его составляющих) обеспечивает хранение информации на выходах бистабильной ячейки первого каскада и разрешает перезапись этого состояния в бистабильную ячейку второго каскада на элементах 11 и 12, выходы которых подключены к первому 6 и второму 7 информационным выходам триггера соответственно. Окончание перезаписи информации в бистабильную ячейку второго каскада разрешает переключение выхода индикаторного элемента 13 (и соответственно - индикаторного выхода 8) в высокий уровень (логическую 1), индицируя тем самым завершение обновления состояния первого 6 и второго 7 информационных выходов триггера.

Предустановка осуществляется после подтверждения перезаписи информации в бистабильную ячейку второго каскада (появление высокого уровня на индикаторном выходе 8) подачей на вход предустановки 5 низкого уровня при поддержке также низкого (спейсерного) уровня и на обеих составляющих парафазного информационного входа со спейсером 3, 4. При этом элемент 9 переключается в логическую 1, заставляя элемент 10 перейти в состояние логического 0, что, в свою очередь, инициирует переключение элемента 12 в логическую 1, а вслед за этим и переключение элемента 11 в логический 0, завершая тем самым предустановку. На первом информационном выходе 6 триггера формируется низкий уровень. При этом выход индикаторного элемента 13 (и соответственно - индикаторный выход 8) не изменяется на всем протяжении установки, поскольку его группы входов блокированы спейсерным состоянием парафазного информационного входа 3, 4 и низким уровнем на входе предустановки 5. По окончании предустановки на вход предустановки 5 подается высокий уровень, и схема триггера снова готова к продолжению работы.

В схеме на фиг.2 возможны два варианта спецификации входов и выходов триггера:

1) вход предустановки является входом установки нуля, первая и вторая составляющие парафазного информационного входа со спейсером являются соответственно прямой и инверсной информационными составляющими, а первый и второй информационные выходы триггера являются прямым и инверсным информационными выходами соответственно,

2) вход предустановки является входом установки единицы, первая и вторая составляющие парафазного информационного входа со спейсером являются соответственно инверсной и прямой информационными составляющими, а первый и второй информационные выходы триггера являются инверсным и прямым информационными выходами соответственно.

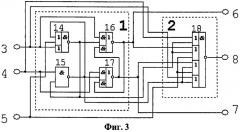

На фиг.3 представлена реализация двухтактного самосинхронного RS-триггера с синхронной предустановкой и единичным спейсером парафазного информационного входа. Схема отличается от схемы на фиг.1 тем, что блок памяти 1 реализован на первом элементе ИЛИ-И-НЕ 14, элементе И-НЕ 15 и первом 16 и втором 17 элементах И-ИЛИ-НЕ, блок индикации 2 реализован на втором элементе ИЛИ-И-НЕ 18, вход второй группы входов ИЛИ первого элемента ИЛИ-И-НЕ 14 и первый вход элемента И-НЕ 15 подключены к первому и второму входам блока памяти 1 соответственно, первые входы первых групп входов И первого 16 и второго 17 элементов И-ИЛИ-НЕ соединены с первым и вторым входами блока памяти 1 соответственно, второй вход первой группы входов И первого элемента И-ИЛИ-НЕ 16 подключен к выходу первого элемента ИЛИ-И-НЕ 14, второму входу элемента И-НЕ 15 и к третьему выходу блока памяти 1, второй вход первой группы входов И второго элемента И-ИЛИ-НЕ 17 подключен к выходу элемента И-НЕ 15, первому входу первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ 14 и четвертому выходу блока памяти 1, выход первого элемента И-ИЛИ-НЕ 16 подключен к входу второй группы входов И второго элемента И-ИЛИ-НЕ 17 и к первому выходу блока памяти 1, выход второго элемента И-ИЛИ-НЕ 17 подключен к входу второй группы входов И первого элемента И-ИЛИ-НЕ 16 и второму выходу блока памяти 1, второй вход первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ 14 подключен к третьему входу блока памяти 1, первые входы первой и четвертой групп входов ИЛИ второго элемента ИЛИ-И-НЕ 18 соединены со вторым и первым входами блока индикации 2 соответственно, первые входы второй и третьей групп входов ИЛИ второго элемента ИЛИ-И-НЕ 18 подключены к третьему и четвертому входам блока индикации 2 соответственно, вторые входы первой и второй групп входов ИЛИ второго элемента ИЛИ-И-НЕ 18 соединены с пятым входом блока индикации 2, вторые входы третьей и четвертой групп входов ИЛИ второго элемента ИЛИ-И-НЕ 18 подключены к шестому входу блока индикации 2, третьи входы второй и третьей групп входов ИЛИ второго элемента ИЛИ-И-НЕ 18 соединены с седьмым входом блока индикации 2, выход второго элемента ИЛИ-И-НЕ 18 является выходом блока индикации 2.

Данная схема в значительной мере совпадает со схемой RS-триггера [3], часть элементов которой после проведения эквивалентных логических преобразований представляется в базисе ИЛИ-И-НЕ.

Схема на фиг.3 работает следующим образом. При низком уровне сигнала на входе предустановки 5 триггер воспринимает и запоминает рабочее состояние парафазного информационного входа со спейсером 3, 4 - (0,1) или (1,0), - в бистабильной ячейке первого каскада на элементах 14 и 15, а окончание запоминания нового состояния фиксируется блоком индикации на элементе 18, выход которого (и соответственно - индикаторный выход 8) переключается в логическую 1 только после окончания переключения элементов 14 и 15. При этом входы второй бистабильной ячейки на элементах 16 и 17 блокированы рабочим состоянием парафазного информационного входа со спейсером 3, 4. Переход в спейсер парафазного информационного входа 3, 4 (логическая 1 на обеих его составляющих) обеспечивает хранение информации на выходах бистабильной ячейки первого каскада и разрешает перезапись этого состояния в бистабильную ячейку второго каскада на элементах 16 и 17, выходы которых подключены к первому 6 и второму 7 информационным выходам триггера соответственно. Окончание перезаписи информации в бистабильную ячейку второго каскада разрешает переключение выхода индикаторного элемента 18 (и соответственно - индикаторного выхода 8) в низкий уровень (логический 0), индицируя тем самым завершение обновления состояния первого 6 и второго 7 информационных выходов триггера.

Предустановка осуществляется после подтверждения перезаписи информации в бистабильную ячейку второго каскада (появление низкого уровня на индикаторном выходе 8) подачей на вход предустановки 5 высокого уровня при поддержке также высокого (спейсерного) состояния и на парафазном информационном входе со спейсером 3, 4. При этом элемент 14 переключается в логический 0, заставляя элемент 15 перейти в состояние логической 1, что, в свою очередь, инициирует переключение элемента 17 в логический 0, а вслед за этим и переключение элемента 16 в логическую 1, завершая тем самым предустановку. На первом информационном выходе 6 триггера формируется высокий уровень. При этом выход индикаторного элемента 18 (и соответственно - индикаторный выход 8) не изменяется на всем протяжении установки, поскольку его группы входов блокированы высокими уровнями (спейсером) на парафазном информационном входе 3, 4 и входе предустановки 5. По окончании предустановки на вход предустановки 5 подается низкий уровень, и схема триггера готова к продолжению работы.

В схеме на фиг.3 возможны два варианта спецификации входов и выходов триггера:

1) вход предустановки является входом установки единицы, первая и вторая составляющие парафазного информационного входа со спейсером являются прямой и инверсной информационными составляющими соответственно, а первый и второй информационные выходы триггера являются прямым и инверсным информационными выходами соответственно,

2) вход предустановки является входом установки нуля, первая и вторая составляющие парафазного информационного входа со спейсером являются соответственно инверсной и прямой информационными составляющими, а первый и второй информационные выходы триггера являются инверсным и прямым информационными выходами соответственно.

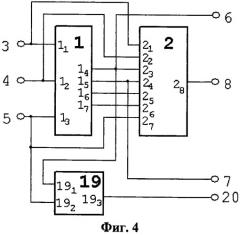

На фиг.4 представлена реализация двухтактного самосинхронного RS-триггера с парафазным информационным входом со спейсером и самосинхронной предустановкой, в которой успешное завершение предустановки фиксируется дополнительным элементом. Схема отличается от схемы на фиг.1 тем, что в нее введены элемент фиксации окончания предустановки 19, входы которого подключены к первому информационному выходу 6 триггера и входу предустановки 5 соответственно, и второй индикаторный выход 20, соединенный с выходом элемента фиксации окончания предустановки.

Схема на фиг.4 работает аналогично схеме на фиг.1. Но теперь окончание предустановки (переключение первого выхода 6 триггера в состояние, соответствующее типу предустановки) фиксируется элементом 19: после переключения первого информационного выхода 6 триггера в требуемое состояние элемент фиксации окончания предустановки 19 переключает второй индикаторный выход 20 в активное состояние, подтверждая тем самым окончание предустановки триггера.

На фиг.5 показана схема двухтактного самосинхронного RS-триггера с самосинхронной предустановкой для случая с нулевым спейсером парафазного информационного входа. Она отличается от схемы на фиг.2 тем, что в нее введены элемент фиксации окончания предустановки 19, входы которого подключены к первому информационному выходу 6 триггера и входу предустановки 5 соответственно, и второй индикаторный выход 20, соединенный с выходом элемента фиксации окончания предустановки 19, причем элемент фиксации окончания предустановки 19 реализован на втором элементе ИЛИ-НЕ 21, входы которого являются входами элемента фиксации окончания предустановки 19, а выход - выходом элемента фиксации окончания предустановки 19.

Схема на фиг.5 работает так же, как и схема на фиг.2. Но теперь переключение первого информационного выхода триггера 6 в устанавливаемое состояние индицируется элементом фиксации окончания предустановки 19. При пассивном (единичном) значении сигнала на входе предустановки 5 выход элемента фиксации окончания предустановки 19 находится в состоянии логического 0. В режиме предустановки низкий уровень на входе предустановки 5 и появляющийся в результате предустановки низкий уровень на первом информационном выходе триггера 6 заставляют элемент 21 переключиться в логическую 1. Появление высокого уровня на выходе элемента фиксации окончания предустановки 19 (и соответственно - на втором индикаторном выходе 20) свидетельствует об успешном окончании предустановки. Последующая подача пассивного (единичного) уровня на вход предустановки 5 переводит элемент фиксации окончания предустановки 19 в состояние логического 0, подтверждающее выход триггера из режима предустановки.

В схеме на фиг.5 возможны два варианта спецификации входов и выходов триггера:

1) вход предустановки является входом установки нуля, первая и вторая составляющие парафазного информационного входа со спейсером являются соответственно прямой и инверсной информационными составляющими, а первый и второй информационные выходы триггера являются прямым и инверсным информационными выходами соответственно,

2) вход предустановки является входом установки единицы, первая и вторая составляющие парафазного информационного входа со спейсером являются соответственно инверсной и прямой информационными составляющими, а первый и второй информационные выходы триггера являются инверсным и прямым информационными выходами соответственно.

На фиг.6 показана схема двухтактного самосинхронного RS-триггера с самосинхронной предустановкой для случая с единичным спейсером парафазного информационного входа. Она отличается от схемы на фиг.3 тем, что в нее введены элемент фиксации окончания предустановки 19, входы которого подключены к первому информационному выходу 6 триггера и входу предустановки 5 соответственно, и второй индикаторный выход 20, соединенный с выходом элемента фиксации окончания предустановки 19, причем элемент фиксации окончания предустановки 19 реализован на втором элементе И-НЕ 22, входы которого являются входами элемента фиксации окончания предустановки 19, а выход - выходом элемента фиксации окончания предустановки 19.

Схема на фиг.6 работает так же, как и схема на фиг.3. Но теперь переключение первого информационного выхода триггера 6 в устанавливаемое состояние индицируется элементом фиксации окончания предустановки 19. При пассивном (нулевом) значении сигнала на входе предустановки 5 выход элемента фиксации окончания предустановки 19 находится в состоянии логической 1. В режиме предустановки высокий уровень на входе предустановки 5 и появляющийся в результате предустановки высокий уровень на первом информационном выходе триггера 6 заставляют элемент 22 переключиться в логический 0. Появление низкого уровня на выходе элемента фиксации окончания предустановки 19 (и соответственно - на втором индикаторном выходе 20) свидетельствует об успешном окончании предустановки. Последующая подача пассивного (нулевого) уровня на вход предустановки 5 переводит элемент фиксации окончания предустановки 19 в состояние логической 1, подтверждающее выход триггера из режима предустановки.

В схеме на фиг.6 возможны два варианта спецификации входов и выходов триггера:

1) вход предустановки является входом установки единицы, первая и вторая составляющие парафазного информационного входа со спейсером являются прямой и инверсной информационными составляющими соответственно, а первый и второй информационные выходы триггера являются прямым и инверсным информационными выходами соответственно,

2) вход предустановки является входом установки нуля, первая и вторая составляющие парафазного информационного входа со спейсером являются соответственно инверсной и прямой информационными составляющими, а первый и второй информационные выходы триггера являются инверсным и прямым информационными выходами соответственно.

В рассмотренных реализациях двухтактного самосинхронного RS-триггера с самосинхронной предустановкой и парафазным информационным входом со спейсером успешное окончание предустановки индицируется отдельно от индикации окончания обновления состояния триггера под воздействием парафазного информационного входа, что в ряде случаев требует неоправданного усложнения схемы управления самосинхронного устройства, в составе которого используется данный триггер. Этот недостаток может быть устранен путем объединения в одном блоке индикации свойств индикации всех режимов работы триггера, как описано ниже.

На фиг.7 представлена реализация двухтактного самосинхронного RS-триггера с парафазным информационным входом со спейсером и самосинхронной предустановкой, в которой успешное завершение предустановки фиксируется на выходе блока индикации. Схема отличается от схемы на фиг.1 тем, что в нее введены элемент фиксации окончания предустановки 19, первый и второй входы которого подключены к первому информационному выходу 6 триггера и входу предустановки 5 триггера соответственно, а в блок индикации 2 введен восьмой вход, подключенный к выходу элемента фиксации окончания предустановки 19. В такой реализации блок индикации 2 обеспечивает индикацию как предустановки триггера, так и окончания перехода в фазу хранения или обновления состояния триггера.

Схема на фиг.7 работает аналогично схеме на фиг.4 с тем лишь отличием, что блок индикации фиксирует теперь окончание переключений элементов триггера во всех режимах его работы, включая и предустановку.

На фиг.8 показана схема двухтактного самосинхронного RS-триггера с самосинхронной предустановкой и объединенным индикатором для случая с нулевым спейсером парафазного информационного входа. Она отличается от схемы на фиг.2 тем, что в нее введены восьмой вход блока индикации 2 и элемент фиксации окончания предустановки 19, содержащий второй элемент ИЛИ-НЕ 21, а во второй элемент И-ИЛИ-НЕ 13 введена пятая группа входов И, вход которой подключен к восьмому входу блока индикации 2, первый вход элемента фиксации окончания предустановки 19 подключен к первому информационному выходу 6 триггера и к первому входу второго элемента ИЛИ-НЕ 21, второй вход элемента фиксации окончания предустановки 19 подключен к входу предустановки 5 триггера и ко второму входу второго элемента ИЛИ-НЕ 21, а выход элемента фиксации окончания предустановки 19 соединен с выходом второго элемента ИЛИ-НЕ 21 и с восьмым входом блока индикации 2.

Схема на фиг.8 работает так же, как и схема на фиг.5, с тем отличием, что окончание предустановки фиксируется блоком индикации 2. При пассивном (логической 1) значении сигнала на входе предустановки 5 выход элемента фиксации окончания предустановки 19 находится в состоянии логического 0 и не влияет на работу элемента И-ИЛИ-НЕ 13 в блоке индикации 2. В режиме предустановки, при спейсерном (нулевом) состоянии парафазного информационного входа 3, 4, низкий уровень на входе предустановки 5 и появляющийся в результате предустановки низкий уровень на первом информационном выходе триггера 6 заставляют элемент 21 переключиться в логическую 1, которая, в свою очередь, инициирует переключение элемента 13 (и соответственно - первый индикаторный выход 8) в логический 0, что свидетельствует об успешном окончании предустановки. Последующая подача пассивного (логической 1) уровня на вход предустановки 5 при сохранении спейсерного состояния на парафазном информационном входе 3, 4 переводит элемент фиксации окончания предустановки 19 в состояние логического 0, а элемент 13 - в состояние логической 1, подтверждающее выход триггера из режима предустановки.

В схеме на фиг.8 также возможны два варианта спецификации входов и выходов триггера:

1) вход предустановки является входом установки нуля, первая и вторая составляющие парафазного информационного входа со спейсером являются соответственно прямой и инверсной информационными составляющими, а первый и второй информационные выходы триггера являются прямым и инверсным информационными выходами соответственно,

2) вход предустановки является входом установки единицы, первая и вторая составляющие парафазного информационного входа со спейсером являются соответственно инверсной и прямой информационными составляющими, а первый и второй информационные выходы триггера являются инверсным и прямым информационными выходами соответственно.

На фиг.9 показана схема двухтактного самосинхронного RS-триггера с самосинхронной предустановкой и объединенным индикатором для случая с единичным спейсером парафазного информационного входа. Она отличается от схемы на фиг.3 тем, что в нее введены восьмой вход блока индикации 2 и элемент фиксации окончания предустановки 19, содержащий второй элемент И-НЕ 22, а во второй элемент ИЛИ-И-НЕ 18 введена пятая группа входов ИЛИ, вход которой подключен к восьмому входу блока индикации 2, первый вход элемента фиксации окончания предустановки 19 подключен к первому информационному выходу 6 триггера и к первому входу второго элемента И-НЕ 22, второй вход элемента фиксации окончания предустановки 19 подключен к входу предустановки 5 триггера и ко второму входу второго элемента И-НЕ 22, а выход элемента фиксации окончания предустановки 19 соединен с выходом второго элемента И-НЕ 22 и с восьмым входом блока индикации 2.

Схема на фиг.9 работает так же, как и схема на фиг.6, с тем отличием, что окончание предустановки фиксируется блоком индикации 2. При пассивном (нулевом) значении сигнала на входе предустановки 5 выход элемента фиксации окончания предустановки 19 находится в состоянии логической 1 и не влияет на работу элемента ИЛИ-И-НЕ 18 в блоке индикации 2. В режиме предустановки, при спейсерном (логической 1) состоянии парафазного информационного входа 3, 4, высокий уровень на входе предустановки 5 и появляющийся в результате предустановки высокий уровень на первом информационном выходе триггера 6 заставляют элемент И-НЕ 22 переключиться в логический 0, который, в свою очередь, инициирует переключение элемента 18 в логическую 1, что свидетельствует об успешном окончании предустановки. Последующая подача пассивного (нулевого) уровня на вход предустановки 5 при сохранении спейсерного состояния на парафазном информационном входе 3, 4 переводит элемент фиксации окончания предустановки 19 в состояние логической 1, а элемент 18 - в состояние логического 0, подтверждающее выход триггера из режима предустановки.

В схеме на фиг.9 возможны два варианта спецификации входов и выходов триггера:

1) вход предустановки является входом установки единицы, первая и вторая составляющие парафазного информационного входа со спейсером являются прямой и инверсной информационными составляющими соответственно, а первый и второй информационные выходы триггера являются прямым и инверсным информационными выходами соответственно,

2) вход предустановки является входом установки нуля, первая и вторая составляющие парафазного информационного входа со спейсером являются соответственно инверсной и прямой информационными составляющими, а первый и второй информационные выходы триггера являются инверсным и прямым информационными выходами соответственно.

На фиг.10 представлена реализация однотактного самосинхронного RS-триггера с парафазным информационным входом со спейсером и самосинхронной предустановкой, объединенным индикатором и вторым индикаторным выходом. Схема отличается от схемы на фиг.7 тем, что в нее введен второй индикаторный выход 20, подключенный к выходу элемента фиксации окончания предустановки 19.

Второй индикаторный выход 20 может использоваться в ряде практических применений для ускорения взаимодействия между составными частями самосинхронного устройства.

На фиг.11 представлена реализация двухтактного самосинхронного RS-триггера с самосинхронной предустановкой, объединенным индикатором, парафазным информационным входом с нулевым спейсером и вторым индикаторным выходом. Схема отличается от схемы на фиг.8 тем, что в нее введен второй индикаторный выход 20, подключенный к выходу элемента фиксации окончания предустановки 19.

Схема на фиг.11 работает так же, как и схема на фиг.8. Но теперь выход элемента фиксации окончания предустановки 19 может использоваться для ускорения запрос-ответных взаимодействий между устройствами в общей самосинхронной схеме в режиме предустановки.

На фиг.12 представлена реализация двухтактного самосинхронного RS-триггера с самосинхронной предустановкой, объединенным индикатором, парафазным информационным входом с единичным спейсером и вторым индикаторным выходом. Схема отличается от схемы на фиг.9 тем, что в нее введен второй индикаторный выход 20, подключенный к выходу элемента фиксации окончания предустановки 19.

Схема на фиг.12 работает так же, как и схема на фиг.9. Но теперь выход элемента фиксации окончания предустановки 19 может использоваться для ускорения запрос-ответных взаимодействий между устройствами в общей самосинхронной схеме в режиме предустановки.

Таким образом, представленные варианты двухтактного самосинхронного RS-триггера с самосинхронной предустановкой и парафазным информационным входом со спейсером позволяют получить следующие реализации (при соответствующей спецификации входов и выходов триггера):

1) двухтактный самосинхронный RS-триггер с нулевым спейсерным состоянием парафазного информационного входа и синхронным начальным сбросом - предустановкой низкого уровня на прямом информационном выходе триггера (фиг.2),

2) двухтактный самосинхронный RS-триггер с единичным спейсерным состоянием парафазного информационного входа и синхронной установкой единицы - предустановкой высокого уровня на прямом информационном выходе триггера (фиг.3),

3) двухтактный самосинхронный RS-триггер с нулевым спейсерным состоянием парафазного информационного входа и синхронной установкой единицы - предустановкой высокого уровня на прямом информационном выходе триггера (фиг.2),

4) двухтактный самосинхронный RS-триггер с единичным спейсерным состоянием парафазного информационного входа и синхронным начальным сбросом - предустановкой низкого уровня на прямом информационном выходе триггера (фиг.3),

5) двухтактный самосинхронный RS-триггер с нулевьм спейсерным состоянием парафазного информационного входа и самосинхронным начальным сбросом - предустановкой низкого уровня на прямом информационном выходе триггера (фиг.5, 8 и 11),

6) двухтактный самосинхронный RS-триггер с единичным спейсерным состоянием парафазного информационного входа и самосинхронной установкой единицы - предустановкой высокого уровня на прямом информационном выходе триггера (фиг.6, 9 и 12),

7) двухтактный самосинхронный RS-триггер с нулевым спейсерным состоянием парафазного информационного входа и самосинхронной установкой единицы - предустановкой высокого уровня на прямом информационном выходе триггера (фиг.5, 8 и 11),

8) двухтактный самосинхронный RS-тригтер с единичным спейсерным состоянием парафазного информационного входа и самосинхронным начальным сбросом - предустановкой низкого уровня на прямом информационном выходе триггера (фиг.6, 9 и 12).

Источники информации

1. Шило В.Л. Популярные цифровые микросхемы: Справочник. 2-е изд., испр. - Челябинск: Металлургия, Челябинское отд., 1989. - рис.1.54а.

2. Астахановский А.Г., Варшавский В.И., Мараховский В.Б. и др. Апериодические автоматы // Под ред. В.И.Варшавского. - М.: Наука, 1976, рис.рис.2.16(а).

3. Астахановский А.Г., Варшавский В.И., Мараховский В.Б. и др. Апериодические автоматы // Под ред. В.И.Варшавского. - М.: Наука, 1976, рис. рис.2.16(б).

1. Двухтактный самосинхронный RS-триггер с парафазным информационным входом, содержащий блок памяти, блок индикации, первую и вторую составляющие парафазного информационного входа, первый и второй информационные выходы и индикаторный выход, причем первая составляющая парафазного информационного входа соединена с первыми входами блоков памяти и индикации, вторая составляющая парафазного информационного входа соединена со вторыми входами блоков памяти и индикации, первый информационный выход п