Устройство декодирования ртсм

Иллюстрации

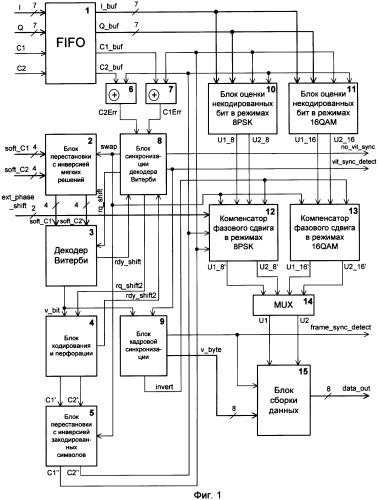

Показать всеИзобретение относится к системам телекоммуникаций и может найти применение в приемниках цифровой информации для исправления ошибок, возникающих в спутниковых каналах передачи информации, например, в системе DVB-DSNG или системе DVB-S. Техническим результатом является уменьшение аппаратной сложности устройства и вносимой им временной задержки в условиях возможной фазовой неопределенности I,Q-сигнала на выходе демодулятора. Указанный технический результат достигается тем, что разрешение фазовой неоднозначности I,Q-сигнала на выходе I,Q-демодулятора приемника осуществляется в устройстве в процессе его синхронизации с использованием свойств сверточного кода, последовательности синхробайт и свойств блочного кода Рида-Соломона. Компенсация возможного фазового сдвига I,Q-сигнала осуществляется распределенно различными блоками устройства. Фазовый сдвиг для бит данных, закодированных сверточным кодом, компенсируется в блоке перестановки с инверсией мягких решений и блоке кадровой синхронизации. Компенсация фазового сдвига для бит данных, не кодированных сверточным кодом, осуществляется компенсатором фазового сдвига в режимах 8PSK или компенсатором фазового сдвига в режимах 16QAM с использованием результатов работы декодера Витерби, блока синхронизации декодера Витерби и блока кадровой синхронизации. Устройство содержит буфер I,Q-компонент сигнала 1, блок перестановки с инверсией мягких решений 2, декодер Витерби 3, блок кодирования и перфорации 4, блок перестановки с инверсией закодированных символов 5, первый 6 и второй 7 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, блок синхронизации декодера Витерби 8, блок кадровой синхронизации 9, блоки оценки некодированных бит в режимах 8PSK 10 и в режимах 16QAM 11, компенсаторы фазового сдвига в режимах 8PSK 12 и в режимах 16QAM 13, мультиплексор некодированных данных 14 и блок сборки данных 15. 9 з.п. ф-лы, 27 ил., 1 табл.

Реферат

Изобретение относится к системам телекоммуникаций и может найти применение в приемниках цифровой информации для исправления ошибок, возникающих в спутниковых каналах передачи информации, например, в системе DVB-DSNG (Digital Video Broadcasting - Digital Satellite News Gathering) [1] или системе DVB-S (Digital Video Broadcasting - Satellite) [2].

Известно устройство декодирования РТСМ (Pragmatic Trellis Coded Modulation), предназначенное для работы в составе приемника цифровой информации, использующего сигнальные созвездия M-PSK [3]. Устройство содержит табличный преобразователь значений синфазной и квадратурной компонент сигнала в полярную систему координат, табличный вычислитель значений метрик ветвей для декодера Витерби, декодер Витерби, детектор интенсивности нормализации декодера Витерби, кодер сверточного кода, табличный формирователь значений секторов, буфер задержки, логику поворота секторов, блок оценки значений некодируемых бит, декодер разрешения фазовой неопределенности, дифференциальный декодер.

Фазовая неоднозначность I,Q-сигнала устраняется в устройстве [3] путем вращения значений секторов в случае обнаружения высокой интенсивности нормализации декодера Витерби и использования декодера разрешения фазовой неопределенности вместе с дифференциальным декодером. Наличие этих декодеров в устройстве обусловлено применяемым дифференциальным кодированием бит данных.

Недостатками устройства [3] являются:

- ограниченная область его применения. Устройство [3] предназначено для сигнальных созвездий M-PSK, но не поддерживает QAM (16QAM используется в системе DVB-DSNG);

- применение дифференциального кодирования приводит к размножению ошибок, что снижает помехоустойчивость приема информации из канала.

Известно устройство декодирования РТСМ, предназначенное для работы в составе приемника цифровой информации, использующего сигнальные созвездия M-PSK [4]. Устройство содержит блок оценки фазы I,Q-сигнала, два фазовращателя, блок задержки оценки фазы сигнала, выделитель группы символов сверточного кода, декодер сверточного кода, кодер сверточного кода, детектор секторов сигнального созвездия, контроллер кадровой синхронизации и три мультиплексора.

Контроллер кадровой синхронизации в известном устройстве разрешает фазовую неоднозначность I,Q-сигнала, анализируя кадровые синхронизирующие слова и поворачивая фазу в двух фазовращателях. Кадровые синхронизирующие слова должны при этом представляться как битами, закодированными сверточным кодом, так и некодируемыми битами.

Недостатком устройства является ограниченная область его применения. РТСМ-декодер [4] предназначен для сигнальных созвездий M-PSK, но так же, как и устройство [3], не поддерживает QAM. Кроме того, введенные для компенсации сдвига фазы I,Q-сигнала, блок оценки фазы I,Q-сигнала и фазовращатели манипулируют многоразрядными двоичными числами, что определяет относительную затратность аппаратных решений.

Наиболее близким по технической сущности к заявляемому изобретению является выбранное в качестве прототипа устройство, предназначенное для приема цифровой информации из спутникового канала системы DVB-DSNG [5]. Устройство содержит I,Q-демодулятор, перестраиваемый преобразователь фазы I,Q-сигнала, декодер внутреннего кода, использующий алгоритм Витерби, детектор заголовка транспортного потока, детектор поворота фазы, буфер задержки, декодер внешнего кода (кода Рида-Соломона).

Устройство-прототип разрешает фазовую неоднозначность сигнала на выходе I,Q-демодулятора путем вращения фазы сигнала на входе декодера внутреннего кода. Для определения необходимого угла поворота фазы анализируются заголовки пакетов транспортного потока (синхробайты) и сигнал отказа от декодирования декодера внешнего кода.

Недостатком прототипа является относительно высокая сложность реализации перестраиваемого преобразователя фазы, обусловленная необходимостью выполнения вычислений над многоразрядными двоичными числами, представляющими I и Q компоненты сигнала. Кроме того, включение преобразователя фазы перед декодером внутреннего кода приводит к увеличению временной задержки поступления данных в декодер внешнего кода при осуществлении поворота фазы.

Технической задачей изобретения является уменьшение аппаратной сложности устройства декодирования РТСМ (РТСМ-декодера) и вносимой им временной задержки в условиях возможной фазовой неопределенности I,Q-сигнала на выходе демодулятора.

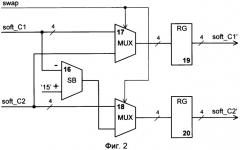

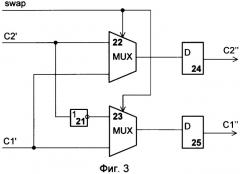

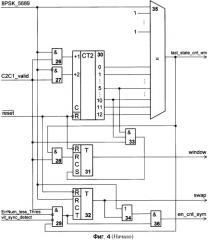

Поставленная техническая задача решается тем, что в известное устройство, содержащее буфер I,Q-компонент сигнала, декодер Витерби, блок кадровой синхронизации, причем первые входы, вторые входы, третий вход и четвертый вход буфера I,Q-компонент сигнала являются соответственно входами I, Q, С1 и С2 устройства декодирования РТСМ, согласно изобретению введены блок перестановки с инверсией мягких решений, блок кодирования и перфорации, блок перестановки с инверсией закодированных символов, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, блок синхронизации декодера Витерби, блок оценки некодированных бит в режимах 8PSK, блок оценки некодированных бит в режимах 16QAM, компенсатор фазового сдвига в режимах 8PSK, компенсатор фазового сдвига в режимах 16QAM, мультиплексор некодированных данных, блок сборки данных, причем первые и вторые входы блока перестановки с инверсией мягких решений являются соответственно входами soft_C1 и soft_C2 устройства декодирования РТСМ, первые и вторые выходы блока перестановки с инверсией мягких решений соединены соответственно с первыми и вторыми входами декодера Витерби, первый выход декодера Витерби соединен с первым входом блока кодирования и перфорации и с первым входом блока кадровой синхронизации, первый и второй выходы блока кодирования и перфорации соединены соответственно с первым и вторым входами блока перестановки с инверсией закодированных символов, первый выход блока перестановки с инверсией закодированных символов соединен со вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с третьим входом блока оценки некодированных бит в режимах 8PSK, с третьим входом блока оценки некодированных бит в режимах 16QAM и с седьмым входом компенсатора фазового сдвига в режимах 8PSK, второй выход блока перестановки с инверсией закодированных символов соединен со вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с четвертым входом блока оценки некодированных бит в режимах 8PSK, с четвертым входом блока оценки некодированных бит в режимах 16QAM и с шестым входом компенсатора фазового сдвига в режимах 8PSK, первые выходы буфера I,Q-компонент сигнала соединены с первыми входами блока оценки некодированных бит в режимах 8PSK и с первыми входами блока оценки некодированных бит в режимах 16QAM, вторые выходы буфера I,Q-компонент сигнала соединены со вторыми входами блока оценки некодированных бит в режимах 8PSK и со вторыми входами блока оценки некодированных бит в режимах 16QAM, третий выход буфера I,Q-компонент сигнала соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четвертый выход буфера I,Q-компонент сигнала соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом блока синхронизации декодера Витерби, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен со вторым входом блока синхронизации декодера Витерби, первый выход блока синхронизации декодера Витерби соединен с третьим входом блока перестановки с инверсией мягких решений, с третьим входом блока перестановки с инверсией закодированных символов, с первым входом компенсатора фазового сдвига в режимах 8PSK и с первым входом компенсатора фазового сдвига в режимах 16QAM, второй выход блока синхронизации декодера Витерби соединен с третьим входом декодера Витерби, второй выход декодера Витерби соединен с третьим входом блока синхронизации декодера Витерби, третий выход блока синхронизации декодера Витерби является выходом no_vit_sync устройства декодирования РТСМ, четвертый выход блока синхронизации декодера Витерби соединен со вторым входом блока кадровой синхронизации и является выходом vit_sync_detect устройства декодирования РТСМ, пятый выход блока синхронизации декодера Витерби соединен со вторым входом блока кодирования и перфорации, третий выход блока кодирования и перфорации соединен с четвертым входом блока синхронизации декодера Витерби, первый выход блока кадровой синхронизации соединен с четвертым входом компенсатора фазового сдвига в режимах 8PSK и с четвертым входом компенсатора фазового сдвига в режимах 16QAM, второй выход блока кадровой синхронизации соединен с третьим входом блока сборки данных и является выходом frame_sync_detect устройства декодирования РТСМ, третьи выходы блока кадровой синхронизации соединены с четвертыми входами блока сборки данных, первый выход блока оценки некодированных бит в режимах 8PSK соединен со вторым входом компенсатора фазового сдвига в режимах 8PSK, второй выход блока оценки некодированных бит в режимах 8PSK соединен с третьим входом компенсатора фазового сдвига в режимах 8PSK, первый выход блока оценки некодированных бит в режимах 16QAM соединен со вторым входом компенсатора фазового сдвига в режимах 16QAM, второй выход блока оценки некодированных бит в режимах 16QAM соединен с третьим входом компенсатора фазового сдвига в режимах 16QAM, пятый вход компенсатора фазового сдвига в режимах 8PSK является входом ext_phase_shift устройства декодирования РТСМ, первый выход компенсатора фазового сдвига в режимах 8PSK соединен с первым входом мультиплексора некодированных данных, второй выход компенсатора фазового сдвига в режимах 8PSK соединен со вторым входом мультиплексора некодированных данных, первый выход компенсатора фазового сдвига в режимах 16QAM соединен с третьим входом мультиплексора некодированных данных, второй выход компенсатора фазового сдвига в режимах 16QAM соединен с четвертым входом мультиплексора некодированных данных, первый выход мультиплексора некодированных данных соединен с первым входом блока сборки данных, второй выход мультиплексора некодированных данных соединен со вторым входом блока сборки данных, первые выходы блока сборки данных являются выходами data_out устройства декодирования РТСМ, причем блок перестановки с инверсией мягких решений содержит первый вычитатель, первый мультиплексор, второй мультиплексор, первый буферный регистр, второй буферный регистр, причем управляющий вход первого мультиплексора соединен с управляющим входом второго мультиплексора и является третьим входом блока перестановки с инверсией мягких решений, первые входы данных первого мультиплексора соединены со входами вычитаемого первого вычитателя и являются первыми входами блока перестановки с инверсией мягких решений, вторые входы данных первого мультиплексора соединены с первыми входами данных второго мультиплексора и являются вторыми входами блока перестановки с инверсией мягких решений, входы уменьшаемого первого вычитателя соединены с шиной константы '15', выходы первого вычитателя соединены со вторыми входами данных второго мультиплексора, выходы первого мультиплексора соединены со входами данных первого буферного регистра, выходы второго мультиплексора соединены со входами данных второго буферного регистра, выходы первого буферного регистра являются первыми выходами блока перестановки с инверсией мягких решений, выходы второго буферного регистра являются вторыми выходами блока перестановки с инверсией мягких решений, причем блок перестановки с инверсией закодированных символов содержит первый инвертор, третий мультиплексор, четвертый мультиплексор, первый D-триггер, второй D-триггер, причем управляющий вход третьего мультиплексора соединен с управляющим входом четвертого мультиплексора и является третьим входом блока перестановки с инверсией закодированных символов, первый вход данных третьего мультиплексора соединен со входом первого инвертора и является вторым входом блока перестановки с инверсией закодированных символов, второй вход данных третьего мультиплексора соединен со вторым входом данных четвертого мультиплексора и является первым входом блока перестановки с инверсией закодированных символов, выход первого инвертора соединен с первым входом данных четвертого мультиплексора, выход третьего мультиплексора соединен с D-входом первого D-триггера, выход четвертого мультиплексора соединен с D-входом второго D-триггера, выход первого D-триггера является вторым выходом блока перестановки с инверсией закодированных символов, выход второго D-триггера является первым выходом блока перестановки с инверсией закодированных символов, причем блок синхронизации декодера Витерби содержит первый элемент И, второй элемент И, третий элемент И, четвертый элемент И, первый счетчик, первый RS-триггер, Т-триггер, пятый элемент И, первый элемент ИЛИ, первый компаратор, шестой элемент И, седьмой элемент И, третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, восьмой элемент И, девятый элемент И, десятый элемент И, одиннадцатый элемент И, второй счетчик, пятый мультиплексор, второй RS-триггер, второй компаратор, двенадцатый элемент И, третий счетчик, третий RS-триггер, четвертый RS-триггер, четвертый счетчик, тринадцатый элемент И, третий компаратор, пятый RS-триггер, причем нулевой разряд первых входов первого компаратора соединен с первым входом первого элемента И, первым, инверсным входом второго элемента И, первым входом первого элемента ИЛИ, с R-входом синхронного сброса Т-триггера, со вторым, инверсным входом седьмого элемента И и соединен с шиной 8PSK_5689 устройства декодирования РТСМ, разряды с первого по двенадцатый первых входов первого компаратора соединены с шиной константы единицы, второй вход первого элемента И соединен со вторым входом второго элемента И, с третьим входом пятого элемента И, со вторым входом третьего элемента И, с первым входом четвертого элемента И, со вторым входом девятого элемента И, со вторым входом десятого элемента И, со вторым входом одиннадцатого элемента И и соединен с шиной C2C1_valid устройства декодирования РТСМ, выход первого элемента И соединен со входом инкремента на единицу первого счетчика, выход второго элемента И соединен со входом инкремента на два первого счетчика, инверсный R-вход асинхронного сброса первого счетчика соединен с инверсным R-входом асинхронного сброса первого RS-триггера, с инверсным R-входом асинхронного сброса Т-триггера, с инверсным R-входом асинхронного сброса второго счетчика, с инверсным R-входом асинхронного сброса второго RS-триггера, с инверсным R-входом асинхронного сброса третьего счетчика, с инверсным R-входом асинхронного сброса третьего RS-триггера, с инверсным R-входом асинхронного сброса четвертого RS-триггера, с инверсным R-входом асинхронного сброса пятого RS-триггера, с инверсным R-входом асинхронного сброса четвертого счетчика и соединен с шиной сброса reset устройства декодирования РТСМ, выходы первого счетчика соединены со вторыми входами первого компаратора, пятый разряд выходов первого счетчика соединен с первым входом пятого элемента И, десятый разряд выходов первого счетчика соединен со вторым входом пятого элемента И, выход первого компаратора соединен с первым входом третьего элемента И, с четвертым входом четвертого элемента И, с третьим входом одиннадцатого элемента И, выход третьего элемента И соединен с R-входом синхронного сброса первого RS-триггера, выход пятого элемента И соединен с S-входом первого RS-триггера, выход четвертого элемента И соединен с Т-входом Т-триггера и со вторым входом шестого элемента И, выход Т-триггера соединен со вторым входом первого элемента ИЛИ и является первым выходом блока синхронизации декодера Витерби, выход первого элемента ИЛИ соединен с первым входом шестого элемента И, выход первого RS-триггера соединен с инверсным R-входом синхронного сброса второго счетчика, выход шестого элемента И соединен со входом инкремента на единицу третьего счетчика, со вторым входом двенадцатого элемента И, с S-входом третьего RS-триггера, с S-входом четвертого RS-триггера, первый вход седьмого элемента И является первым входом блока синхронизации декодера Витерби, выход седьмого элемента И соединен с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с первым входом восьмого элемента И, второй вход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен со вторым входом восьмого элемента И и является вторым входом блока синхронизации декодера Витерби, выход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом девятого элемента И, выход восьмого элемента И соединен с первым входом десятого элемента И, выход девятого элемента И соединен со входом инкремента на единицу второго счетчика, выход десятого элемента И соединен со входом инкремента на два второго счетчика, выходы второго счетчика соединены с первыми входами второго компаратора, первые входы, вторые входы, третьи входы, четвертые входы, пятые входы, шестые входы, седьмые входы, восьмые входы, девятые входы и десятые входы данных пятого мультиплексора соединены соответственно с шинами thres_QPSK12, thres_QPSK23, thres_QPSK34, thres_QPSK56, thres_QPSK78, thres_8PSK23, thres_8PSK56, thres_8PSK89, thres_16QAM34, thres_16QAM78 устройства декодирования РТСМ, управляющие входы пятого мультиплексора соединены с шиной выбора режима кодирования и модуляции mode устройства декодирования РТСМ, выходы пятого мультиплексора соединены со вторыми входами второго компаратора, выход второго компаратора соединен с первым входом одиннадцатого элемента И и со вторым, инверсным входом четвертого элемента И, выход одиннадцатого элемента И соединен с S-входом второго RS-триггера, выход второго RS-триггера соединен с третьим, инверсным входом четвертого элемента И и является четвертым выходом блока синхронизации декодера Витерби, первые входы третьего компаратора соединены с шиной n_last_state_cnt_sym устройства декодирования РТСМ, выходы третьего счетчика соединены со вторыми входами третьего компаратора, выход третьего компаратора соединен с R-входом синхронного сброса третьего счетчика и с первым входом двенадцатого элемента И, выход двенадцатого элемента И соединен с первым входом тринадцатого элемента И и со входом инкремента на единицу четвертого счетчика, R-вход третьего RS-триггера является третьим входом блока синхронизации декодера Витерби, выход третьего RS-триггера является вторым выходом блока синхронизации декодера Витерби, R-вход четвертого RS-триггера является четвертым входом блока синхронизации декодера Витерби, выход четвертого RS-триггера является пятым выходом блока синхронизации декодера Витерби, нулевой разряд выходов четвертого счетчика соединен со вторым входом тринадцатого элемента И, первый разряд выходов четвертого счетчика соединен с третьим входом тринадцатого элемента И, выход тринадцатого элемента И соединен с S-входом пятого RS-триггера, выход пятого RS-триггера является третьим выходом блока синхронизации декодера Витерби, причем блок кадровой синхронизации содержит первый регистр сдвига, селектор кода '47h', селектор кода 'B8h', второй элемент ИЛИ, четырнадцатый элемент И, пятнадцатый элемент И, шестнадцатый элемент И, семнадцатый элемент И, третий элемент ИЛИ, восемнадцатый элемент И, четвертый элемент ИЛИ, девятнадцатый элемент И, пятый элемент ИЛИ, двадцатый элемент И, шестой элемент ИЛИ, пятый счетчик, шестой счетчик, седьмой счетчик, восьмой счетчик, четвертый компаратор, первый дешифратор, селектор кода '7h', двадцать первый элемент И, блок инверторов, шестой RS-триггер, седьмой элемент ИЛИ, двадцать второй элемент И, двадцать третий элемент И, двадцать четвертый элемент И, двадцать пятый элемент И, восьмой элемент ИЛИ, первый шинный формирователь, второй шинный формирователь, третий шинный формирователь, четвертый шинный формирователь, пятый шинный формирователь, шестой шинный формирователь, седьмой шинный формирователь, шестой мультиплексор, девятый счетчик, сумматор, седьмой мультиплексор, девятый элемент ИЛИ, пятый компаратор, второй вычитатель, третий буферный регистр, восьмой мультиплексор, селектор нулевого кода, причем вход первого регистра сдвига является первым входом блока кадровой синхронизации, выходы первого регистра сдвига соединены со входами данных блока инверторов, со входами селектора кода '47h' и со входами селектора кода 'B8h', выход селектора кода '47h' соединен со вторым входом четырнадцатого элемента И и с первым, инверсным входом пятнадцатого элемента И, выход селектора кода 'B8h' соединен со вторым входом шестнадцатого элемента И и с первым, инверсным входом семнадцатого элемента И, первый вход четырнадцатого элемента И соединен с первым входом шестнадцатого элемента И, с инверсным R-входом синхронного сброса шестого RS-триггера, с инверсным R-входом синхронного сброса седьмого счетчика и является вторым входом блока кадровой синхронизации, выход четырнадцатого элемента И соединен со входом инкремента на единицу пятого счетчика, со вторым входом пятого элемента ИЛИ, с первым входом двадцатого элемента И и с первым входом шестого элемента ИЛИ, выход пятнадцатого элемента И соединен с первым входом третьего элемента ИЛИ, выход шестнадцатого элемента И соединен со вторым входом четвертого элемента ИЛИ, с первым входом девятнадцатого элемента И, со входом инкремента на единицу шестого счетчика и со вторым входом шестого элемента ИЛИ, выход семнадцатого элемента И соединен со вторым входом третьего элемента ИЛИ, выход третьего элемента ИЛИ соединен с первым входом четвертого элемента ИЛИ, с первым входом пятого элемента ИЛИ и со входом декремента на единицу седьмого счетчика, выход четвертого элемента ИЛИ соединен со входом декремента на единицу пятого счетчика, выход девятнадцатого элемента И соединен с R-входом синхронного сброса пятого счетчика, выход пятого элемента ИЛИ соединен со входом декремента на единицу шестого счетчика, выход двадцатого элемента И соединен с R-входом синхронного сброса шестого счетчика, выходы пятого счетчика соединены с первыми входами четвертого компаратора, выходы шестого счетчика соединены со вторыми входами четвертого компаратора, выход четвертого компаратора соединен с управляющим входом блока инверторов и является первым выходом блока кадровой синхронизации, выходы блока инверторов являются третьими выходами блока кадровой синхронизации, выход шестого элемента ИЛИ соединен со входом инкремента на единицу седьмого счетчика и с первым входом двадцать первого элемента И, выходы седьмого счетчика соединены со входами первого дешифратора, пятнадцатый разряд выходов первого дешифратора соединен со вторым входом двадцать первого элемента И, нулевой разряд выходов первого дешифратора соединен с третьим, инверсным входом пятнадцатого элемента И, с третьим, инверсным входом семнадцатого элемента И, с первым входом второго элемента ИЛИ, со вторым входом девятнадцатого элемента И, со вторым входом двадцатого элемента И, с инверсным входом инкремента на единицу восьмого счетчика, с R-входом синхронного сброса восьмого счетчика, с первым, инверсным входом двадцать пятого элемента И, с первым входом восьмого элемента ИЛИ, со вторым входом седьмого элемента ИЛИ, с управляющим входом седьмого мультиплексора и с первым входом девятого элемента ИЛИ, выход второго элемента ИЛИ соединен с третьим входом четырнадцатого элемента И и с третьим входом шестнадцатого элемента И, выход восемнадцатого элемента И соединен со вторым входом пятнадцатого элемента И, со вторым входом семнадцатого элемента И, со вторым входом второго элемента ИЛИ и с третьим входом двадцать первого элемента И, выход двадцать первого элемента И соединен с S-входом шестого RS-триггера и с шиной SB_pos_out устройства декодирования РТСМ, выход шестого RS-триггера соединен со вторым, инверсным входом восемнадцатого элемента И и является вторым выходом блока кадровой синхронизации, выходы восьмого счетчика соединены со входами селектора кода '7h', выход селектора кода '7h' соединен со вторым входом двадцать пятого элемента И, с первым входом двадцать второго элемента И и со вторым входом девятого элемента ИЛИ, управляющий вход шестого мультиплексора соединен с первым входом двадцать третьего элемента И, со вторым входом двадцать четвертого элемента И и с шиной 16QAM78 устройства декодирования РТСМ, первые входы данных шестого мультиплексора соединены с шиной константы '0', вторые входы данных шестого мультиплексора соединены с шиной константы '2', выходы шестого мультиплексора соединены с первыми входами пятого компаратора, выход двадцать пятого элемента И соединен со входом инкремента на единицу девятого счетчика, выход двадцать второго элемента И соединен со вторым входом восьмого элемента ИЛИ, выход восьмого элемента ИЛИ соединен с R-входом синхронного сброса девятого счетчика, выходы девятого счетчика соединены со вторыми входами пятого компаратора, выход пятого компаратора соединен с четвертым входом двадцать первого элемента И, со вторым входом двадцать второго элемента И и с первым входом седьмого элемента ИЛИ, выход седьмого элемента ИЛИ соединен со вторым, инверсным входом двадцать третьего элемента И и с первым входом двадцать четвертого элемента И, входы данных первого шинного формирователя соединены с шиной константы '2', управляющий вход первого шинного формирователя соединен с шиной 8PSK23 устройства декодирования РТСМ, входы данных второго шинного формирователя соединены с шиной константы '5', управляющий вход второго шинного формирователя соединен с шиной 8PSK56 устройства декодирования РТСМ, входы данных третьего шинного формирователя соединены с шиной константы '4', управляющий вход третьего шинного формирователя соединен с шиной 8PSK89 устройства декодирования РТСМ, входы данных четвертого шинного формирователя соединены с шиной константы '2', выход двадцать третьего элемента И соединен с управляющим входом четвертого шинного формирователя, входы данных пятого шинного формирователя соединены с шиной константы '3', выход двадцать четвертого элемента И соединен с управляющим входом пятого шинного формирователя, входы данных шестого шинного формирователя соединены с шиной константы '1', управляющий вход шестого шинного формирователя соединен с шиной QPSK устройства декодирования РТСМ, входы данных седьмого шинного формирователя соединены с шиной константы '3', управляющий вход седьмого шинного формирователя соединен с шиной 16QAM34 устройства декодирования РТСМ, выходы первого шинного формирователя соединены с выходами второго шинного формирователя, с выходами третьего шинного формирователя, с выходами четвертого шинного формирователя, с выходами пятого шинного формирователя, с выходами шестого шинного формирователя, с выходами седьмого шинного формирователя, с тремя младшими разрядами первых входов сумматора и с тремя младшими разрядами вторых входов данных седьмого мультиплексора, пять старших разрядов первых входов сумматора и пять старших разрядов вторых входов данных седьмого мультиплексора соединены с шиной константы '0', выходы сумматора соединены с восемью младшими разрядами входов уменьшаемого второго вычитателя и со вторыми входами данных восьмого мультиплексора, старший разряд входов уменьшаемого второго вычитателя соединен с шиной константы '0', входы вычитаемого второго вычитателя соединены с шиной константы '204', младшие разряды выходов второго вычитателя соединены с первыми входами данных восьмого мультиплексора, старший, знаковый разряд выходов второго вычитателя соединен с управляющим входом восьмого мультиплексора, выходы восьмого мультиплексора соединены с первыми входами данных седьмого мультиплексора, выходы седьмого мультиплексора соединены со входами данных третьего буферного регистра, выходы третьего буферного регистра соединены со вторыми входами сумматора и со входами селектора нулевого кода, выход девятого элемента ИЛИ соединен с управляющим входом третьего буферного регистра, выход селектора нулевого кода соединен с первым входом восемнадцатого элемента И, причем блок оценки некодированных бит в режимах 8PSK содержит второй инвертор, девятый мультиплексор, десятый мультиплексор, одиннадцатый мультиплексор, первый умножитель, второй умножитель, шестой компаратор, седьмой компаратор, двадцать шестой элемент И, двадцать седьмой элемент И, десятый элемент ИЛИ, двадцать восьмой элемент И, четвертый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, третий D-триггер, четвертый D-триггер, причем управляющий вход девятого мультиплексора соединен с первым, инверсным входом двадцать восьмого элемента И и с шиной 8PSK23 устройства декодирования РТСМ, первый вход двадцать шестого элемента И соединен с первым, инверсным входом двадцать седьмого элемента И, со входом второго инвертора, с нулевым разрядом вторых входов данных девятого мультиплексора, с управляющим входом одиннадцатого мультиплексора и является третьим входом блока оценки некодированных бит в режимах 8PSK, первый разряд вторых входов данных девятого мультиплексора является четвертым входом данных блока оценки некодированных бит в режимах 8PSK, нулевой разряд первых входов данных девятого мультиплексора соединен с шиной константы '0', выход второго инвертора соединен с первым разрядом первых входов данных девятого мультиплексора, выходы девятого мультиплексора соединены с управляющими входами десятого мультиплексора, первые входы данных десятого мультиплексора соединены с шиной константы K00 устройства декодирования РТСМ, вторые входы данных десятого мультиплексора соединены с первыми входами данных одиннадцатого мультиплексора и с шиной константы K01 устройства декодирования РТСМ, третьи входы данных десятого мультиплексора соединены с шиной константы K10 устройства декодирования РТСМ, четвертые входы данных десятого мультиплексора соединены со вторыми входами данных одиннадцатого мультиплексора и с шиной константы K11 устройства декодирования РТСМ, выходы десятого мультиплексора соединены с первыми входами первого умножителя, выходы одиннадцатого мультиплексора соединены со вторыми входами второго умножителя, вторые входы первого умножителя соединены с первыми входами второго умножителя и являются первыми входами блока оценки некодированных бит в режимах 8PSK, выходы первого умножителя соединены с первыми входами шестого компаратора, выходы второго умножителя соединены со вторыми входами седьмого компаратора, вторые входы шестого компаратора соединены с первыми входами седьмого компаратора и являются вторыми входами блока оценки некодированных бит в режимах 8PSK, выход шестого компаратора соединен со вторым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход седьмого компаратора соединен со вторым входом двадцать шестого элемента И, со вторым, инверсным входом двадцать седьмого элемента И и с D-входом четвертого D-триггера, выход двадцать шестого элемента И соединен с первым входом десятого элемента ИЛИ, выход двадцать седьмого элемента И соединен со вторым входом десятого элемента ИЛИ, выход десятого элемента ИЛИ соединен со вторым входом двадцать восьмого элемента И, выход двадцать восьмого элемента И соединен с первым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с D-входом третьего D-триггера, выход третьего D-триггера является первым выходом блока оценки некодированных бит в режимах 8PSK, выход четвертого D-триггера является вторым выходом блока оценки некодированных бит в режимах 8PSK, причем блок оценки некодированных бит в режимах 16QAM содержит двенадцатый мультиплексор, тринадцатый мультиплексор, восьмой компаратор, девятый компаратор, пятый D-триггер, шестой D-триггер, причем первые входы восьмого компаратора являются первыми входами блока оценки некодированных бит в режимах 16QAM, управляющий вход двенадцатого мультиплексора является третьим входом блока оценки некодированных бит в режимах 16QAM, первые входы данных двенадцатого мультиплексора соединены со вторыми входами данных тринадцатого мультиплексора и с шиной константы -const_16QAM устройства декодирования РТСМ, вторые входы данных двенадцатого мультиплексора соединены с первыми входами данных тринадцатого мультиплексора и с шиной +const_16QAM устройства декодирования РТСМ, управляющий вход тринадцатого мультиплексора является четвертым входом блока оценки некодированных бит в режимах 16QAM, вторые входы девятого компаратора являются вторыми входами блока оценки некодированных бит в режимах 16QAM, выходы двенадцатого мультиплексора соединены со вторыми входами восьмого компаратора, выходы тринадцатого мультиплексора соединены с первыми входами девятого компаратора, выход восьмого компаратора соединен с D-входом пятого D-триггера, выход девятого компаратора соединен с D-входом шестого D-триггера, выход пятого D-триггера является первым выходом блока оценки некодированных бит в режимах 16QAM, выход шестого D-триггера является вторым выходом блока оценки некодированных бит в режимах 16QAM, причем компенсатор фазового сдвига в режимах 8PSK содержит двадцать девятый элемент И, тридцатый элемент И, тридцать первый элемент И, пятый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, тридцать второй элемент И, тридцать третий элемент И, тридцать четвертый элемент И, одиннадцатый элемент ИЛИ, двенадцатый элемент ИЛИ, третий инвертор, четвертый инвертор, пятый инвертор, шестой инвертор, четырнадцатый мультиплексор, шестой элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, седьмой инвертор, восьмой инвертор, пятнадцатый мультиплексор, шестнадцатый мультиплексор, седьмой элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, тридцать пятый элемент И, тридцать шестой элемент И, тридцать седьмой элемент И, тридцать восьмой элемент И, тридцать девятый элемент И, сороковой элемент И, сорок первый элемент И, сорок второй элемент И, сорок третий элемент И, сорок четвертый элемент И, сорок пятый элемент И, сорок шестой элемент И, тринадцатый элемент ИЛИ, четырнадцатый элемент ИЛИ, пятнадцатый элемент ИЛИ, шестнадцатый элемент ИЛИ, девятый инвертор, десятый инвертор, семнадцатый мультиплексор, причем первый вход данных четырнадцатого мультиплексора соединен с первым, инверсным входом двадцать девятого элемента И, с первым входом тридцатого элемента И, с первым входом тридцать первого элемента И, с первым входом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с первым входом тридцать второго элемента И, с первым, инверсным входом тридцать третьего элемента И, с первым, инверсным входом тридцать четвертого элемента И, со входом третьего инвертора, с первым и пятым входами данных пятнадцатого мультиплексора, со входом седьмого инвертора, с первым входом шестого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, со вторым входом седьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, со вторым, инверсным входом тридцать пятого элемента И, со вторым входом тридцать седьмого элемента И, со вторым входом тридцать восьмого элемента И, со вторым, инверсным входом сорокового элемента И, со вторым, инверсным входом сорок первого элемента И, со вторым входом сорок третьего элемента И, со вторым входом сорок четвертого элемента И, со вторым, инверсным входом сорок шестого элемента И и является вторым входом компенсатора фазового сдвига в режимах 8PSK,

второй, инверсный вход двадцать девятого элемента И соединен со вторым входом тридцатого элемента И, с третьим, инверсным входом тридцать второго элемента И, со вторым входом тридцать четвертого элемента И, со вторым входом шестого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с третьим, инверсным входом тридцать пятого элемента И, со вторым входом тридцать шестого элемента И, с третьим входом тридцать восьмого элемента И, со вторым, инверсным входом тридцать девятого элемента И, с третьим, инверсным входом сорок первого элемента И, со вторым входом сорок второго элемента И, с третьим входом сорок четвертого элемента И, со вторым, инверсным входом сорок пятого элемента И и является седьмым входом компенсатора фазового сдвига в режимах 8PSK, третий, инверсный вход двадцать девятого элемента И соединен со вторым входом тридцать первого элемента И, со вторым входом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, со вторым входом тридцать второго элемента И, со вторым, инверсным входом тридцать третьего элемента И и является шестым входом компенсатора фазового сдвига в режимах 8PSK,

выход двадцать девятого элемента И соединен с первым входом одиннадцатого элемента И