Одноканальный корреляционный измеритель частотных искажений

Иллюстрации

Показать всеИзобретение относится к области радиоизмерений и предназначено для оценки частотных искажений случайных сигналов. Измеритель содержит входной мультиплексор, компаратор, N-разрядный регистр сдвига, группу N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, группу N элементов 2И, группу N счетчиков, выходной мультиплексор и блок управления. Особенностью измерителя является применение для оценки частотных искажений знаковых автокорреляционных функций, которые позволили основную часть операций выполнить над одноразрядными операндами. Технический результат заключается в упрощении устройства. 2 н.п. ф-лы, 3 ил.

Реферат

Изобретение относится к области радиоизмерений и предназначено для оценки частотных искажений случайных сигналов.

Прототипом изобретения является корреляционный анализатор частотных свойств линейной системы, который содержит мультиплексор, коррелятор, блок сравнения и блок управления, вход которого является входом запуска анализатора, первым тестовым входом которого служит первый информационный вход мультиплексора, второй информационный вход которого является вторым тестовым входом анализатора, выход мультиплексора соединен с информационным входом коррелятора, выход которого соединен с информационным входом блока сравнения, выход которого является информационным выходом анализатора, адресный вход мультиплексора, тактовый и обнуляющий входы коррелятора, а также входы управления блоком сравнения соединены с соответствующими выходами блока управления, адресный выход которого соединен с единой адресной шиной коррелятора и блока сравнения [Пат. RU 2242013. Опубл. 10.12.2004. Бюл. №34].

Недостатком прототипа является сложность его реализации, что объясняется относительно большими аппаратурными затратами, связанными с вычислениями классических автокорреляционных функций.

Технический результат, достигаемый при использовании настоящего изобретения, заключается в упрощении устройства.

Технический результат достигается тем, что в одноканальный корреляционный измеритель частотных искажений, содержащий входной мультиплексор и блок управления, первый и второй канальные входы входного мультиплексора являются соответственно первым и вторым информационными входами измерителя, адресный вход входного мультиплексора подключен к первому адресному выходу блока управления, согласно изобретению введены компаратор, регистр сдвига, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, группа элементов И, группа реверсивных накапливающих сумматоров, выходной мультиплексор, выход входного мультиплексора соединен с сигнальным входом компаратора, вход опорного напряжения которого соединен с общей шиной, выход компаратора соединен с информационным входом регистра сдвига и с объединенными первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ группы, вторые входы которых соединены с соответствующими выходами регистра сдвига, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ группы подключены к первым входам соответствующих элементов И группы, тактовый вход регистра сдвига соединен с первым тактовым выходом блока управления, со вторым тактовым выходом которого соединены объединенные вторые входы элементов И группы, выходы которых подключены к счетным входам соответствующих реверсивных накапливающих сумматоров, разрядные выходы которых подключены к соответствующим канальным входам выходного мультиплексора, выходы которого являются выходами измерителя, входы управления направлением счета реверсивных накапливающих сумматоров объединены и подключены к соответствующему управляющему выходу блока управления, к выходу обнуления которого подключены объединенные обнуляющие входы реверсивных накапливающих сумматоров, адресный вход выходного мультиплексора подключен ко второму адресному выходу блока управления.

Реверсивный накапливающий сумматор согласно изобретению содержит реверсивный счетчик, суммирующий счетчик, триггер и элемент ИЛИ, выход которого соединен со входом управления направлением счета реверсивного счетчика, счетный вход которого объединен с счетным входом суммирующего счетчика и образует счетный вход сумматора, обнуляющим входом которого являются объединенные обнуляющие входы реверсивного счетчика, суммирующего счетчика и триггера, вход установки в единицу которого соединен с выходом переноса реверсивного счетчика, выход триггера подключен к первому входу элемента ИЛИ, второй вход которого является входом управления направлением счета реверсивного накапливающего сумматора, разрядными выходами суммы которого являются разрядные выходы суммирующего счетчика, а разрядными выходами разности - разрядные выходы реверсивного счетчика.

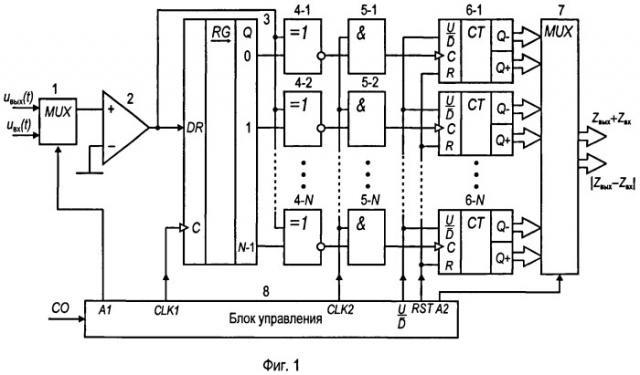

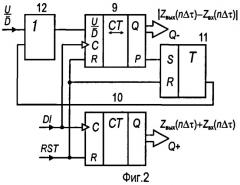

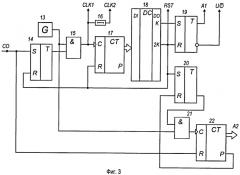

Сущность изобретения поясняется графическим материалом. На фиг.1 показана функциональная схема измерителя. На фиг.2 показана функциональная схема реверсивного накапливающего сумматора. На фиг.3 показана функциональная схема блока управления.

Функциональная схема измерителя (фиг.1) содержит входной мультиплексор 1, компаратор 2, N-разрядный регистр 3 сдвига, группу 4 N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, группу 5 N элементов 2И, группу 6 N реверсивных накапливающих сумматоров, выходной мультиплексор 7 и блок 8 управления. Первый и второй канальные входы входного мультиплексора являются соответственно первым uвых(t) и вторым uвых(t) информационными входами измерителя, адресный вход входного мультиплексора подключен к первому адресному выходу А1 блока 8 управления, выход входного мультиплексора 1 соединен с сигнальным входом компаратора 2, вход опорного напряжения которого соединен с общей шиной, выход компаратора 2 соединен с информационным входом регистра 3 сдвига и с объединенными первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 4-1÷4-N, вторые входы которых соединены с соответствующими выходами регистра 3 сдвига, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 4-1÷4-N подключены к первым входам соответствующих элементов И 5-1+5-N, тактовый вход регистра 3 сдвига соединен с первым тактовым выходом CLK1 блока 8 управления, со вторым тактовым выходом CLK2 которого соединены объединенные вторые входы элементов И 5-1÷5-N, выходы которых подключены к счетным входам соответствующих сумматоров 6-1÷6-N, разрядные выходы которых подключены к соответствующим канальным входам выходного мультиплексора 7, выходы которого являются выходами измерителя, входы управления направлением счета сумматоров 6-1÷6-N объединены и подключены к управляющему выходу блока 8 управления, к выходу обнуления RST которого подключены объединенные обнуляющие входы счетчиков, адресный вход выходного мультиплексора подключен ко второму адресному выходу А2 блока 8 управления.

Функциональная схема реверсивного накапливающего сумматора (фиг.2) содержит реверсивный счетчик 9, суммирующий счетчик 10, триггер 11 и элемент ИЛИ 12, выход которого соединен со входом управления направлением счета реверсивного счетчика 9, счетный вход которого объединен с счетным входом суммирующего счетчика 10 и образует счетный вход С сумматора, обнуляющим входом RST которого являются объединенные обнуляющие входы реверсивного счетчика 9, суммирующего счетчика 10 и триггера 11, вход установки в единицу которого соединен с выходом переноса реверсивного счетчика 9, выход триггера 11 подключен к первому входу элемента ИЛИ 12, второй вход которого является входом управления направлением счета U/D реверсивного накапливающего сумматора, разрядными выходами суммы которого являются разрядные выходы суммирующего счетчика, а разрядными выходами разности - разрядные выходы реверсивного счетчика.

Блок управления (фиг.3) содержит генератор 13 тактовых импульсов, триггеры 14, 19, 20, элементы 2И 15, 21, элемент 16 задержки, счетчики 17, 22 и дешифратор 18. Запускающим входом СО блока является вход установки в единицу триггера 14, обнуляющий вход которого объединен с обнуляющим входом счетчика 17, триггера 19 и со входом установки в единицу триггера 20 и подключен к 2К-му выходу дешифратора 18, который является выходом RST блока, обнуляющий вход счетчика 22 подключен к запускающему входу СО блока, а обнуляющий вход триггера 20 подключен к выходу переноса Р счетчика 22, счетный вход которого соединен с выходом элемента 2И 21, первый вход которого соединен с выходом триггера 20, а второй вход соединен с выходом генератора 13 тактовых импульсов, с выходом которого также соединен первый вход элемента 2И 15, второй вход которого соединен с выходом триггера 14, выход элемента 2И 15 соединен со счетным входом счетчика 17 и является первым тактовым выходом CLK1 блока, вторым тактовым входом CLK2 которого является выход элемента 16 задержки, вход которого подключен к первому тактовому выходу CLK1 блока, информационный выход счетчика 17 соединен с информационным входом дешифратора 18, К-й выход которого соединен со входом установки в единицу триггера 19, а 2К-й выход - с обнуляющим входом триггера 19 и входом установки в единицу триггера 20, прямой выход которого является первым адресным выходом А1 блока, а инвертирующий выход является управляющим выходом блока, вторым адресным выходом А2 которого является информационный выход счетчика 22.

Принцип действия измерителя состоит в следующем.

На первом этапе, на обработку, через входной аналоговый мультиплексор 1, направляется сигнал uвых(t). Для этого в начальном состоянии на адресном входе мультиплексора 1 поддерживают уровень логического нуля (А1=0). Для запуска измерителя на вход управления СО подают запускающий импульс, в ответ на что блок 8 управления начинает тактирование регистра 3 сдвига, выполняющего функции многоотводной линии задержки с шагом Δτ, и группы 5 элементов И (последовательности CLK1 и CKL2). Одновременно на выходе блока 8 управления устанавливается высокий логический уровень (=1), переводящий реверсивные накапливающие сумматоры группы 6 в режим сложения. В течение первого этапа, на интервале наблюдения Тр, результаты совпадения знаков N сигналов суммируются в вышеупомянутых накапливающих сумматорах. После чего, то есть по истечении времени Тр, блок 8 управления переводит мультиплексор 1 в режим коммутации на его выход сигнала uвх(t) (A1=1), а реверсивные накапливающие сумматоры группы 6 - в режим вычитания (=0). Коррелятор переходит ко второму этапу, отличающемуся от первого тем, что вместо сложения с накоплением знаковых совпадений происходит их вычитание из уже накопленных сумм Zвых(nΔτ), находящихся в памяти накапливающих сумматоров группы 6. Кроме того, параллельно в накапливающих сумматорах группы 6 происходит сложение величин Zвых(nΔτ) и ZBX(nΔτ). По окончании второго этапа, при обязательном условии, что интервалы наблюдений Тр на первом и втором этапах равны, на выходах реверсивных накапливающих сумматоров группы 6 будут зарегистрированы величины

и

соответствующие N сигналам или N реверсивным накапливающим сумматорам. Далее, что следует отнести уже к третьему этапу, подача тактовых импульсов CLK1, CLK2 прекращается и начинается последовательный вывод полученных данных через сдвоенный мультиплексор 7 (под сдвоенным мультиплексором понимают два идентичных мультиплексора, входы адресных селекторов которых объединены, что позволяет одновременно коммутировать два потока данных). С этой целью блок 8 управления формирует на выходе А2 соответствующий адресный код. После вывода всей информации содержимое сумматоров группы 6 обнуляется, и коррелятор готов к следующему циклу измерений.

Оценку частотных искажений находят из выражения

где ƒ0(P(nΔτ)) - относительный показатель, функция, по значению которой судят о наличии и объеме искажений, а Р(nΔτ) - вероятность совпадения знаков сравниваемых процессов.

Величина ƒ0(P(nΔτ)) принимает значения от нуля до единицы. При отсутствии частотных искажений ƒ0(P(nΔτ))=0. Максимальным искажениям соответствует равенство: ƒ0(P(nΔτ))=1.

Особенностью измерителя являются реверсивные накапливающие сумматоры, позволившие отказаться от процессов вычитания, выделения модуля и сложения при обработке результатов, полученных на выходе коррелятора. Работа реверсивного накапливающего сумматора сводится к суммированию обеими счетчиками 9 и 10 импульсов, поступающих на вход С на первом этапе работы коррелятора (=l) и вычитанию из содержимого счетчика 9 на втором этапе (=0), в то время как счетчик 10 продолжает их суммировать. Если в процессе вычитания окажется, что Zвх(nΔτ)>Zвых(nΔτ), на выходе переноса Р счетчика 9, в определенный момент времени появится импульс, опрокидывающий триггер 11 и переводящий таким образом счетчик 9 в режим сложения. Начатое таким образом сложение останавливается после того, как счетчиком 9 будет накоплено число, равное разности Zвх(nΔτ)-Zвых(nΔτ). В результате к концу второго этапа (в идеале через интервал времени 2TР) на выходе счетчика 9 сформируется код модуля разности величин Zвых(nΔτ), Zвх(nΔτ), а на выходе счетчика 10 - код их суммы.

Блок 8 управления (см. фиг.3) работает следующим образом.

В исходном состоянии на выходе А1 установлен низкий логический уровень, на выходе - высокий, а на выходах CLK1, CLK2 отсутствуют тактовые импульсы. Для запуска блока на вход СО подают короткий импульс, по которому устанавливается в единицу триггер 14. В связи с чем на выходах CLK1, CLK2 появляются последовательности тактовых импульсов, вырабатываемые генератором 13. Одновременно начинается счет импульсов счетчиком 17, состояние которого непрерывно отслеживается дешифратором 18. После отсчета k-го импульса, т.е. по истечении времени Тр, на k-ом выходе дешифратора 18 появляется высокий логический уровень, который переводит триггер 19 в состояние логической единицы на выходе и, следовательно, меняется распределение уровней на выходах Al, . Продолжающийся счет импульсов счетчиком 17 после прохождения 2k импульсов приводит к перепаду напряжений на соответствующем выходе дешифратора 18, в ответ на что начинается подача тактовых импульсов на счетный вход счетчика 22, служащего для формирования адресного кода управления мультиплексором 7 (см. фиг.1). В то же время обнуляется триггер 19 и распределение уровней на выходах А1, блока возвращается к исходному. Кроме того, обнуляется триггер 14 и счетчик 17, а через время, необходимое для переполнения счетчика 22, и триггер 20. После чего блок управления готов к началу следующего цикла формирования управляющих сигналов.

Элемент 16 задержки обеспечивает относительный сдвиг во времени последовательностей тактовых импульсов CLK1, CLK2, что необходимо для разнесения во времени моментов переключения регистра 3 и сумматоров группы 6. Время задержки выбирают меньше периода следования тактовых импульсов, но больше длительности их фронтов.

1. Одноканальный корреляционный измеритель частотных искажений, содержащий входной мультиплексор и блок управления, первый и второй канальные входы входного мультиплексора являются соответственно первым и вторым информационными входами измерителя, адресный вход входного мультиплексора подключен к первому адресному выходу блока управления, отличающийся тем, что в него введены компаратор, регистр сдвига, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, группа элементов И, группа реверсивных накапливающих сумматоров, выходной мультиплексор, выход входного мультиплексора соединен с сигнальным входом компаратора, вход опорного напряжения которого соединен с общей шиной, выход компаратора соединен с информационным входом регистра сдвига и с объединенными первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ группы, вторые входы которых соединены с соответствующими выходами регистра сдвига, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ группы подключены к первым входам соответствующих элементов И группы, тактовый вход регистра сдвига соединен с первым тактовым выходом блока управления, со вторым тактовым выходом которого соединены объединенные вторые входы элементов И группы, выходы которых подключены к счетным входам соответствующих реверсивных накапливающих сумматоров, разрядные выходы которых подключены к соответствующим канальным входам выходного мультиплексора, выходы которого являются выходами измерителя, входы управления направлением счета реверсивных накапливающих сумматоров объединены и подключены к соответствующему управляющему выходу блока управления, к выходу обнуления которого подключены объединенные обнуляющие входы реверсивных накапливающих сумматоров, адресный вход выходного мультиплексора подключен ко второму адресному выходу блока управления.

2. Реверсивный накапливающий сумматор, отличающийся тем, что содержит реверсивный счетчик, суммирующий счетчик, триггер и элемент ИЛИ, выход которого соединен со входом управления направлением счета реверсивного счетчика, счетный вход которого объединен с счетным входом суммирующего счетчика и образует счетный вход сумматора, обнуляющим входом которого являются объединенные обнуляющие входы реверсивного счетчика, суммирующего счетчика и триггера, вход установки в единицу которого соединен с выходом переноса реверсивного счетчика, выход триггера подключен к первому входу элемента ИЛИ, второй вход которого является входом управления направлением счета реверсивного накапливающего сумматора, разрядными выходами суммы которого являются разрядные выходы суммирующего счетчика, а разрядными выходами разности - разрядные выходы реверсивного счетчика.