Компаратор двоичных чисел

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления. Техническим результатом является уменьшение аппаратурных затрат. Устройство содержит два элемента задержки, два элемента И, четыре элемента ИЛИ, два элемента НЕ. 1 ил., 1 табл.

Реферат

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны компараторы двоичных чисел (см., например, рис.6-19а на стр.286 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974), которые выполняют распознавание отношений х1=х2, х1≠х2, где х1=x1(n-1)…x10, х2=x2(n-1)…x20 - n-разрядные двоичные числа, задаваемые двоичными сигналами х10,…,x1(n-1),x20,…,x2(n-1)∈{0,1}, причем сигналы x1(n-j), x2{n-j) подаются на упомянутые компараторы в j-й момент времени, а сигналы xi(n-1) и xi0

определяют значения соответственно старшего и младшего разрядов числа xi.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных компараторов двоичных чисел, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется распознавание отношений xl>х2, x1<x2.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип компаратор двоичных чисел (рис.6-20 на стр.288 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974), который содержит элементы НЕ, элементы И, элементы ИЛИ, элементы задержки и выполняет распознавание отношений x1=x2, x1>х2, x1<x2. где х1=x1(n-1)…x10, х2=x2(n-1)…x20 - n-разрядные двоичные числа, задаваемые двоичными сигналами х10,…,x1(n-1),x20,…,x2(n-1)∈{0,1}, причем сигналы x1(n-j), x2(n-j) подаются на соответствующие входы прототипа в j-й момент времени, а сигналы xi(n-1) и xi0 определяют значения соответственно старшего и младшего разрядов числа xi.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся большие аппаратурные затраты.

Техническим результатом изобретения является уменьшение аппаратурных затрат при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в компараторе двоичных чисел, содержащем два элемента НЕ, два элемента И, два элемента ИЛИ и два элемента задержки, особенность заключается в том, что в него дополнительно введены два элемента ИЛИ, причем первый, второй входы и выход i-го элемента ИЛИ соединены соответственно с выходом i-го элемента И, первым входом (i+2)-го элемента ИЛИ и входом i-го элемента задержки, подключенного выходом к первому входу (i+2)-го элемента ИЛИ, второй вход и выход которого соединены соответственно с первым входом i-го элемента И и входом i-го элемента НЕ, подключенного выходом к второму входу (3-i)-го элемента И, первый вход которого соединен с (3-i)-м входом компаратора двоичных чисел, подключенного i-м выходом к выходу i-го элемента ИЛИ.

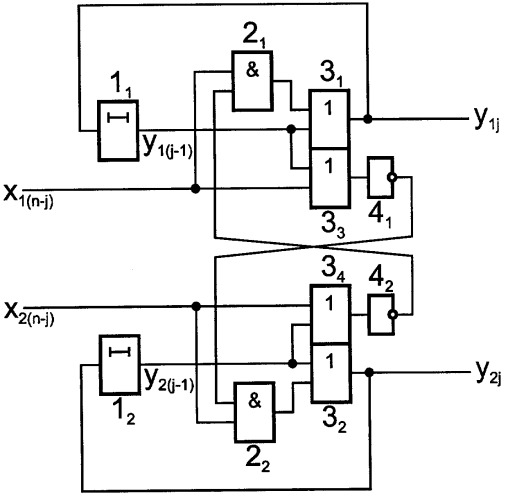

На чертеже представлена схема предлагаемого компаратора двоичных чисел.

Компаратор двоичных чисел содержит два элемента задержки 11, 12, два элемента И 21, 22, четыре элемента ИЛИ 31, 32, 33, 34, два элемента НЕ 41, 42, причем первый, второй входы и выход элемента 3i соединены соответственно с выходом элемента 2i, первым входом элемента 3i+2 и входом элемента 1i подключенного выходом к первому входу элемента 3i+2, второй вход и выход которого соединены соответственно с первым входом элемента 2i и входом элемента 4i, подключенного выходом к второму входу элемента 23-i, первый вход которого соединен с (3-i)-м входом компаратора двоичных чисел, подключенного i-м выходом к выходу элемента 3i.

Работа предлагаемого компаратора двоичных чисел осуществляется следующим образом. На его первый и второй входы в j-й момент времени подаются соответственно двоичные сигналы x1(n-j)∈{0,1} и x2(n-j)∈{0,1}, которые задают значения (n-j)-х разрядов подлежащих сравнению n-разрядных двоичных чисел х1=x1(n-1)…x10, и x2=x2(n-1)…x20. Здесь сигналы xi(n-l) и xi0 определяют значения соответственно старшего и младшего разрядов числа xi. Сигнал на выходе элемента задержки 1i в j-й момент времени равен сигналу, который действовал на его входе в (j-1)-й момент времени, а уi0=0 (в качестве элемента задержки может быть использован D-триггер). Тогда сигналы на первом, втором выходах предлагаемого компаратора будут определяться выражениями

где у10=у20=0. В представленной ниже таблице приведены значения реализуемых выражениями (1) функций на всех возможных наборах значений их аргументов.

| уl(j-l) | у2(j-l) | xl(n-j) | x2(n-j) | уlj | У2j |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 1 | 0 |

Анализ данных, приведенных в таблице, позволяет заключить, что: 1) если уl(j-l)=у2(j-1)=0 и x1(n-j)=x2(n-j), то уlj=у2j=0; 2) если уl(j-l)=у2(j-1)=0 и xl(n-j)>x2(n-j) (у1(j-l)=у2(j-l)=0 и xl(n-j)<x2(n-j)), то уlj=1 и у2j=0 (уlj=0 и у2j=1); 3) если у1(j-l)=1 и у2(j-l)=0 (у1(j-l)=0 и у2(j-l)=1),то у1j=1 и у2j=0 (у1j=0 и у2j=1) Таким образом, когда х1=х2 либо х1>х2 либо х1<х2 соответственно имеем у1n=у2n=0 либо у1n=1, у2n=0 либо у1n=0, у2n=1. При этом предлагаемый компаратор содержит десять элементов. Отметим, что в состав прототипа входят двенадцать элементов.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый компаратор двоичных чисел обладает меньшими по сравнению с прототипом аппаратурными затратами и выполняет распознавание отношений x1=х2, х1>х2, х1<х2, где х1=x1(n-1)…x10, х2=х2(n-1)…х20 - n-разрядные двоичные числа, задаваемые двоичными сигналами х10,…,x1(n-1), x20,…,x2(n-1)∈{0,1}, причем сигналы x1(n-j), x2(n-j) подаются на соответствующие входы предлагаемого компаратора в j-й момент времени, а сигналы xi(n-1) и xi0 определяют значения соответственно старшего и младшего разрядов числа xi.

Компаратор двоичных чисел, содержащий два элемента НЕ, два элемента И, два элемента ИЛИ и два элемента задержки, отличающийся тем, что в него дополнительно введены два элемента ИЛИ, причем первый, второй входы и выход i-го элемента ИЛИ соединены соответственно с выходом i-го элемента И, первым входом (i+2)-го элемента ИЛИ и входом i-го элемента задержки, подключенного выходом к первому входу (i+2)-го элемента ИЛИ, второй вход и выход которого соединены соответственно с первым входом i-го элемента И и входом i-го элемента НЕ, подключенного выходом к второму входу (3-i)-го элемента И, первый вход которого соединен с (3-i)-м входом компаратора двоичных чисел, подключенного i-м выходом к выходу i-го элемента ИЛИ.