Дифференциальный усилитель с повышенным входным сопротивлением

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов датчиков с высоким внутренним сопротивлением, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), широкополосных и избирательных усилителях, фильтрах и т.п.). Технический результат: повышение входного сопротивления. Дифференциальный усилитель (ДУ) содержит входной параллельно-балансный каскад (ПБК) (1) на биполярных транзисторах (Т), имеющий первый (2) и второй (3) входы, первый (4) и второй (5) основные токовые выходы, связанные с цепью нагрузки (6), первый (7) и второй (8) вспомогательные Т, базы которых соединены с первым (2) и вторым (3) входами ПБК (1), а эмиттеры соединены друг с другом и подключены к выходу (9) вспомогательного токового зеркала (ТЗ) (10). ПБК (1) содержит первый (11) дополнительный токовый выход, синфазный с первым (4) основным токовым выходом, второй (12) дополнительный токовый выход, синфазный со вторым (5) основным токовым выходом, причем первый (11) и второй (12) дополнительные токовые выходы связаны с эмиттером дополнительного Т (13), база которого соединена со входом (14) ТЗ (10), коллектор первого Т (7) связан со вторым (3) входом ПБК (1), а коллектор второго Т (8) связан с первым (2) входом ПБК (1). 4 з.п. ф-лы, 8 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов датчиков с высоким внутренним сопротивлением, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), широкополосных и избирательных усилителях, фильтрах и т.п.).

Известны схемы дифференциальных усилителей (ДУ) с параллельным включением двух параллельно-балансных каскадов на разнотипных транзисторах [1-19]. На их модификации выдано более 20 патентов для ведущих микроэлектронных фирм мира. Дифференциальные усилители данного класса, наряду с одиночными параллельно-балансными каскадами, стали основным усилительным элементом многих микросхем аналоговых интерфейсов. Предлагаемое изобретение относится к данному подклассу устройств.

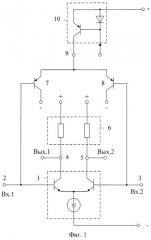

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, представленный в устройстве по патенту США №5.153.529, содержащий входной параллельно-балансный каскад 1 на биполярных транзисторах, имеющий первый 2 и второй 3 входы, первый 4 и второй 5 основные токовые выходы, связанные с цепью нагрузки 6, первый 7 и второй 8 вспомогательные транзисторы, базы которых соединены с первым 2 и вторым 3 входами входного параллельно-балансного каскада 1, а эмиттеры соединены друг с другом и подключены к выходу 9 вспомогательного токового зеркала 10.

Данная структура ДУ присутствует также в патентах US №4.555.673, 5.610.557, 4.797.631, 6.963.244, 4.358.739, 5.153.529.

Существенный недостаток известного ДУ состоит в том, что он имеет небольшое входное дифференциальное сопротивление (Rвх), зависящее от абсолютных значений коэффициента усиления по току базы (β) применяемых транзисторов и их статического режима. Для повышения в известных ДУ применяется местная отрицательная обратная связь (вводятся эмиттерные резисторы). Однако при этом ухудшаются многие параметры ДУ - коэффициент усиления по напряжению, напряжение смещения нуля, коэффициент подавления помехи по питанию, крутизна усиления ДУ и др.

Основная цель предлагаемого изобретения состоит в повышении на один-два порядка входного сопротивления ДУ без ухудшения его крутизны и ряда других параметров.

Поставленная цель достигается тем, что в дифференциальном усилителе (фиг.1), содержащем входной параллельно-балансный каскад 1 на биполярных транзисторах, имеющий первый 2 и второй 3 входы, первый 4 и второй 5 основные токовые выходы, связанные с цепью нагрузки 6, первый 7 и второй 8 вспомогательные транзисторы, базы которых соединены с первым 2 и вторым 3 входами входного параллельно-балансного каскада 1, а эмиттеры соединены друг с другом и подключены к выходу 9 вспомогательного токового зеркала 10, предусмотрены новые элементы и связи - входной параллельно-балансный каскад 1 содержит первый 11 дополнительный токовый выход, синфазный с первым 4 основным токовым выходом, второй 12 дополнительный токовый выход, синфазный со вторым 5 основным токовым выходом, причем первый 11 и второй 12 дополнительные токовые выходы связаны с эмиттером дополнительного транзистора 13, база которого соединена со входом 14 вспомогательного токового зеркала 10, коллектор первого 7 вспомогательного транзистора связан со вторым 3 входом входного параллельно-балансного каскада 1, а коллектор второго 8 вспомогательного транзистора связан с первым 2 входом входного параллельно-балансного каскада 1.

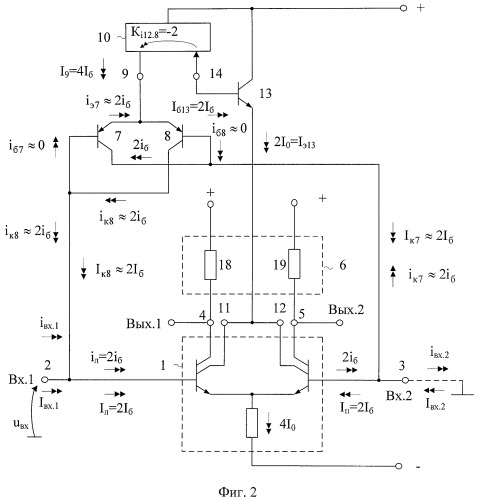

На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения.

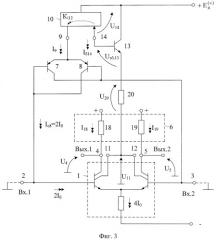

На фиг.3 представлена схема заявляемого устройства в соответствии с п.2 формулы изобретения.

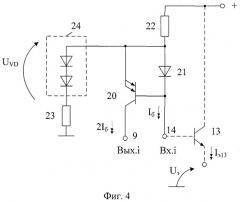

На фиг.4 представлена схема токового зеркала 10 заявляемого устройства в соответствии с п.4 формулы изобретения.

На фиг.5 представлена схема токового зеркала 10 заявляемого устройства в соответствии с п.5 формулы изобретения.

На фиг.6 приведена схема, соответствующая фиг.3, в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НЛП «Пульсар».

На фиг.7 приведены графики температурной зависимости входного тока ДУ-прототипа при R3=1,1 кОм и ДУ, соответствующего фиг.1, которые показывают, что при комнатной температуре предлагаемое устройство имеет более чем в 40 раз меньший входной ток.

На фиг.8 показаны частотные зависимости входных сопротивлений заявляемого (фиг.6 при R3=1,1 кОм) и известного дифференциальных усилителей, из которых следует, что входное сопротивление предлагаемой схемы фиг.6 в 150-200 раз больше, чем в ДУ-прототипе.

Дифференциальный усилитель (фиг.2) содержит входной параллельно-балансный каскад 1 на биполярных транзисторах, имеющий первый 2 и второй 3 входы, первый 4 и второй 5 основные токовые выходы, связанные с цепью нагрузки 6, первый 7 и второй 8 вспомогательные транзисторы, базы которых соединены с первым 2 и вторым 3 входами входного параллельно-балансного каскада 1, а эмиттеры соединены друг с другом и подключены к выходу 9 вспомогательного токового зеркала 10. Входной параллельно-балансный каскад 1 содержит первый И дополнительный токовый выход, синфазный с первым 4 основным токовым выходом, второй 12 дополнительный токовый выход, синфазный со вторым 5 основным токовым выходом, причем первый 11 и второй 12 дополнительные токовые выходы связаны с эмиттером дополнительного транзистора 13, база которого соединена со входом 14 вспомогательного токового зеркала 10, коллектор первого 7 вспомогательного транзистора связан со вторым 3 входом входного параллельно-балансного каскада 1, а коллектор второго 8 вспомогательного транзистора связан с первым 2 входом входного параллельно-балансного каскада 1.

На фиг.3, в соответствии с п.2 формулы изобретения, первый 11 и второй 12 дополнительные токовые выходы входного параллельно-балансного каскада связаны с эмиттером дополнительного транзистора 13 через вспомогательный двухполюсник 20.

Кроме этого, в соответствии с п.3 формулы изобретения, коэффициент передачи по току вспомогательного токового зеркала 10 схем фиг.2 и фиг.3 близок к двум единицам.

На фиг.4, в соответствии с п.4 формулы изобретения, дополнительное токовое зеркало 10 содержит первый транзистор 20, база которого соединена со входом токового зеркала 14, а коллектор - с его выходом 9, дополнительный p-n-переход 21, первый 22 и второй 23 вспомогательные резисторы, первую цепь смещения потенциалов на основе p-n-переходов 24, причем первый вспомогательный резистор 22, первая цепь смещения потенциалов на основе p-n-переходов 24 и второй вспомогательный резистор 23 соединены последовательно, общий узел первой цепи смещения потенциалов на основе p-n-переходов 24 и первого вспомогательного резистора 22 соединен с эмиттером первого транзистора 20 и первым выводом дополнительного p-n-перехода 21, второй вывод которого соединен со входом 14 токового зеркала, причем площадь p-n-перехода транзистора 20 приблизительно в два раза больше площади эмиттерной области дополнительного p-n-перехода 21.

На фиг.5, в соответствии с п.5 формулы изобретения, дополнительное токовое зеркало 10 содержит второй 25 и третий 26 транзисторы, база второго транзистора 25 соединена с эмиттером третьего транзистора 26 и первым выводом дополнительного двухполюсника 27, коллектор второго транзистора 25 связан со входом токового зеркала 14 и базой третьего транзистора 26, а коллектор третьего транзистора 26 подключен к выходу токового зеркала 9, третий 28 и четвертый 29 дополнительные резисторы, и вторую цепь смещения потенциалов на основе p-n-переходов 30, причем третий дополнительный резистор 28, вторая цепь смещения потенциалов на основе p-n-переходов 30 и четвертый дополнительный резистор 29 соединены последовательно, а общий узел второй цепи смещения потенциалов на основе p-n-переходов 30 и третьего дополнительного резистора 28 подключен к эмиттеру второго транзистора 25 и второму выводу дополнительного двухполюсника 27.

Рассмотрим работу ДУ (фиг.2).

В статическом режиме статические входные токи ДУ Iвх.1 и Iвх.2 определяются разностью токов базы входных транзисторов дифференциального каскада 1 и коллекторных токов транзисторов 7 и 8:

где Iк7, Iк8 - коллекторные токи транзисторов 7 и 8;

Iл - входной статический ток каскада 1 по левому входу;

Iп - входной статический ток каскада 1 по его правому входу.

Если учесть, что коэффициент передачи тока подсхемы 10 близок к двум единицам (Ki12=2), а Iл≈Iк8=Iп=I7=2Iб, то из (1) и (2) следует, что входные токи ДУ фиг.2 близки к нулю: Iвх.1≈0, Iвх.2≈0. Это первое достоинство предлагаемой схемы.

Второе преимущество предлагаемого устройства состоит в том, что в схеме фиг.2 обеспечивается компенсация не только статических входных токов Iвх.1 и Iвх.2, но и их приращений iвх.1 и iвх.2. Как следствие, входное сопротивление ДУ фиг.2 для переменного тока существенно повышается. Действительно, при увеличении напряжения uвх на входе 2 относительно входа 3 увеличивается ток базы каждого из двух параллельно включенных входных транзисторов каскада 1:

где ;

β1-2=β1=β2 - коэффициент усиления по току базы входных транзисторов ДУ каскада 1;

rэ1, rэ2 - сопротивления эмиттерных переходов по току базы входных транзисторов каскада 1;

φт=25 мВ - температурный потенциал;

IΣ=4I0 - суммарный ток общей эмиттерной цепи транзисторов каскада 1.

Поэтому переменная составляющая суммарного тока базы параллельно включенных входных транзисторов каскада 1:

С другой стороны, приращения коллекторных токов транзисторов 7 и 8

где rэ8=rэ7 - сопротивления эмиттерных переходов транзисторов 8 и 7.

Причем

где I9 - выходной суммарный ток токового зеркала 10.

Если учесть, что за счет токового зеркала 10 (Ki12.8=2) обеспечивается равенство

то уравнение (6) можно представить в следующем виде

где β13 - коэффициент усиления по току базы транзистора 13.

Поэтому коллекторные токи транзисторов 7 и 8, а также суммарные входные токи ДУ iвх.1 и iвх.2 относительно узлов 2 и 3:

где iл, iп - переменные входные токи ДУ без цепей компенсации. После преобразований (10) и (11) находим, что входной ток узла 2

Поэтому входная проводимость предлагаемого ДУ на переменном токе

Так как β1-2≈β13, то из (13) следует, что в предлагаемой схеме увх существенно уменьшается (входное сопротивление растет).

В ДУ-прототипе фиг.1 входная проводимость не лучше, чем

Следовательно, в заявляемом ДУ входное сопротивление увеличивается в Ny-раз, где

Эффективность предлагаемого технического решения существенно зависит от точности разделения статического тока общей эмиттерной цепи каскада 1 (IΣ=4I0) между выходами 4 и 11, 5 и 12. Если эмиттерный ток транзистора 13 окажется меньше, чем суммарный ток в узлах 4 и 5 ДУ фиг.2, то даже при β13=β1-2 в схеме фиг.2 будет наблюдаться «недокомпенсация» статического входного тока каскада 1, так как Iк8<Iл. При этом следует заметить, что строго заданный коэффициент деления тока Kd=Iэ13/IΣ=0,5 будет реализован только в том случае, если статические потенциалы выходов 4, 11(12), 5 одинаковы. Если это требование не выполняется, то вследствие эффекта Эрли Kd≠0,5, что несколько ухудшает выигрыш по входному сопротивлению и входному току. Для устранения этого эффекта в схеме фиг.3 вводится резистор 20, который выбирается таким образом, чтобы обеспечить равенство

где U4, U5 - напряжения в узлах 4, 5;

- напряжение питания;

U14 - статическое напряжение на входе токового зеркала 10;

Uэб.13 - напряжение эмиттер-база транзистора 13;

R20 - сопротивление резистора 20.

Предельная температурная стабильность входного статического тока в схеме фиг.3 реализуется в том случае, когда во всем диапазоне рабочих температур выполняется условие U11=U4=U5. Однако в практических схемах токовых зеркал 10 их входное статическое напряжение U13, так же, как и напряжение Uэб.13, уменьшается под действием температуры, что приводит к нарушению баланса U11≠U4=U5 и, следовательно, к появлению дополнительного составляющего дрейфа входного тока ДУ и ухудшению эффекта компенсации Rвх. В этой связи в некоторых случаях авторы рекомендуют применять специальные токовые зеркала фиг.4 и фиг.5, в которых напряжение на входе U14 (фиг.3) изменяется за счет диодной цепи 24 таким образом, чтобы напряжение на эмиттере транзистора 13 и, следовательно, напряжение на выходах 11 и 12 ДУ фиг.2 (фиг.3) было температурно стабильным. Это позволяет получить предельные значения коэффициента Ny (15).

Полученные выше теоретические выводы подтверждаются результатами моделирования известной и предлагаемой схем в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» (фиг.8). При этом заявляемый ДУ имеет более чем на два порядка лучшие значения входного сопротивления. Данный результат обеспечивается без ухудшения других параметров ДУ-крутизны и напряжения смещения нуля. Кроме этого, статические входные токи заявляемого ДУ значительно меньше, чем в схеме ДУ-прототипа (фиг.7).

Литература

1. Патент Японии JP 8222972.

2. Патентная заявка США №2004/0174216.

3. Патент США №6.963.244.

4. Патент США №6.420.931.

5. Патент США №6.222.416.

6. Патент США №5.880.639.

7. Патент США №5.610.557.

8. Патент США №5.153.529.

9. Патент Японии JP №7050528.

10. Патент США №6.191.619.

11. Патент США №6.163.290.

12. Патент США №5.814.953.

13. Патент США №5.714.906.

14. Патент США №5.523.718.

15. Патент США №5.515.005.

16. Патент США №5.293.136.

17. Патент США №4.636.743.

18. Патент США №4.783.637.

19. Матавкин В.В. Быстродействующие операционные усилители. - М., Радио и связь, 1989. - С.101-103. - Рис.6.11 (стр.103).

1. Дифференциальный усилитель с повышенным входным сопротивлением, содержащий входной параллельно-балансный каскад (1) на биполярных транзисторах, имеющий первый (2) и второй (3) входы, первый (4) и второй (5) основные токовые выходы, связанные с цепью нагрузки (6), первый (7) и второй (8) вспомогательные транзисторы, базы которых соединены с первым (2) и вторым (3) входами входного параллельно-балансного каскада (1), а эмиттеры соединены друг с другом и подключены к выходу (9) вспомогательного токового зеркала (10), отличающийся тем, что входной параллельно-балансный каскад (1) содержит первый (11) дополнительный токовый выход, синфазный с первым (4) основным токовым выходом, второй (12) дополнительный токовый выход, синфазный со вторым (5) основным токовым выходом, причем первый (11) и второй (12) дополнительные токовые выходы связаны с эмиттером дополнительного транзистора (13), база которого соединена со входом (14) вспомогательного токового зеркала (10), коллектор первого (7) вспомогательного транзистора связан со вторым (3) входом входного параллельно-балансного каскада (1), а коллектор второго (8) вспомогательного транзистора связан с первым (2) входом входного параллельно-балансного каскада (1).

2. Дифференциальный усилитель по п.1, отличающийся тем, что первый (11) и второй (12) дополнительные токовые выходы входного параллельно-балансного каскада связаны с эмиттером дополнительного транзистора (13) через вспомогательный двухполюсник (20).

3. Устройство по п.1, отличающееся тем, что коэффициент передачи по току вспомогательного токового зеркала (10) близок к двум единицам.

4. Дифференциальный усилитель по п.1, отличающийся тем, что дополнительное токовое зеркало (10) содержит первый транзистор (20), база которого соединена со входом токового зеркала (14), а коллектор - с его выходом (9), дополнительный p-n переход (21), первый (22) и второй (23) вспомогательные резисторы, первую цепь смещения потенциалов на основе p-n переходов (24), причем первый вспомогательный резистор (22), первая цепь смещения потенциалов на основе p-n переходов (24) и второй вспомогательный резистор (23) соединены последовательно, общий узел первой цепи смещения потенциалов на основе p-n переходов (24) и первого вспомогательного резистора (22) соединен с эмиттером первого транзистора (20) и первым выводом дополнительного p-n перехода (21), второй вывод которого соединен со входом (14) токового зеркала, причем площадь р-n перехода транзистора (20) приблизительно в два раза больше площади эмиттерной области дополнительного p-n перехода (21).

5. Дифференциальный усилитель по п.1, отличающийся тем, что дополнительное токовое зеркало (10) содержит второй (25) и третий (26) транзисторы, база второго транзистора (25) соединена с эмиттером третьего транзистора (26) и первым выводом дополнительного двухполюсника (27), коллектор второго транзистора (25) связан со входом токового зеркала (14) и базой третьего транзистора (26), а коллектор третьего транзистора (26) подключен к выходу токового зеркала (9), третий (28) и четвертый (29) дополнительные резисторы, и вторую цепь смещения потенциалов на основе p-n переходов (30), причем третий дополнительный резистор (28), вторая цепь смещения потенциалов на основе p-n переходов (30) и четвертый дополнительный резистор (29) соединены последовательно, а общий узел второй цепи смещения потенциалов на основе p-n переходов (30) и третьего дополнительного резистора (28) подключен к эмиттеру второго транзистора (25) и второму выводу дополнительного двухполюсника (27).