Преобразователь сдвига фазы во временнойинтервал

Иллюстрации

Показать всеРеферат

оийдветена346

О П И С А Н И Е 239385

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства М

Заявлено 13,Х1.1967 (№ 1196763/26-9) Кл. 21ат, 36/20

" присоединением заявки №

Комитет по делам изобретений и открытий при Совете Министров

СССР

Приоритет

Опубликовано 18.111.1969. Бюллетень № 11

МПК Н 03k

УД К 621.376,4 (088.8) Дата опубликования описания 24Х11.1969

Авторы изобретения

Ю. М. Титов и Е. П. Попечителев

Заявитель

Ленинградский электротехнический институт им. В. И. Ульянова (Ленина) ПРЕОБРАЗОВАТЕЛЬ СДВИГА ФАЗЪ1 ВО ВРЕМЕННОЙ

ИНТЕРВАЛ

Известнь!е преобразователи сдвига фазы во временной интервал содержат две !пороговые схемы с равными пороговыми уровнями. ВыХОДЫ ПОРОГОВЫХ СХЕМ ПОДКЧ10ЧЕНЫ К СХЕМЕ ВЫ читания, на выходе которой фзрмируется прямоугольный импульс, длительностью равной сдвигу фа между измеряемыми,напряжениями.

Основная погрешность известных преобразователей вызвана необходимостью и сложностью построепия двух пороговых схем с аасолютно одинаковыми пороговыми уровнями.

Цель предлагаемого преобразователя — получение линейной характеристики преобразования и расширение диапазона преобразования.

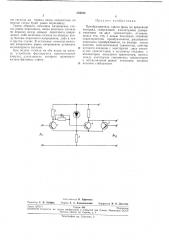

Дост11гается это за счет построения схемы иа трех транзисторах, два пз которых являются входными и выполняют функции амлитудных дискриминаторов, а третий (выходно1!) совместно с транзистором одного из дискриминаторов образует схему вычитания.

Транзисторы имеют общий эмиттерный резистор, к эмиттерам указанных транзисторов подключен катод стабилитрона, анод которого подключен к потенциальной шине исто !ника питания, коллектор и эмиттер входного транзистора соединены соответственно с коллектором и эхпттером выходного транзистора.

На чертеже показано схематически предлагае»ое устройство. В отсутствии входных сиг5 налов транзисторы 1 и 2 заперты падением напряжения на резисторе !, а транзистор 4 открыт и насыщен, что обеспечивается неоОхадимы» базовым таком через резисторы 5 и 6.

При подаче на базу транзистора 1 входного

1О сигнала схема работает как обычное пороговое l строиства, так как закрыты и ТраН311сТор

2 не оказывает никакого влияния на ее работу, До тех пор, пока величина входного сигнала не превысит пороговый уровень, выход15 ное напряжение равно пороговому уровню.

Как только входной сигнал IIB базе транз;1стара 1 превысит пороговый уровень, в схеме происходит процесс опрок!1дывания, транзистор 1 переход;1т в режим насыщения, а тран20 зистор 4 закрывается.

Выходное напряжение будет равно напряжениlо иcTQ IHIIÊ2 ко, IлскTopíÎÃÎ питанl!ÿ В течение всего времени превышения входным сигналом порогового уровня.

При подаче с;!гнала на второй вход схемы и при превышении этим сигналом порогового уровня транзистор 2 насыщается и шунтирует выход схемы. При этом независимо от вегсичи239385

Предмет изобретения

Соса авитсль В. Ефремова

Техред A. А. Камышникова Корректор Н. В. Дятлова

Редактор С. Н. Хейфиц

1И .заказ 16/о/11 Тираж 480 Подписное

ИИПИ Комитета по делам изобретений и огкрытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2 ны сигнала на первом входе напряжение на выходе схемы будет равно пороговому. 1 аким образом, выходное напряжение схемы равно пороговому, копда величина сигнала по первому входу меньше 1порогового напряжения, либо величина сигнала по второму входу больше порогового напряжения, либо в том и другом случае. В остальные моменты выходное напряжение равно напряженшо источника коллекторного питания.

При подаче сигнала на оба входа на выходе устройства формируется прямоугольный им пульс, длителы1ость которого пропорциональна фазсвому сдвигу.

Преобразователь сдвш1а фазы во временной интервал, содержащий амплитудные диокриминаторы на двух транзисторах, отличаюи ийоя тем, что, с целью получения линейной характеристики преобразования, расширения диапазона преобразования,,на выходе схемы включен дополнительный транзистор, эмиттер

10 которого соединен с эмиттерами двух упомянутых транзисторов, а коллектор соединен с коллектором выходного транзистора, причем между эмпттерамп упомянутых транзисторов и потенциальной шиной источника питания

15 включен стабилитрон.