Компенсационный стабилизатор напряжения

Иллюстрации

Показать всеУстройство относится к области электротехники и может быть использовано в качестве стабилизатора напряжения постоянного тока. Для достижения технического результата - снижения коэффициента нестабильности по току нагрузки - устройство содержит первый и второй резисторы, подключенные первыми выводами к шине питания, третий резистор, подключенный первым выводом к общей шине, первый транзистор, подключенный истоком ко второму выводу первого резистора, а затвором - ко второму выводу второго резистора, второй транзистор, подключенный эмиттером к общей шине, а базой - ко второму выводу третьего резистора, третий транзистор, подключенный коллектором к затвору первого транзистора, а базой - к стоку первого транзистора и коллектору второго транзистора, четвертый транзистор, подключенный коллектором к шине питания, эмиттером - к выходной клемме, а базой - к эмиттеру третьего транзистора, стабилитрон, подключенный катодом к выходной клемме, а анодом - к базе второго транзистора. 5 ил.

Реферат

Устройство относится к области электротехники и может быть использовано в качестве стабилизатора напряжения постоянного тока.

Известны компенсационные стабилизаторы напряжения (CH), отличающиеся простотой, но не обладающие высоким коэффициентом стабилизации [Пат. №2313819 РФ. Стабилизатор постоянного напряжения / А.А.Мануйлов, И.А.Семенов - Опубл. 27.12.2007, Бюл. №36.].

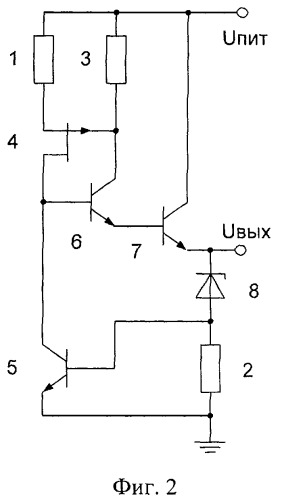

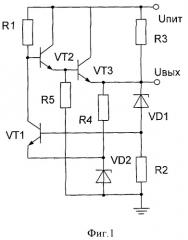

Наиболее близким техническим решением, принятым за прототип, является СН, приведенный на фиг.1 [Горошков Б.И. Радиоэлектронные устройства: Справочник. - М.: Радио и связь, 1984. - (Массовая радиобиблиотека; Вып.1076), рис.16.22.].

Недостатком прототипа является недостаточно высокий коэффициент стабилизации по току нагрузки. Это объясняется не только конечным петлевым усилением и ненулевым выходным сопротивлением, но и изменением режима работы источника опорного напряжения при изменении тока нагрузки.

Для снижения коэффициента нестабильности по току нагрузки в схему прототипа, содержащую первый резистор, подключенный одним выводом к шине питания, второй резистор, подключенный одним выводом к общей шине, третий резистор, подключенный одним выводом к шине питания, первый транзистор, подключенный эмиттером к общей шине, а базой - ко второму выводу второго резистора, второй транзистор, подключенный базой к коллектору первого транзистора, третий транзистор, подключенный коллектором к шине питания, эмиттером - к выходной клемме, а базой - к эмиттеру второго транзистора, стабилитрон, подключенный катодом к выходной клемме, а анодом - к базе первого транзистора, введен полевой транзистор, подключенный истоком ко второму выводу первого резистора, стоком - к коллектору первого транзистора, а затвором - к соединению второго вывода третьего резистора с коллектором второго транзистора.

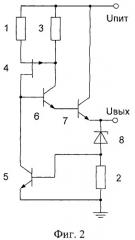

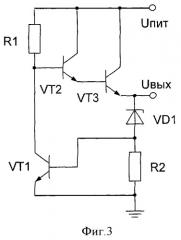

Схема прототипа приведена на фиг.1, заявляемого устройства - на фиг.2, а упрощенная схема прототипа - на фиг.3.

Заявляемый СН (фиг.2) содержит первый резистор 1, подключенный первым выводом к шине питания, второй резистор 2, подключенный первым выводом к общей шине, третий резистор 3, подключенный первым выводом к шине питания, первый транзистор 4, подключенный истоком ко второму выводу резистора 1, а затвором - ко второму выводу резистора 3, второй транзистор 5, подключенный эмиттером к общей шине, а базой - ко второму выводу резистора 2, третий транзистор 6, подключенный коллектором к затвору транзистора 4, а базой - к стоку транзистора 4 и коллектору транзистора 5, четвертый транзистор 7, подключенный коллектором к шине питания, эмиттером - к выходной клемме, а базой - к эмиттеру транзистора 6, стабилитрон 8, подключенный катодом к выходной клемме, а анодом - к базе транзистора 5.

Прежде чем рассмотреть работу заявляемого устройства, рассмотрим работу упрощенной схемы прототипа (фиг.3), так как это необходимо для сопоставительного анализа. Выходное напряжение такого стабилизатора определяется суммой напряжений база-эмиттер транзистора VT1 Uбэ и стабилитрона VD1 Uст. Следовательно, приращение выходного напряжения dUвых, возникающее при воздействии дестабилизирующих факторов, определяется выражением

где dUст и Uбэ - приращения напряжений стабилитрона VD1 и база-эмиттер транзистора VT1 соответственно.

Приращения напряжений dUст и dUбэ можно выразить через соответствующие приращения токов стабилитрона и эмиттера транзистора VT1

где rст и dIст - соответственно, дифференциальное сопротивление и приращение тока стабилитрона VD1; rэ и dIэ - соответственно, дифференциальное сопротивление и приращение тока эмиттера транзистора VT1.

Ток стабилитрона Iст равен сумме тока резистора R2 и тока базы транзистора VT1. Следовательно, приращение dIст определится выражением

где dIR2 и dIб2 - приращения тока резистора R2 и базы транзистора VT2 соответственно; R2 - сопротивление резистора R2; β1 - коэффициент передачи по току транзистора VT1 в схеме с общим эмиттером.

Ток эмиттера выходного транзистора VT3 равен сумме тока нагрузки и Iст. Следовательно, справедливо выражение

где dIэ3 и dIн - приращения эмиттера транзистора VT3 и тока нагрузки соответственно.

Приращение тока dIэ3 можно выразить через dIэ, пренебрегая изменением тока резистора R1, (резистор R1 выполняет роль источника тока)

где β2 и β3 - соответственно коэффициенты передачи по току транзисторов VT2 и VT3 в схеме с общим эмиттером, а член - (β2+1) выражает коэффициент преобразования тока коллектора транзистора VT2 в ток эмиттера транзистора VT2.

Из выражений (3)-(5) получаем

Из выражений (2) и (3) получим

откуда, с учетом (6), находим

Полученное выражение (8) определяет нестабильность выходного напряжения прототипа по току нагрузки. Знак минус говорит о том, что с ростом тока нагрузки выходное напряжение уменьшается. Принимая практически справедливые допущения, что rэ<<R2, rст<<R2, а β1≈β2≈β3≈β>>1, получим

Теперь аналогичным образом рассмотрим работу устройства (фиг.2). Принципиальное отличие работы заявляемого устройства от прототипа состоит в том, что введен транзистор 4, выполняющий роль источника тока, причем ток стока транзистора 4 зависит от тока нагрузки. В идеале при изменении тока нагрузки соответствующее изменение тока базы транзистора 6 компенсируется приращением тока стока транзистора 4, а не приращением тока коллектора (и, разумеется, эмиттера) транзистора 5. Следовательно, приращения опорного напряжения база-эмиттер транзистора 5 и результирующего выходного напряжения в таком случае не возникает.

Можно показать, что выражение, аналогичное (8), для заявляемого устройства запишется в следующем виде:

где r5 и r8 - дифференциальные сопротивления эмиттера транзистора 5 и стабилитрона 8 соответственно; R2 - сопротивление резистора 2; β5 и β7 - коэффициенты передачи по току в схеме с общим эмиттером транзисторов 5 и 7 соответственно; K6=-dI6/dI5 - коэффициент преобразования тока коллектора транзистора 5 в ток эмиттера транзистора 6; dI5 и dI6, - приращения тока коллектора транзистора 5 и тока эмиттера транзистора 6 соответственно.

Для определения K6 учтем следующее:

где dI4 - приращение тока стока транзистора 4; β6 -коэффициент передачи по току в схеме с общим эмиттером транзистора 6.

где dU1 и dU3 - приращение напряжения на резисторах 1 и 3 соответственно; dU4 - приращение напряжения затвор-исток транзистора 4.

Уравнение (12) запишем через приращения токов

где R1 и R3 - сопротивление резисторов 1 и 3 соответственно; S - крутизна (передаточная проводимость) транзистора 4.

Из (11) и (13) можно выразить

Отсюда можно вывести условие настройки, при котором K6 обращается в бесконечность, а нестабильность (10) - в ноль

На практике для снижения режимной зависимости условия (15) следует применять транзистор 4 с максимальной крутизной, а транзистор 6 - минимальной режимной зависимостью β6. Допуская, что r5<<R2, r8<<R2, а β5≈β7≈β>>1, из (10) получим

Заметим, что при R3=0 выражение (10) совпадает с (8), а (16) - с (9). При выполнении неравенства получаем K6>β6+1.

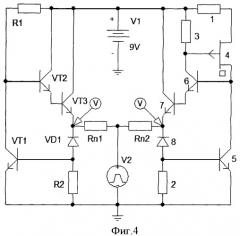

На фиг.4 приведена схема, а на фиг.5 - соответствующие результаты схемотехнического моделирования. В моделируемой схеме к одному источнику питания для удобства сравнения подключены и прототип (левая часть фиг.4) и заявляемый СН (правая часть фиг.4), нагруженные резисторами Rn1 и Rn2, соответственно, которые подключены к управляемому источнику напряжения V2. На фиг.5 представлены графики, показывающие изменение выходного напряжения прототипа (линия со знаками □) и заявляемого СН (линия со знаками ◇) при изменении тока нагрузки Rn2 (горизонтальная ось). Из результатов моделирования можно сделать следующий вывод: при практически одинаковых выходных напряжениях и изменениях тока нагрузки абсолютное изменение выходного напряжения заявляемого СН (0,3 мВ) оказывается существенно меньше, чем в схеме прототипа (3,1 мВ).

Таким образом, и проведенный анализ и данные схемотехнического моделирования подтверждают, что достигается заявляемый технический результат - снижение коэффициента нестабильности по току нагрузки.

Компенсационный стабилизатор напряжения, содержащий первый резистор, подключенный одним выводом к шине питания, второй резистор, подключенный одним выводом к общей шине, третий резистор, подключенный одним выводом к шине питания, первый транзистор, подключенный эмиттером к общей шине, а базой - ко второму выводу второго резистора, второй транзистор, подключенный базой к коллектору первого транзистора, третий транзистор, подключенный коллектором к шине питания, эмиттером - к выходной клемме, а базой - к эмиттеру второго транзистора, стабилитрон, подключенный катодом к выходной клемме, а анодом - к базе первого транзистора, отличающийся тем, что введен полевой транзистор, подключенный истоком ко второму выводу первого резистора, стоком - к коллектору первого транзистора, а затвором - к соединению второго вывода третьего резистора с коллектором второго транзистора.