Синтезатор частот

Иллюстрации

Показать всеИзобретение относится к радиотехнике и может использоваться в качестве возбудителя передатчика и гетеродина приемника без подачи модулирующего сигнала. Техническим результатом является значительное повышение быстродействия при переключении частот одновременно с высокой чистотой спектра выходного сигнала. Синтезатор частот содержит два частотно-фазовых детектора, два фильтра нижних частот, генератор, управляемый напряжением, два делителя с переменным коэффициентом деления, буферный каскад, два индикатора синхронизма, схему совпадения, D-триггер, формирователь регулирующего сигнала и усилитель с регулируемым коэффициентом усиления, двухрежимный автогенератор, блок управления, ключ, переключатель с двух направлений, запоминающий блок и источник сигнала эталонной частоты. 3 ил.

Реферат

Предлагаемое изобретение относится к радиотехнике и может использоваться в качестве малошумящего быстро переключаемого по частоте гетеродина приемника и в других устройствах, где требуется быстрая перестройка по частоте при высокой чистоте спектра выходного сигнала.

Известен цифровой синтезатор частот (ЦСЧ), построенный на основе системы импульсно-фазовой автоподстройки (ИФАПЧ) с делителем частоты с переменным коэффициентом деления (ДПКД) в цепи обратной связи (см. Шапиро Д.Н., Паин А.А. Основы теории синтеза частот. - М.: Радио и связь. 1981., стр.39, рис.1.7, а также Левин В. А. и др. Синтезаторы частот с системой импульсно-фазовой автоподстройки. - М.: Радио и связь. 1989, стр.9, рис.1.1.).

Достоинством такого ЦСЧ с применением современных микросхем является возможность формирования на выходе его большого числа дискретных частот со стабильностью, равной стабильности одного опорного кварцевого генератора (ОКГ) при малых габаритах и малой потребляемой мощности постоянного тока.

Недостаток этого однокольцевого ЦСЧ состоит в том, что невозможно получить одновременно высокую чистоту спектра выходного высокочастотного (ВЧ) сигнала при перестройке в широком диапазоне частот с малым шагом сетки частот и высокое быстродействие при переключении с одной частоты на другую.

Известно, что система ИФАПЧ ЦСЧ представляет собой фильтр нижних частот по отношению к шумам колебания опорной частоты и фильтр верхних частот по отношению к шумам генератора, управляемого напряжением (ГУН). Поэтому, если необходимо подавить шумы колебания опорной частоты до требуемых значении, надо использовать узкополосную петлю ИФАПЧ. В этом случае не будут выполняться требования по быстродействию и не компенсируются собственные шумы ГУН, для чего нужна широкополосная петля ИФАПЧ. С другой стороны, если спроектировать кольцо ИФАПЧ со сравнительно широкой полосой частот, что и требуется для быстродействующего синтезатора, тогда шумы опорного генератора после повышения частоты путем умножения пропорционально коэффициенту N до выходной частоты будут определять основные шумы на выходе синтезатора.

Это основное противоречие однокольцевого ЦСЧ, которое не позволяет выполнить высокие современные требования к быстродействующему высокочастотному и малошумящему синтезатору частот.

Известен двухкольцевой ЦСЧ с частотной модуляцией (ЧМ) с последовательным включением колец ИФАПЧ, в котором функции частотообразования разделены между первым и вторым кольцами, что уменьшает отмеченные выше противоречия (см. патент на ПМ №63996 от 29 декабря 2006 г.). В этом ЦСЧ первое кольцо узкополосное и является опорным для второго широкополосного выходного кольца. Во втором кольце с использованием делителя частоты с дробным переменным коэффициентом деления (ДДПКД) вместо целочисленного ДПКД можно получить высокое быстродействие, которое в настоящее время необходимо в системах связи на основе быстрого переключения частот по заданной программе. Однако в этом синтезаторе даже с использованием современных микросхем ЦСЧ с ΣΔ-модуляторами (см., например, микросхему ADF4252 фирмы Analog Devices) есть так называемые «помехи дробности», которые на 10-20 дБ ухудшают спектральную чистоту ГУН по сравнению с ЦСЧ на основе целочисленного ДПКД, что проверено экспериментально.

Наиболее близким по технической сущности к предложенному является синтезатор частот (см. патент на изобретение RU №2329594 C1 H03L 7/18 от 20. 07. 2008 г. Бюл. №20), который принят за прототип.

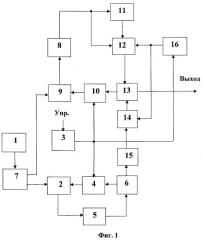

Блок-схема устройства-прототипа приведена на фиг.1, где введены следующие обозначения:

1 - источник сигнала эталонной частоты (ИСЭЧ);

2 и 9 - первый и второй частотно-фазовые детекторы (ЧФД);

3 - блок управления (БУ);

4 и 10 - первый и второй делители частоты с переменным коэффициентом деления (ДПКД);

5 и 8 - первый и второй фильтры нижних частот (ФНЧ);

6 - генератор, управляемый напряжением (ГУН);

7 - буферный каскад (БК);

11 - запоминающий блок (ЗБ);

12 - переключатель с двух направлений (ПД);

13 - двухрежимный автогенератор (ДА);

14 - ключ (КЛ);

15 - делитель напряжения (ДН);

16 - блок временных интервалов (БВИ).

Устройство-прототип содержит последовательно соединенные источник сигнала эталонной частоты ИСЭЧ 1 и буферный каскад БК 7, первый выход которого соединен с первым входом первого ЧФД 2, выход которого через первый ФНЧ 5 соединен с управляющим входом ГУН 6, первый выход которого через первый ДПКД 4 соединен со вторым входом первого ЧФД 2.

Таким образом, на основе ГУН 6 образовано первое кольцо ИФАПЧ.

Второй выход БК 7 соединен с первым входом второго ЧФД 9, выход которого через второй ФНЧ 8 соединен со входом ЗБ 11 и первым входом ПД 12, второй вход которого соединен с выходом ЗБ 11, а выход ПД 12 соединен с управляющим входом ДА 13, первый выход которого через второй ДПКД 10 соединен со вторым входом второго ЧФД 9.

Следовательно, второе кольцо ИФАПЧ на основе двухрежимного автогенератора ДА 13 включено параллельно первому кольцу.

Второй выход ГУН 6 через последовательно соединенные ДН 15 и КЛ 14 соединен с ВЧ входом ДА 13, второй выход которого является выходом устройства. Управляющим входом устройства-прототипа является вход БУ 3, выход которого соединен с управляющими входами первого ДПКД 4, второго ДПКД 10 и входом БВИ 16, выход которого соединен с управляющими входами ПД 12 и КЛ 14.

Устройство-прототип работает следующим образом.

Управляющая команда на включение поступает на вход БУ 3, выходной сигнал которого является командой на установление задаваемого (одинакового, например, равного N) коэффициента деления для первого ДПКД 4 и второго ДПКД 10. Сигнал с первого выхода ГУН 6 через первый ДПКД 4 и сигнал с первого выхода ДА 13 через второй ДПКД 10 подаются соответственно на вторые входы первого ЧФД 2 и второго ЧФД 9, на первые входы которых подается сигнал от ИСЭЧ 1 после разделения в БК 7 с первого и второго его выходов соответственно.

Кроме того, управляющая команда на включение через БУ 3 подается на БВИ 16, который формирует сигнал длительностью Т3 для управления ПД 12 и КЛ 14. По этой команде ПД 12 соединяет выход второго ФНЧ 8 с управляющим входом ДА 13 на время Т3 и на это же время размыкает КЛ 14. При этом выходное напряжение с первого ЧФД 2 через первый ФНЧ 5 подается на управляющий вход ГУН 6 и через определенный отрезок времени Т3 обеспечивается вхождение в синхронизм в первом кольце ИФАПЧ на основе ГУН 6, на выходе которого формируется заданная частота.

В то же время выходное напряжение со второго ЧФД 9 через второй ФНЧ 8 и ПД 12, замкнутый по команде с БВИ 16, подается на управляющий вход ДА 13. Напряжение на управляющем входе ДА 13 через определенный отрезок времени Т3 обеспечивает получение на выходах ДА 13 частоты, точно равной эталонной частоте, умноженной на N - коэффициент деления второго ДПКД 10. Таким образом, одновременно с первым работает второе, дополнительное кольцо ИФАПЧ, и в обоих кольцах на выходе формируются одинаковые частоты. В то же время управляющее напряжение с выхода второго ФНЧ 8 запоминается в ЗБ 11.

По истечении отрезка времени Т3 команда с выхода БВИ 16 меняется и ключ КЛ 14 замыкается, а ПД 12 отключает управляющий вход ДА 13 от второго ФНЧ 8 и подключает его вход к выходу ЗБ 11. Следовательно, второе кольцо ИФАПЧ перестает работать и ДА 13 переходит в режим автоколебаний по частоте, близкой к той, которая установилась перед отключением. Одновременно на ВЧ вход ДА 13 через замкнутый КЛ 14 и ДН 15 подается напряжение со второго выхода ГУН 6 и происходит захват частоты колебаний ДА 13 колебаниями ГУН 6.

Следовательно, выходное напряжение ДА 13 будет иметь частоту, равную синтезированной в ГУН 6, который охвачен кольцом ИФАПЧ, а шумы -соответствующие шумам генератора ДА 13, который работает в режиме автоколебаний. Эти шумы автогенератора без кольца ИФАПЧ значительно ниже, чем у синтезаторов с кольцом ИФАПЧ на основе целочисленного ДПКД (примерно на 20-30 дБ согласно данным, приведенным в описании синтезатора-прототипа на стр.2).

Таким образом, на выходе устройства-прототипа формируется ВЧ сигнал с высокой чистотой спектра и малыми шумами со стабильностью, точно равной стабильности ГУН, охваченного кольцом ИФАПЧ.

Недостаток рассмотренного синтезатора-прототипа состоит в малом быстродействии.

Работа известного устройства при переключении частот происходит в два этапа. На первом этапе ГУН 6 и ДА 13 работают, как обычно, в системе ИФАПЧ и генерируют на своих выходах одну и ту же заданную частоту. Причем фактически время установления синхронизма в обоих кольцах ИФАПЧ существенно меньше, чем заданный интервал времени Т3, который определяется от БВИ 16 (естественно, всегда с некоторым запасом). Иначе говоря, уже на первом этапе происходит ухудшение быстродействия из-за ожидания окончания интервала времени Т3 после установления синхронизма в системе ИФАПЧ.

На втором этапе ГУН 6 продолжает работать в режиме ИФАПЧ, а ДА 13 работает как автогенератор в режиме захвата частоты. При этом ВЧ напряжение (внешнее возбуждение Еос по отношению к ДА 13) со второго выхода ГУН 6 через делитель напряжения ДН 15 и замкнутый КЛ 14 подается в колебательную цепь ДА 13. При этом "шум" в составе напряжения внешнего возбуждения Еос (от ГУН 6) будет фильтроваться контуром автогенератора ДА 13. Чтобы этот "шум" в стационарном режиме был минимальный, предусмотрен делитель ДН 15 этого внешнего ВЧ напряжения возбуждения Еос от ГУН 6. Уровень внешнего ВЧ напряжения возбуждения Еос устанавливается от ГУН 6 с помощью делителя напряжения ДН 15 чуть больше минимально необходимого для осуществления захвата частоты в ДА 13 колебаниями на выходе ГУН 6. Но известно, что длительность процесса установления (захвата) частоты в автогенераторе возрастает с уменьшением значения напряжения внешнего возбуждения Еос (см. материалы по описанию устройства-прототипа стр.6).

Следовательно, установление минимальной величины напряжения внешнего возбуждения Еос в синтезаторе-прототипе приводит к существенному увеличению длительности процесса установления (захвата) частоты автогенератора на втором этапе, т.е. к ухудшению быстродействия.

Таким образом, быстродействие синтезатора-прототипа недостаточно как на первом этапе работы при переключении частот, так и на втором этапе при захвате частоты ДА 13 от частоты ГУН 6.

Для устранения указанного недостатка в синтезатор частот, содержащий последовательно соединенные источник сигнала эталонной частоты и буферный каскад, первый выход которого соединен с первым входом первого частотно-фазового детектора, выход которого через первый фильтр нижних частот соединен с управляющим входом генератора, управляемого напряжением, первый выход которого через первый делитель частоты с переменным коэффициентом деления соединен со вторым входом первого частотно-фазового детектора; второй выход буферного каскада соединен с первым входом второго частотно-фазового детектора, выход которого через второй фильтр нижних частот соединен со входом запоминающего блока и первым входом переключателя с двух направлений, второй вход которого соединен с выходом запоминающего блока, а выход переключателя с двух направлений соединен с управляющим входом двухрежимного автогенератора, первый выход которого через второй делитель частоты с переменным коэффициентом деления соединен со вторым входом второго частотно-фазового детектора; при этом второй выход двухрежимного автогенератора является выходом устройства, а также ключ, выход которого соединен с высокочастотным входом двухрежимного автогенератора, и блок управления, вход которого является входом устройства, при этом выход блока управления соединен с управляющими входами первого и второго делителей частоты с переменным коэффициентом деления, введены первый и второй индикаторы синхронизма, логическая схема совпадения, Д-триггер, формирователь регулирующего сигнала и усилитель с регулируемым коэффициентом усиления, причем входы первого и второго индикаторов синхронизма соединены соответственно с выходами первого и второго частотно-фазовых детекторов, а выходы первого и второго индикаторов синхронизма соединены соответственно с первым и вторым входами логической схемы совпадения, выход которой через Д-триггер и формирователь регулирующего сигнала соединен с управляющим входом усилителя с регулируемым коэффициентом усиления, вход которого соединен со вторым выходом генератора, управляемого напряжением, а выход - с входом ключа, управляющий вход которого соединен с выходом Д-триггера и управляющим входом переключателя с двух направлений, при этом выход блока управления соединен также со входом сброса Д-триггера.

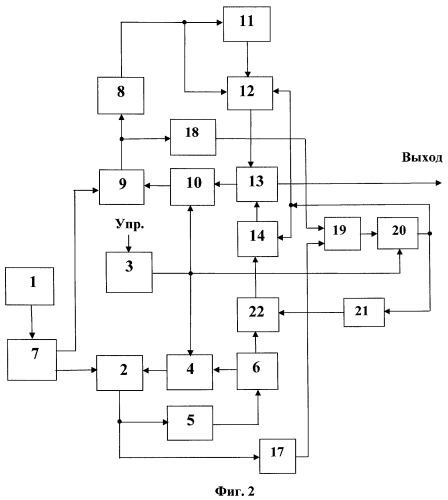

Блок-схема предложенного устройства приведена на фиг.2, где введены следующие обозначения:

1 - источник сигнала эталонной частоты (ИСЭЧ);

2 и 9 - первый и второй частотно-фазовые детекторы (ЧФД);

3 - блок управления (БУ);

4 и 10 - первый и второй делители частоты с переменным коэффициентом деления (ДПКД);

5 и 8 - первый и второй фильтры нижних частот (ФНЧ);

6 - генератор, управляемый напряжением (ГУН);

7 - буферный каскад (БК);

11 - запоминающий блок (ЗБ);

12 - переключатель с двух направлений (ПД);

13 - двухрежимный автогенератор (ДА);

14 - ключ (КЛ);

17 и 18 - первый и второй индикаторы синхронизма (ИС);

19 - логическая схема совпадения (СС);

20 - Д-триггер (ДТ);

21 - формирователь регулирующего сигнала (ФРС);

22 - усилитель с регулируемым коэффициентом усиления (РУ).

Предлагаемое устройство содержит последовательно соединенные источник сигнала эталонной частоты ИСЭЧ 1 и буферный каскад БК 7, первый выход которого соединен с первым входом первого ЧФД 2, выход которого через первый ФНЧ 5 соединен с управляющим входом ГУН 6, первый выход которого через первый ДПКД 4 соединен со вторым входом первого ЧФД 2, выход которого, кроме того, соединен со входом первого индикатора синхронизма ИС 17, выход которого соединен с первым входом логической схемы совпадения СС 19. На основе ГУН 6 сформировано первое кольцо ИФАПЧ.

Второй выход БК 7 соединен с первым входом второго ЧФД 9, выход которого через второй ФНЧ 8 соединен с входом ЗБ 11 и первым входом ПД 12, второй вход которого соединен с выходом ЗБ 11. При этом выход ПД 12 соединен с управляющим входом ДА 13, первый выход которого через второй ДПКД 10 соединен со вторым входом второго ЧФД 9, выход которого, кроме того, соединен со входом второго индикатора синхронизма ИС 18, выход которого соединен со вторым входом логической схемы совпадения СС 19. На основе двухрежимного автогенератора ДА 13 образовано второе кольцо ИФАПЧ.

Второй выход ГУН 6 через последовательно соединенные усилитель с регулируемым коэффициентом усиления РУ 22 и КЛ 14 соединен с ВЧ входом ДА 13, второй выход которого является выходом устройства. Управляющим входом предлагаемого устройства является вход БУ 3, выход которого соединен с управляющими входами первого ДПКД 4, второго ДПКД 10 и входом сброса Д-триггера ДТ 20. Выход ДТ 20 соединен с управляющими входами КЛ 14 и ПД 12, а через ФРС 21 соединен с управляющим входом РУ 22.

Усилитель с переменным коэффициентом усиления РУ 22 имеет регулируемую эмиттерную отрицательную обратную связь. Причем регулирующий сигнал на его управляющем входе, который образуется на выходе ФРС 21, предназначен для экспоненциального изменения коэффициента усиления входного сигнала.

Предлагаемое устройство работает следующим образом.

Управляющая команда на включение заданной частоты СЧ поступает от БУ 3 на управляющие входы первого ДПКД 4 и второго ДПКД 10, устанавливая в них одинаковые коэффициенты деления N, а также на вход сброса ДТ 20, устанавливая на его выходе команду с уровнем Лог.0. По этой команде ПД 12 соединяет выход второго ФНЧ 8 с управляющим входом ДА 13, а ключ КЛ 14 размыкает выход усилителя РУ 22 с ВЧ входом ДА 13. При этом выходное напряжение с первого ЧФД 2 через первый ФНЧ 5 подается на управляющий вход ГУН 6. В результате происходит процесс вхождения в синхронизм в первом кольце и на выходе первого ИС 17, включенного после первого ЧФД 2, формируется уровень Лог.1, который поступает на первый вход СС 19. В то же время выходное напряжение со второго ЧФД 9 через второй ФНЧ 8 и ПД 12, замкнутый по команде с ДТ 20, подается на управляющий вход ДА 13. В результате происходит процесс вхождения в синхронизм во втором кольце ИФАПЧ и на выходе второго ИС 18, включенного после второго ЧФД 9, формируется уровень Лог.1, который поступает на второй вход СС 19. Одновременно управляющее напряжение с выхода второго ФНЧ 8 запоминается в ЗБ 11.

Как только на первый и второй входы СС 19 поступают одинаковые уровни Лог.1, на выходе СС 19 формируется уровень Лог.1, который приходит на Д-вход Д-триггера ДТ 20, устанавливая на его выходе сигнал с уровнем Лог.1.

По этому сигналу ПД 12 размыкает выход второго ФНЧ 8 с управляющим входом ДА 13 (т.е. второе кольцо ИФАПЧ размыкается), а ключ КЛ 14 соединяет выход усилителя РУ 22 с ВЧ входом ДА 13. Одновременно управляющее напряжение с выхода ЗБ 11 через ПД 12 поступает на управляющий вход ДА 13. Кроме того, уровень Лог.1 поступает с выхода ДТ 20 на вход формирователя регулирующего сигнала ФРС 21, на выходе которого формируется сигнал, предназначенный для экспоненциального изменения коэффициента усиления усилителя с регулируемым коэффициентом усиления РУ 22 (см. временные диаграммы процесса формирования сигнала для экспоненциального изменения коэффициента усиления РУ 22 на фиг.3а, б, в).

Усилитель с регулируемым коэффициентом усиления имеет в эмиттерной цепи переменный резистор, величина которого может изменяться от внешнего управляющего напряжения. С помощью переменного резистора, включенного в эмиттерную цепь усилителя РУ 22, осуществляется отрицательная обратная связь. От величины этого переменного резистора зависит коэффициент усиления РУ 22. В качестве переменного резистора используется полевой транзистор. Когда напряжение управления на затворе полевого транзистора увеличивается, величина переменного резистора уменьшается, а значит, уменьшается отрицательная обратная связь и усиление РУ 22 увеличивается. Таким образом, увеличивается ВЧ напряжение внешнего возбуждения Еос на ВЧ входе ДА 13. И наоборот, когда напряжение управления уменьшается, соответственно уменьшается усиление РУ 22 и уровень внешнего возбуждения Еос.

Перепад напряжения с Лог.0 на Лог.1 (т.е. короткий фронт импульса) с выхода ДТ 20 (см. фиг.3а) поступает на вход ФРС 21, на выходе которого формируется «скачок» управляющего напряжения (фиг.3б), превышающий значительно уровень минимальной величины, необходимой для получения на выходе РУ 22 напряжения внешнего возбуждения Еос в стационарном (установившемся) режиме. Этот «скачок» с минимальной длительностью в начале затем по экспоненте затухает до установившегося минимального значения, которое достаточно для сохранения процесса захвата частоты в ДА 13 и которое обеспечивает минимальный уровень «шума». Иначе говоря, короткий фронт импульса с выхода ДТ 20 вызывает экспоненциальный процесс в ФРС 21, а длительность этого процесса будет зависеть от величины его входной емкости. Этот «скачок» управляющего напряжения существенно сокращает время захвата частоты ДА 13 от колебаний ГУН 6, т.е. захват частоты в ДА 13 происходит с более высоким быстродействием, чем в СЧ - прототипе.

Достоинство предложенного технического решения в том, что с помощью введенных новых элементов, объединенных соответствующими связями с остальными узлами схемы, осуществляется возможность значительного повышения быстродействия синтезатора как на первом этапе в режиме вхождения в синхронизм, так и на втором этапе в режиме захвата частоты ДА 13 от внешнего возбуждения и одновременного получения высокой чистоты спектра выходного сигнала.

Доказательством возможности осуществления предлагаемого устройства является то, что вводимые блоки типовые и могут быть выполнены на широко известных микросхемах. Цифровая часть синтезаторов выполняется на микросхемах ЦСЧ с ИФАПЧ разных фирм. При этом в одной микросхеме могут быть один или два независимых ЦСЧ с целочисленным ДПКД (Integer-N) или с дробным (Fractional-N). Например, микросхемы LMX2364, LMX2470 фирмы National Semiconductor, микросхемы ADF4252 фирмы Analog Devices представляют собой двойной синтезатор с двумя раздельными контурами регулирования: один с дробным ДПКД (ДДПКД), другой с целочисленным ДПКД. Микросхема ADF4001 фирмы Analog Devices имеет только один целочисленный ДПКД, прецизионный ЧФД и ультранизкий фазовый шум. Индикаторы синхронизма обычно входят в состав этих микросхем на выходе ЧФД и бывают двух типов: цифровой и аналоговый. Цифровой ИС работает так, что если в трех (или пяти) последовательных циклах измерения фазовое рассогласование между импульсами двух потоков импульсов на входах ЧФД меньше 15 нсек, то имеется синхронизм в кольце ИФАПЧ и на выходе цифрового ИС формируется уровень Лог.1. Если фазовая ошибка больше 25 нсек в одном цикле измерения, то синхронизма нет и на выходе цифрового ИС формируется уровень Лог.0. Логическая схема совпадения на два входа может быть выполнена на микросхеме 564 ЛА7, Д-триггер - на микросхеме 564 ТМ2, формирователь регулирующего сигнала - на операционном усилителе AD822AR фирмы Analog Devices, усилитель с регулируемым коэффициентом усиления РУ 22 на основе транзистора типа BFR 93A фирмы Philips. В качестве управляемого сопротивления в эмиттерной цепи транзистора BFR 93A используется полевой транзистор, на основе которого образуется регулируемая эмиттерная отрицательная обратная связь. При изменении величины сопротивления в эмиттерной цепи усилителя РУ 22 изменяется его коэффициент усиления.

Таким образом, в предложенном синтезаторе частот решена противоречивая проблема одновременного получения высокой чистоты спектра выходного сигнала и высокого быстродействия при переключении частот.

Это позволяет использовать предложенный синтезатор частот в современных системах радиосвязи с быстрым перескоком частоты по заданной программе.

Синтезатор частот, содержащий последовательно соединенные источник сигнала эталонной частоты и буферный каскад, первый выход которого соединен с первым входом первого частотно-фазового детектора, выход которого через первый фильтр нижних частот соединен с управляющим входом генератора, управляемого напряжением, первый выход которого через первый делитель частоты с переменным коэффициентом деления соединен со вторым входом первого частотно-фазового детектора, второй выход буферного каскада соединен с первым входом второго частотно-фазового детектора, выход которого через второй фильтр нижних частот соединен со входом запоминающего блока и первым входом переключателя с двух направлений, второй вход которого соединен с выходом запоминающего блока, а выход переключателя с двух направлений соединен с управляющим входом двухрежимного автогенератора, первый выход которого через второй делитель частоты с переменным коэффициентом деления соединен со вторым входом второго частотно-фазового детектора, при этом второй выход двухрежимного автогенератора является выходом устройства, а также ключ, выход которого соединен с высокочастотным входом двухрежимного автогенератора, и блок управления, вход которого является входом устройства, при этом выход блока управления соединен с управляющими входами первого и второго делителей частоты с переменным коэффициентом деления, отличающийся тем, что введены первый и второй индикаторы синхронизма, схема совпадения, Д-триггер, формирователь регулирующего сигнала и усилитель с регулируемым коэффициентом усиления, причем входы первого и второго индикаторов синхронизма соединены соответственно с выходами первого и второго частотно-фазовых детекторов, а выходы первого и второго индикаторов синхронизма соединены соответственно с первым и вторым входами схемы совпадения, выход которой через Д-триггер и формирователь регулирующего сигнала соединен с управляющим входом усилителя с регулируемым коэффициентом усиления, вход которого соединен со вторым выходом генератора, управляемого напряжением, а выход - с входом ключа, управляющий вход которого соединен с выходом Д-триггера и управляющим входом переключателя с двух направлений, при этом выход блока управления соединен также со входом сброса Д-триггера.