Способ демодуляции сигнала в манчестерском коде

Иллюстрации

Показать всеИзобретение относится к области передачи информации по проводным линиям и предназначено для использования в системах сбора и обработки информации охранных систем с их высокими требованиями к надежности каналов связи. Технический результат - исключении помех в сигнале на выходе интегратора в момент начала очередного информационного интервала и помех внутри устройства при отсутствии информационного сигнала. Способ демодуляции сигнала в манчестерском коде заключается в том, что информационный сигнал интегрируют и формируют четыре последовательности импульсов. В моменты появления импульсов третьей и четвертой последовательностей формируют уровни выходного бинарного сигнала, а затем формируют импульсы, обеспечивающие обнуление интегратора. 4 з.п. ф-лы, 2 ил.

Реферат

Изобретение относится к области передачи информации по проводным линиям и предназначено преимущественно для использования в системах сбора и обработки информации охранных систем с их высокими требованиями к надежности каналов связи. В принципе, возможно использование изобретения в любых системах связи.

Предшествующий уровень техники

Код Манчестер представляет собой код, формирующий в центре разрядного интервала логическую «1» при переходе информационного сигнала с высокого уровня на низкий и логический «0» - при переходе с низкого уровня на высокий. Манчестерский код отличается высоким быстродействием, не требует специальных синхронизирующих слов, и в нем концептуально заложена значительно более высокая помехоустойчивость по сравнению с другими видами кодов. Он нашел очень широкое применение в технике связи. Несмотря на это предлагаются все новые и новые технические решения, усовершенствующие способ демодуляции манчестерского кода (см., например, патент США № 6370242 "Method and device for decoding Manchester encoded data", inventor: Junji Nacai, Assignee: Old Electric Industry Co. Ltd. (JP), Priority data: May 20 1998, патент США № 6008746 "Method and device for decoding noisy, intermittent data, such as Manchester encoded data or the like", inventor: William A. White, Assignee: Texas Instrument Incorporated (US), Priority data: Nov. 13 1996, патент США № 5892797 "System and method for recovering data using Manchester code and other bi-phase level codes", inventor: Jay Jie Deng (US), Priority data: Jul. 15, 1997).

Весьма перспективным представляется способ демодуляции сигнала в манчестерском коде, основанный на том, что биполярный информационный сигнал интегрируют и сравнивают по амплитуде проинтегрированный информационный сигнал с сигналами заданного уровня положительной и отрицательной полярностей и формируют при этом высокий или низкий уровни выходного бинарного сигнала (см. патент США № 3979746 "High speed Manchester code demodulator", inventor: Bobby R. Jarrett, Assignee: The United States of America as represented by the Secretary of the Navy. (US), Priority data: Apr. 28, 1975).

Указанное техническое решение получило развитие в способе демодуляции сигнала в манчестерском коде, заключающемся в том, что при превышении проинтегрированным информационным сигналом заданных уровней положительной или отрицательной полярности формируют импульсы первой и второй последовательностей, соответствующих единичным и нулевым значениям входного сигнала. Начала импульсов обеих последовательностей формируют в моменты перехода биполярного информационного сигнала от отрицательной полярности к положительной и обратно, а длительность их сигналов устанавливают равной половине периода входного сигнала. Входной сигнал и импульсные сигналы обеих последовательностей нормализуют по амплитуде. Нормализованные сигналы обеих последовательностей складывают с нормализованным входным сигналом со знаками, соответствующими его информационным значениям (см. авторское свидетельство СССР № 1156246, "Способ демодуляции двухфазных трехуровневых сигналов", автор Ю.Г.Байков, МПК Н03К 13/00, опубликовано 15.05.85 г. Бюллетень № 18).

Недостатком обоих упомянутых способов является влияние помех на величину сигнала на выходе интегратора в момент начала очередного информационного интервала, а также то, что на интервалах времени, где отсутствует информационный сигнал, высокочастотные помехи в линии связи даже с небольшой амплитудой вызывают внутри устройства высокочастотные помехи с большой амплитудой.

Наиболее совершенным представляется способ демодуляции сигнала в манчестерском коде, согласно которому биполярный информационный сигнал ограничивают по амплитуде, интегрируют, сравнивают по амплитуде проинтегрированный информационный сигнал с сигналами заданного уровня положительной и отрицательной полярностей, на интервалах времени, где проинтегрированный информационный сигнал превышает по амплитуде сигнал заданного уровня положительной или отрицательной полярности, формируют импульсы соответственно первой и второй последовательностей, в моменты перехода биполярного информационного сигнала от отрицательной полярности к положительной и обратно формируют импульсы соответственно третьей и четвертой последовательностей. В моменты совпадения импульсов первой и четвертой, а также второй и третьей последовательностей формируют положительные фронты меандрового сигнала, которым модулируют по амплитуде входной сигнал перед интегрированием, а также формируют высокий или низкий уровни выходного бинарного сигнала (см. авторское свидетельство СССР № 1330761, "Способ демодуляции биполярного фазоманипулированного сигнала", автор Ю.Г.Байков, МПК Н03М 5/12, опубликовано 15.08.87 г. Бюллетень № 30).

Этот способ выбран в качестве прототипа.

Недостатком данного способа является то, что под влиянием помех, а также при изменении, например, под влиянием температуры окружающей среды, параметров компонентов устройства, используемых для модуляции коэффициента передачи, величина напряжения на выходе интегратора в момент начала очередного разрядного интервала может отличаться от нуля. Поскольку критерием принятия решения о том, что был принят информационный сигнал (ноль или единица), служит результат интегрирования сигнала на первой половине разрядного интервала, отличие начального напряжения на выходе интегратора от нуля в момент начала интегрирования увеличивает вероятность принятия неправильного решения. Следовательно, это обстоятельство не позволяет достичь максимальной помехоустойчивости демодуляции. Кроме того, на интервалах времени, где отсутствует информационный сигнал, высокочастотные помехи в линии связи, даже с небольшой амплитудой, вызывают переключения с высокой частотой компараторов нулевого уровня, что приводит к возникновению внутри устройства высокочастотных помех с большой амплитудой и увеличению потребляемого тока.

Раскрытие изобретения

Задача изобретения - повышение помехоустойчивости демодуляции сигнала.

Технический результат, позволяющий решить задачу повышения помехоустойчивости, заключается в обеспечении нулевого напряжения на выходе интегратора к моменту начала очередного разрядного интервала и запрещении работы компараторов, служащих для обнаружения перехода информационного сигнала через нулевой уровень, на интервалах времени, где отсутствует информационный сигнал. Дополнительно устраняется возможность увеличения потребления тока устройством, реализующим способ.

Для достижения технического результата в способе демодуляции сигнала в манчестерском коде, заключающемся в том, что биполярный информационный сигнал ограничивают по амплитуде, интегрируют, сравнивают по амплитуде проинтегрированный информационный сигнал с сигналами заданного уровня положительной и отрицательной полярностей, на интервалах времени, где проинтегрированный информационный сигнал превышает по амплитуде сигнал заданного уровня отрицательной или положительной полярности, формируют импульсы соответственно первой и второй последовательностей и импульсы третьей и четвертой последовательностей и в моменты их появления формируют соответственно импульсы высокого или низкого уровня выходного бинарного сигнала, согласно изобретению импульсы третьей последовательности формируют в моменты смены знака суммы сигнала первой последовательности и входного сигнала с положительного на отрицательный, импульсы четвертой последовательности формируют в моменты смены знака разности сигнала второй последовательности и входного сигнала с положительного на отрицательный, при этом после появления импульсов третьей и четвертой последовательностей осуществляют обнуление интегратора и удерживают нулевое напряжение на его выходе до конца текущего разрядного интервала.

В предлагаемом решении выходное напряжение интегратора гарантированно приводится к нулю шунтированием интегратора электронным ключом. При недостаточно малом сопротивлении ключа еще больше приблизить сигнал на выходе интегратора к нулю можно, если с помощью дополнительного ключа прервать прохождение сигналов на вход интегратора одновременно с шунтированием емкости интегратора.

Открывание ключа, шунтирующего емкость интегратора, можно начинать ближе к концу разрядного интервала, когда напряжение на выходе интегратора приблизится к нулю под воздействием входного сигнала. Этим достигается уменьшение амплитуды тока через шунтирующий ключ.

Предложенный принцип формирования управляющих импульсов третьей и четвертой последовательностей позволяет на интервалах времени, где отсутствует информационный сигнал, избежать переключения компараторов перехода информационного сигнала через ноль под воздействием помех в линии связи и тем самым предотвратить возможность возникновения в устройстве высокочастотных помех с большой амплитудой.

Краткое описание чертежей

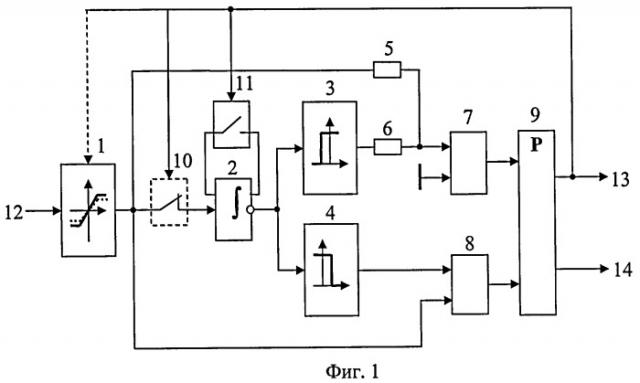

Изобретение поясняется чертежами, приведенным на фиг.1 и фиг.2, где:

на фиг.1 представлена функциональная схема устройства, реализующая данный способ;

на фиг.2 - последовательность операций, осуществляемая устройством при реализации способа.

Варианты осуществления изобретения

Устройство для реализации способа (фиг.1) содержит ограничитель амплитуды входных сигналов 1, интегратор 2 (или апериодическое звено с постоянной времени, оптимизированной по отношению к длительности импульсов входного сигнала), компараторы 3 и 4 сравнения проинтегрированного сигнала с положительным и отрицательным уровнями, резисторы 5 и 6, компараторы 7 и 8, логическое устройство 9, нормально замкнутый ключ 10, нормально разомкнутый ключ 11. На фиг.1 обозначены информационный вход 12, тактовый и информационный выходы 13 и 14.

Устройство работает следующим образом.

Пусть на вход устройства подается последовательность логических сигналов 11001 (фиг.2а). Этой последовательности соответствует сигнал в коде Манчестер, представленный на фиг.2b, поступающий через информационный вход 12 на ограничитель амплитуды входных сигналов 1. Сигнал с выхода ограничителя 1 через нормально замкнутый ключ 10 поступает на вход интегратора 2. Положительный импульс входного сигнала, воздействуя на вход интегратора 2, приводит к нарастанию по абсолютному значению величины отрицательного напряжения на его выходе (фиг.2с). В момент времени t1 выходной сигнал интегратора 2 достигает значения порогового уровня компаратора 3, и сигнал на выходе компаратора 3 (фиг.2d) переходит из высокого уровня в низкий (нулевой), образуя передний фронт первого импульса первой последовательности. Сигнал в точке соединения резисторов 5 и 6 является суммой (с некоторыми весовыми коэффициентами) сигналов первой последовательности и входного сигнала. До момента t1 переключение компаратора 7 под воздействием каких-либо помех невозможно, т.к. напряжение в точке соединения резисторов 5 и 6 (на входе компаратора 7) не может стать отрицательным из-за большого положительного напряжения на выходе компаратора 3. В момент t1 напряжение на выходе компаратора 3 становится нулевым, и знак сигнала в точке соединения резисторов 5 и 6 полностью определяется знаком входного сигнала. В момент перехода значения входного сигнала с положительного на отрицательное напряжение на входе компаратора 7 (фиг.2f) также станет отрицательным, а сигнал на выходе компаратора 7 примет низкий уровень (фиг.2h). Логическое устройство 9, получив на вход сигнал с выхода компаратора 7, устанавливает на выходе 14 логическую единицу (фиг.2k). Емкость интегратора 2 начинает разряжаться вследствие смены полярности входного сигнала, и в момент времени t2, когда уровень напряжения на выходе интегратора 2 станет меньше порогового уровня компаратора 3, уровень сигнала на выходе компаратора 3 станет высоким, сформировав задний фронт первого импульса первой последовательности. Напряжение на входе компаратора 7 (сумма входного напряжения и напряжения с выхода компаратора 2) станет положительным, а уровень напряжения на выходе компаратора 7 - высоким. Единичный уровень на выходе 14 будет сохраняться до появления сигнала с выхода компаратора 8. Логическое устройство 9 формирует импульс на выходе 13 (фиг.2j), используемый для управления компонентами устройства, обеспечивающими обнуление интегратора 2. Этот импульс закрывает ключ 10, прекращающий прохождение информационного сигнала на вход интегратора 2, и открывает ключ 11, обнуляющий интегратор 2 и удерживающий нулевое напряжение на его выходе до момента начала следующего тактового интервала независимо от амплитуды и формы сигнала, действующего в течение второй половины тактового интервала. На следующем тактовом интервале, где также передается логическая единица, процессы на выходах интегратора 2 и компараторов 3 и 7 повторяются, а высокий уровень сигнала на выходе 14 устройства сохраняется.

Процессы, происходящие в устройстве при декодировании сигнала, соответствующего логическому нулю, аналогичны рассмотренным. Импульсы второй последовательности формируются на выходе компаратора 4. Переключения компаратора 4 с высокого уровня на низкий и с низкого на высокий происходят соответственно в моменты времени t3 и t4 (фиг.2е). Компаратор 8 реагирует на разность сигналов второй последовательности и входного сигнала (точнее, сигнала с выхода ограничителя). До момента времени t3 переключение компаратора 8 при воздействии любого входного сигнала невозможно, т.к. сигнал на выходе компаратора 4 превышает любой возможный уровень сигнала на выходе ограничителя (фиг.2g). После момента t3 напряжение на выходе компаратора 4 становится равным нулю, следовательно, переключение компаратора 8 с высокого уровня на низкий произойдет в момент перехода входного сигнала через ноль, т.е. так же, как и при декодировании входного сигнала, соответствующего логической единице, в середине разрядного интервала. Логическое устройство 9, получив сигнал с выхода компаратора 8, установит на выходе 14 логический ноль (фиг.2k), а на выходе 13 сформирует импульс (фиг.2j), используемый для управления компонентами устройства, обеспечивающими обнуление интегратора 2. Импульсы с выхода 13 могут использоваться как тактовые импульсы, сопровождающие информационный сигнал с выхода 14. Эти импульсы закрывают ключ 10, прекращающий прохождение информационного сигнала на вход интегратора 2, и открывают ключ 11, обнуляющий интегратор 2 и удерживающий нулевое напряжение на его выходе до момента начала следующего тактового интервала независимо от амплитуды и формы сигнала, действующего в течение второй половины тактового интервала. Емкость интегратора 2 начинает разряжаться и в момент времени t4, когда абсолютное значение напряжения на выходе интегратора 2 станет меньше порогового уровня компаратора 4, уровень сигнала на выходе компаратора 4 станет высоким, а на выходе компаратора 8 - низким. Низкий уровень на выходе 14 будет сохраняться до появления сигнала с выхода компаратора 7. Обнуление интегратора 2 можно осуществлять и путем модуляции коэффициента передачи ограничителя входного сигнала 1. В этом случае к началу следующего тактового интервала входного сигнала напряжение на интеграторе 2 приходит к нулевому значению под воздействием входного сигнала на второй половине информационного интервала, но может отличаться от нулевой величины при воздействии помех.

Устройство обеспечивает полную повторяемость рассмотренных процессов при демодуляции всех разрядов, исключает переключение с высокой частотой компараторов под воздействием высокочастотных помех на входе устройства, увеличение в связи с этим тока потребления устройства и появление высокочастотных помех с большой амплитудой внутри устройства.

Устройство может использоваться для построения асинхронного канала связи, когда информационные сигналы формируются только при изменении значения передаваемого логического сигнала. В этом случае тактовый выход 13 не используется.

Алгоритм работы логического устройства может быть дополнен функцией установки выхода 14 в нулевое состояние при подаче питания и при длительном отсутствии информационных сигналов.

Промышленная применимость

Наиболее эффективным выглядит его использование в системах сбора и обработки информации интегрированных систем физической защиты объектов с их высокими требованиями к надежности каналов связи. В принципе, возможно использование изобретения в любых системах связи. Рассмотренные выше варианты выполнения изобретения показывают его работоспособность.

1. Способ демодуляции сигнала в манчестерском коде, заключающийся в том, что биполярный информационный сигнал ограничивают по амплитуде, интегрируют, сравнивают по амплитуде проинтегрированный информационный сигнал с сигналами заданного уровня положительной и отрицательной полярностей, на интервалах времени, где проинтегрированный информационный сигнал превышает по амплитуде сигнал заданного уровня отрицательной или положительной полярности, формируют импульсы соответственно первой и второй последовательностей, и импульсы третьей и четвертой последовательностей и в моменты их появления формируют соответственно импульсы высокого или низкого уровня выходного бинарного сигнала, отличающийся тем, что импульсы третьей последовательности формируют в моменты смены знака суммы сигнала первой последовательности и входного сигнала с положительного на отрицательный, импульсы четвертой последовательности формируют в моменты смены знака разности сигнала второй последовательности и входного сигнала с положительного на отрицательный, при этом после появления импульсов третьей и четвертой последовательностей осуществляют обнуление интегратора и удерживают нулевое напряжение на его выходе до конца текущего разрядного интервала.

2. Способ по п.1, отличающийся тем, что обнуление интегратора осуществляют путем шунтирования зарядной емкости интегратора.

3. Способ по п.2, отличающийся тем, что при обнулении интегратора прерывают прохождение сигналов на вход интегратора.

4. Способ по п.2, отличающийся тем, шунтирование осуществляют путем замыкания нормально разомкнутого ключа, шунтирующего зарядную емкость интегратора.

5. Способ по п.3, отличающийся тем, что прерывание прохождения сигналов на вход интегратора осуществляют путем размыкания нормально замкнутого ключа, установленного во входную цепь интегратора.