Способ и устройство суммирования двоично-десятичных кодов

Иллюстрации

Показать всеИзобретение относиться к цифровой вычислительной технике и устройствам автоматики. Технический результат заключается в повышении быстродействия выполнения операции сложения и снижении затратности оборудования. Каждый десятичный разряд устройства содержит пять двоичных разрядов, каждый из которых содержит два RS-триггера, пять логических элементов И, два логических элемента ИЛИ, четыре логических элемента НЕ, каждый десятичный разряд содержит также три логических элемента И, четыре логических элемента ИЛИ, матрицу сложения чисел, одноразрядный трехвходовый сумматор в пятом двоичном разряде. 3 ил., 2 табл.

Реферат

Изобретение относится к области вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики. Известны устройства суммирования двоично-десятичных кодов, содержащие триггерные регистры, схемы формирования сквозного переноса и суммы, логические элементы И, ИЛИ, НЕ и входы управления работой устройства. Варианты таких устройств суммирования детально рассмотрены в книге Карцева М.А. «Арифметика цифровых машин», издательство «Наука», 1969 г., стр.164-186. Известные устройства обладают определенными недостатками, так как требуют дополнительных затрат времени для выполнения корректировки результата суммирования. Известны также способы и устройства «прямого» суммирования десятичных кодов с применением матриц сложения в каждом десятичном разряде. Описание работы такого устройства приведено в указанной книге Карцева М.А. «Арифметика цифровых машин», издательство «Наука», 1969 г., стр.176, рис.2-21. Большим недостатком такого устройства является применение матрицы сложения, требующей не менее 100 элементов И-ИЛИ, что увеличивает затратность оборудования и потребление электропитания и повышает стоимость устройства в целом. Это устройство является прототипом предлагаемого способа и устройства сложения (далее - объект). Предлагаемый объект устраняет недостатки известных устройств прототипа.

Целью предлагаемого объекта является повышение быстродействия за счет исключения операций корректировки суммы, снижение оборудования матрицы сложения и числа триггерных регистров. Для этого предложен способ сложения двоично-десятичных кодов, отличающейся тем, что каждую десятичную цифру первого и второго слагаемых представляют пятью двоичными разрядами, при этом десятичные цифры от единицы до пяти представляют кодами 00001, 00010, 00100, 01000 и 10000 соответственно, цифры от шести до девяти представляют кодами 10001, 10010, 10100, 11000 соответственно; выполнение сложения кодов триггеров первого - четвертого двоичных разрядов и нулевого значения одновременно всех упомянутых разрядов выполняют с помощью матрицы сложения на пять горизонтальных входов, при этом первый - четвертый горизонтальные входы соединены с выходами третьих элементов И первого - четвертого двоичных разрядов соответственно, а нулевой горизонтальный вход матрицы соединен с выходом шестого элемента И, входы которого соединены с выходами третьих элементов НЕ, являющихся нулевыми выходами каждого триггера первого - четвертого двоичных разрядов первого слагаемого, на пять вертикальных входов, при этом первый - четвертый входы подключены к единичным выходам триггеров первого - четвертого разрядов соответственно, а нулевой вертикальный вход соединен с выходом седьмого элемента И, входы которого связаны с нулевыми выходами триггеров первого - четвертого второго слагаемого; в каждой точке пересечения горизонтальных и вертикальных входов матрицы устанавливают элементы И, с помощью каждого элемента И вырабатывают потенциал суммы, соответствующий сумме одной из десятичных цифр, выходы элементов И, установленных на одной диагональной линии матрицы сложения, объединяют через элементы ИЛИ, выходы которых являются выходами суммы матрицы сложения от «0» до 8, одновременно формируют потенциал переноса в пятый двоичный разряд, который вырабатывают при значениях суммы 5, 6, 7, 8, а также при наличии потенциала переноса из младшего десятичного разряда и суммы, равной 4, упомянутые потенциалы переносов объединяют с помощью элемента ИЛИ, выход которого является входом переноса одноразрядного трехвходового сумматора пятого двоичного разряда, второй и третий входы которого являются значениями триггеров пятого двоичного разряда первого и второго слагаемых, сумматор работает по известным правилам двоичного сложения и вырабатывает потенциал суммы пятого двоичного разряда, прямой и инверсный потенциалы переноса в старший десятичный разряд; по завершении формирования переноса и суммы в каждом десятичном разряде результат суммирования, полученный с выходов матрицы сложения и равный цифрам 1, 2, 3, 4 и при отсутствии потенциала переноса из младшего десятичного разряда, через первую группу элементов И, ИЛИ пересылают на входы парафазного приема кода триггеров первого - четвертого двоичных разрядов, при поступлении потенциала переноса из младшего десятичного разряда, результат с выходов матрицы сложения увеличивается на одну единицу за счет пересылки кода через вторую группу элементов И-ИЛИ, обеспечивающую сдвиг результата суммирования на один разряд влево, т.е. в сторону старших разрядов, при этом сумма, сформированная в одноразрядном трехвходовом сумматоре, передается прямо на входы элементов парафазного приема кода триггера пятого двоичного разряда; для занесения результата суммирования в триггеры первого - пятого двоичных разрядов на вход управления приемом суммы в триггеры первого слагаемого подают исполнительный импульс, который устанавливает в нуль или единицу триггеры первого слагаемого в зависимости от значения сигнала суммы, при этом сигнал установки нуля используют для задержки выключения третьего элемента И, инверсное значение сигнала установки единицы используют для запрета включения третьего элемента И на время длительности исполнительного импульса, упомянутая временная задержка сигнала с выхода третьего элемента И позволяет выполнять суммирование на основе двух триггерных регистров. Также предложено устройство суммирования двоично-десятичных кодов, содержащее в каждом десятичном разряде пять двоичных разрядов, каждый из которых содержит первый и второй RS - триггеры, отличающееся тем, что первый и второй элементы И подключены через первый и второй элементы НЕ к нулевому и единичному входам первого RS - триггера, выход первого элемента И соединен с входом первого элемента ИЛИ, второй вход которого подключен к единичному выходу первого RS - триггера, а выход упомянутого элемента ИЛИ соединен с первым входом третьего элемента И, второй вход которого подключен к выходу второго элемента НЕ, выход третьего элемента И соединен с первым входом первого элемента И и входом третьего элемента НЕ, выход этого элемента НЕ соединен с первым входом второго элемента И, вторые входы первого и второго элементов И подключены к выходу и входу четвертого элемента НЕ, третьи входы первого и второго элементов И подключены к входу управления приемом суммы в первый RS - триггер, входы четвертых элементов НЕ первого, второго, третьего и четвертого двоичных разрядов соединены с выходами вторых элементов ИЛИ, входы которых соединены с выходами четвертых и пятых элементов И упомянутых разрядов, каждый десятичный разряд содержит матрицу сложения двух десятичных чисел от нуля до четырех включительно, выполненную на элементах И, ИЛИ, имеющую пять горизонтальных входов значений чисел первого слагаемого, пять вертикальных входов значений чисел второго слагаемого и девять выходов, соответствующих результатам суммирования десятичных чисел от нуля единиц до восьми единиц, в каждой точке пересечения вертикальных и горизонтальных входов матрицы установлены элементы И, вырабатывающие потенциал суммы двух слагаемых, выходы элементов И, расположенных на одной диагональной линии матрицы, объединены через элементы ИЛИ и соединены соответственно с нулевым - восьмым выходами матрицы сложения, одноразрядный трехвходовый сумматор комбинационного типа для суммирования кода пятого двоичного разряда, шестой, седьмой и восьмой элементы И, третий, четвертый, пятый и шестой элементы ИЛИ, при этом выходы третьих элементов НЕ первого, второго, третьего и четвертого двоичных разрядов соединены с входами шестого элемента И, выход которого связан с нулевым горизонтальным входом матрицы сложения, выходы третьих элементов И первого, второго, третьего и четвертого двоичных разрядов соединены с первым, вторым, третьим и четвертым горизонтальными входами матрицы сложения, нулевые выходы вторых RS - триггеров первого, второго, третьего и четвертого двоичных разрядов соединены с входами седьмого элемента И, выход которого соединен с нулевым вертикальным входом матрицы сложения, единичные выходы упомянутых триггеров связаны соответственно с первым, вторым, третьим и четвертым вертикальными входами матрицы сложения, первый, второй и третий выходы матрицы сложения соединены с первыми входами третьего, четвертого и пятого элементов ИЛИ, четвертый выход матрицы сложения соединен с вторым входом четвертого элемента И четвертого двоичного разряда и первым входом восьмого элемента И, пятый, шестой, седьмой и восьмой выходы матрицы сложения соединены с входами шестого элемента ИЛИ, шестой, седьмой и восьмой выходы матрицы сложения связаны с вторыми входами третьего, четвертого и пятого элементов ИЛИ, выход шестого элемента ИЛИ подключен к третьему входу одноразрядного трехвходового сумматора пятого двоичного разряда, первый и второй входы этого сумматора связаны с выходом третьего элемента И упомянутого разряда и с единичным выходом второго RS - триггера этого же разряда, первый выход сумматора соединен с входом четвертого элемента НЕ и вторым входом второго элемента И пятого разряда, а второй и третий выходы сумматора являются прямым и инверсным выходами переноса из i-го десятичного разряда и соединены соответственно с вторыми входами пятых элементов И первого, второго, третьего и четвертого двоичных разрядов и восьмого элемента И (i+1)-го десятичного разряда, и с первыми входами четвертых элементов И первого-четвертого двоичных разрядов i+1-го десятичного разряда, вторые входы четвертых элементов И первого, второго и третьего разрядов соединены соответственно с выходами третьего, четвертого и пятого элементов ИЛИ, первые входы пятых элементов И второго-четвертого разрядов соединены с выходами упомянутых элементов ИЛИ, а первый вход пятого элемента И первого разряда связан с нулевым выходом матрицы сложения, выход восьмого элемента И связан с пятым входом шестого элемента ИЛИ.

Рассмотрим основные отличительные характеристики объекта и покажем что конкретно они обеспечивают.

1. Основными особенностями способа выполнения операции сложения являются следующие:

- представление одного десятичного разряда пятью двоичными разрядами, что позволяет использовать матрицу сложения на 5×5 входов слагаемых и девять выходов суммы;

- получение суммы пятого двоичного разряда с помощью одноразрядного трехвходового сумматора комбинационного типа;

- предлагаемый способ позволяет исключить операции корректировки кода при выполнении операций сложения двоично-десятичных чисел, представленных в коде

«8 4 2 1», что обеспечивает повышение быстродействия работы устройства более чем в два раза. Также повышается быстродействие сложения за счет снижения временных задержек распространения переноса в два раза по сравнению с известными устройствами, каждый десятичный разряд которых построен на основе четырех двоичных разрядов;

- использование в каждом двоичном разряде первого элемента ИЛИ и третьего элемента И с соответствующими связями обеспечивает временную задержку сигнала с выхода третьих элементов И первого - пятого двоичных разрядов на время длительности исполнительного импульса на входе управления приемом суммы в регистр первого слагаемого, что позволяет построить каждый десятичный разряд объекта на основе двух триггерных регистров. В известных устройствах и в прототипе требуется три регистра.

Предлагаемый объект по сравнению с прототипом позволяет повысить быстродействие выполнения операции сложения в 2-3 раза за счет исключения операции корректировки кода десятичного разряда, заключающейся в добавлении к коду суммы кода корректировки, равного 0110. Также быстродействие повышается за счет исключения времени выполнения операций преобразования двоичного - десятичного кода в двоичный до начала вычислений и обратного преобразования двоичного кода в десятичный после выполнения вычислений. При этом имеет место снижение числа логических элементов И-ИЛИ для построения матрицы сложения в четыре раза и снижается число RS - триггеров в каждом десятичном разряде на два триггера (двенадцать против десяти). Основные характеристики сравниваемых устройств приведены в таблице 1.

| Таблица 1 | |||||

| М | Наименование характеристик | Устройство комбинационного типа | Прототип | Предлагаемый объект | Примечание |

| 1 | Операция преобразования десятичного кода в двоичный и наоборот | Есть | Нет | Нет | Повышается быстродействие по сравнению с устройствами комбинационного типа |

| 2 | Операция корректировки кода при сложении чисел в коде «8 4 2 1» | Есть | Нет | Нет | Повышается быстродействие по сравнению с устройствами комбинационного типа |

| 3 | Наличие матрицы сложения в каждом десятичном разряде | Нет | Есть | Есть | Повышается быстродействие по сравнению с устройствами комбинационного типа |

| 4 | Число элементов И-ИЛИ для построения матрицы, ед. | - | 100 | 24 | |

| 5 | Число К8 - триггеров для построения одного десятичного разряда, ед. | 12 | 12 | 10 | |

| 6 | Время выполнения операции сложения (прием, формирование переноса, запоминание суммы), в тактах, ед. | 6 | 3 | 3 | |

| 7 | Число одноразрядных двоичных сумматоров в десятичном разряде, ед. | 4 | - | 1 | |

| 8 | Оценка оборудования одного десятичного разряда (цена Квайна) | 200 | 465 | 292 | Обеспечивается снижение затратности оборудования по сравнению с прототипом в 1,5 раза |

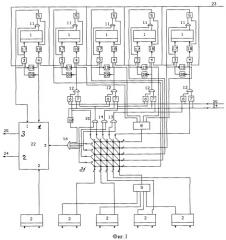

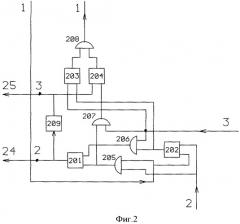

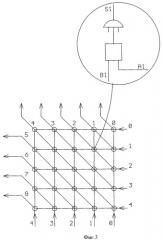

Для пояснения работы предлагаемого объекта на фиг.1, 2 и 3 приведены функциональная схема одного двоично-десятичного разряда устройства, схема одноразрядного трехвходового сумматора и схема матрицы сложения.

На фиг.1 приняты следующие обозначения: RS - триггеры (Тr) 1, 2, логические элементы И 3-10; элементы ИЛИ 11-16; элементы НЕ 17-20, матрица сложения (МС) 21, одноразрядный трехвходовый сумматор (ОТС) 22, вход управления (ВУ) приемом суммы в регистр первого слагаемого (Рr1) 23, вход сигнала переноса из младшего десятичного разряда 24, вход инверсного сигнала переноса из младшего разряда 25. На фиг.2 обозначены элементы И 201-204, элементы ИЛИ 205-208, элемент НЕ 209, входы первого, второго и третьего слагаемых соответственно 1, 2, 3, выход суммы, выходы прямого и инверсионного сигналов переноса 1, 2, 3 соответственно. На фиг.3 обозначены горизонтальные входы первого слагаемого 0, 1, 2, 3, 4, вертикальные входы второго слагаемого 0, 1, 2, 3, 4, выходы матрицы сложения 0, 1, 2, 3, 4, 5, 6, 7 и 8.

Предложенный объект осуществляется следующим образом. В каждом двоичном разряде выход Тr1 через ИЛИ 1, И 5 соединен с входами И 3, НЕ 19. Вторые входы И 3, 4 соединены с выходом и входом НЕ 20, третьи входы И 3, 4 связаны с ВУ 23. В пятом разряде выход И 5 соединен с первым входом ОТС 22. Единичный выход Тr2 пятого разряда связан с вторым входом ОТС 22, нулевые выходы Тr2 первого - четвертого двоичных разрядов соединены с И 9, выход которого связан с нулевым вертикальным входом МС 21, единичные выходы упомянутых триггеров подключены к 1, 2, 3 и 4 вертикальным входам МС 21, выходы НЕ 19 первого - четвертого двоичных разрядов подключены к входам И8, выход этого элемента соединен с нулевым горизонтальным входом МС 21, выходы И 5 первого - четвертого разрядов подключены к 1, 2, 3 и 4 горизонтальным входам МС 21, нулевой выход МС 21 соединен с И 7 первого разряда, первый, второй и третий выходы МС 21 соединены с ИЛИ 13, 14, 15, четвертый выход связан с И 6 четвертого разряда и И 10, пятый выход соединен с ИЛИ 16, шестой, седьмой и восьмой выходы матрицы 21 связаны с ИЛИ 13, 14 и 15 соответственно и с входами ИЛИ 16, выход этого элемента соединен с третьим входом ОТС 22, прямой и инверсный выходы переноса ОТС 22 i-го десятичного разряда соединены соответственно с входами И 7, 6 первого - четвертого двоичных разрядов i+1-го десятичного разряда и с входом И 10, выход И 10 подключен к входу ИЛИ 16, выходы И 6, 7 через ИЛИ 12 первого - четвертого двоичных разрядов соединены с И 4, НЕ 20 этих же разрядов, первый выход ОТС 22 связан с НЕ 20, И 4 пятого двоичного разряда.

Рассмотрим работу устройства при выполнении операции сложения. В исходном положении код первого слагаемого (А) хранится в Тr1 первого - пятого двоичных разрядов. По первому временному такту код второго слагаемого принимается в Тr2 второго слагаемого (В). Второй временной такт отводится для формирования суммы каждого двоичного разряда и максимального переноса по суммарным временным задержкам сигнала, равного 4 n t (n - число десятичных разрядов, t - задержка сигнала переноса на одном элементе И (ИЛИ). В предлагаемом способе сложения имеет место два типа суммирования двоичных кодов. Первый тип суммирования кодов первого - четвертого двоичных разрядов выполняется с помощью матрицы сложения, содержащей 25 логических элементов И-ИЛИ. Каждый элемент И имеет два входа. На первый вход поступает потенциал с единичного выхода одного из триггеров 1-4 разрядов первого слагаемого или нулевой горизонтальный вход, определяющий нулевые состояния всех упомянутых триггеров, т.е. По . На второй вход поступает потенциал с единичного выхода одного из 1-4 триггеров второго слагаемого или нулевой вертикальный вход По 2, определяющий нулевые состояния 1-4 триггеров второго слагаемого, т.е. По . На фиг.3 описания заявки представлена матрица сложения. Матрица содержит 5 горизонтальных входов А4, А3, А2, А1 По 1, пять вертикальных входов В4, В3, В2, В1, По 2 и на 9 выходов суммы, равных цифрам 8, 7, 6, 5, 4, 3, 2, 1, 0. В точках пересечения упомянутых входов установлены логические элементы И-ИЛИ. Все выходы элементов И-ИЛИ, установленные на одной диагональной линии матрицы, объединены между собой и соответствуют потенциалу одной из цифр суммы. Если на входы элемента И-ИЛИ поступили два потенциала, например, с горизонтального первого и вертикального третьего входов, то на выходе этого элемента И - ИЛИ будет выработан потенциал, соответствующий сумме, равной десятичному числу 4. Этот потенциал по третьему временному такту, если из младшего десятичного разряда не поступит сигнал переноса, заносится в триггер четвертого разряда первого слагаемого. В том случае, если из младшего десятичного разряда по входу 24 поступил потенциал переноса, то значение суммы десятичного разряда, равной 4, увеличивается на одну единицу, т.е. в нашем примере с выхода И 10 через ИЛИ 16 на вход сумматора 22 поступит потенциал, соответствующий цифре 5, который является входом потенциала переноса в пятый двоичный разряд. По t3 результат суммирования будет занесен парафазным кодом в Тr1 пятого разряда. Второй тип суммирования выполняется в пятом двоичном разряде с помощью одноразрядного трехвходового комбинационного сумматора 22, в котором перенос и сумма вырабатывается согласно общеизвестным соотношениям (фиг.2).

Здесь А5 В5 - значения слагаемых пятого двоичного разряда (входы 1 и 2);

Р4 - перенос из четвертого разряда (вход 3);

Р5, - прямое и инверсное значения переносов, выработанные в 5 двоичном разряде (выходы 2 и 3);

S5 - сумма пятого разряда (выход сумматора 1).

Рассмотрим пример сложения 2+3=5. При сложении кодов 00010 (2) и 00100 (3) результат будет 10000 (5). При этом потенциал с единичного выхода Тr1 второго разряда первого слагаемого через элементы ИЛИ 1, И 5 поступит на второй горизонтальный вход МС, потенциал с единичного выхода Тr2 третьего разряда второго слагаемого поступит на третий вертикальный вход МС. На логическом элементе И-ИЛИ, установленном в точке пересечения второго горизонтального и третьего вертикального входов будет выработан потенциал, который соответствует сумме первого и второго слагаемых, т.е. 5 единицам. Этот потенциал через ИЛИ 16 поступит на третий вход ОТС 22, с первого выхода которого будет выработан потенциал, соответствующий числу 5. По t3 код суммы десятичного разряда будет занесен парафазным кодом в Тr1 пятого разряда. Для этого на ВУ 23 поступит исполнительный импульс, который занесет код суммы в триггеры первого слагаемого. Так как только на входе И 4 пятого разряда будет присутствовать высокий потенциал, а на И 4 первого - четвертого разрядов будут отсутствовать высокие потенциалы, то в Тr1 пятого разряда будет занесена единица, а Тr1 первого - четвертого разрядов будут установлены в «0».

Пример сложения 9+9=18 (плюс 1 переноса из младшего десятичного разряда).

При сложении кода 11000 (9) и 11000 (9) и при поступлении переноса из младшего десятичного разряда получаем сумму, равную 1.11000 (19). По второму временному такту на четвертые входы МС поступают высокие потенциалы с выходов Тr1, 2 четвертых двоичных разрядов. На восьмом выходе МС будет выработан потенциал, который через ИЛИ 16 поступит на третий вход ОТС 22. Одновременно упомянутый сигнал поступает через ИЛИ 15 на И 6,7 третьего и четвертого двоичного разряда. Так как на второй вход И 7 четвертого разряда по входу 24 поступил потенциал переноса из младшего десятичного разряда, то потенциалы с восьмого выхода МС поступят через И 7, ИЛИ 12 на входы И 4, НЕ 20 четвертого двоичного разряда. Одновременно на 1, 2 и 3 входы ОТС 22 поступают потенциалы первого, второго и третьего слагаемых. С первого выхода ОТС 22 будет выработан потенциал суммы пятого двоичного разряда, а с второго выхода будет поступать потенциал переноса в старший десятичный разряд (см. стр.3, соотношение 2 и 1). По третьему временному такту на ВУ 23 поступит исполнительный импульс и занесет в Тr1 четвертого и пятого разрядов первого регистра коды единиц, что соответствует цифре 9. Перенос в старший десятичный разряд, поступающий по входу 24 по цепи элементов И 7, ИЛИ 12 поступит на входы И 4, НЕ 20 Тr1 первого двоичного разряда. По третьему временному такту упомянутый триггер будет установлен в единицу. Результат суммирования 1.11000 (19).

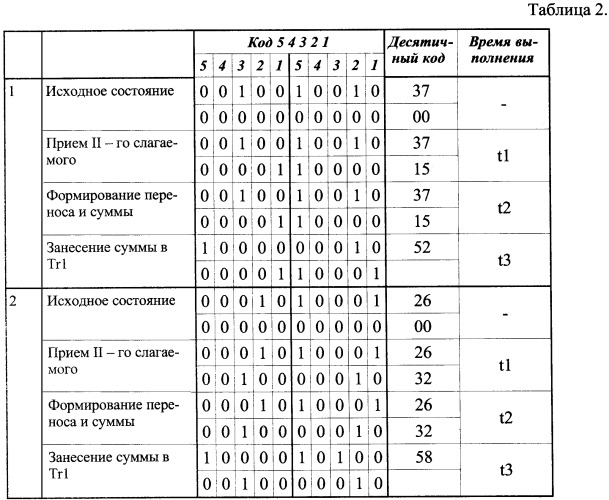

После завершения формирования переноса и суммы в каждом десятичном разряде по третьему временному такту на ВУ 23 поступает исполнительный импульс, который занесет значение суммы в Тr1, сформированной на нулевом - восьмом выходах МС 21 и на первом выходе ОТС 22. При этом, если на входе 24 отсутствует высокий потенциал, т.е. в i-ый десятичный разряд не поступил перенос из i-1-го разряда, то сигналы, соответствующие коду единицы, передаются по цепи элементов И 6, ИЛИ 12, И 4 и НЕ 18 на вход Тr1 первого - четвертого разрядов и с выхода ОТС 22 через И 4, НЕ 18 на вход Тr1 пятого разряда. В том случае, если в десятичный разряд поступил перенос из младшего разряда, то сумма, полученная с нулевого выхода, выходов ИЛИ 13, 14, 15 и с четвертого выхода МС 22, увеличивается на единицу. Примеры суммирования двухразрядных двоично-десятичных чисел приведены в таблице 2.

Таким образом, предлагаемые способ и устройство позволяют повысить быстродействие выполнения операции сложения при некотором сокращении аппаратурных затрат.

1. Способ суммирования двоично-десятичных кодов, отличающийся тем, что каждую десятичную цифру первого и второго слагаемых представляют пятью двоичными разрядами, при этом десятичные цифры от единицы до пяти представляют кодами 00001, 00010, 00100, 01000 и 10000 соответственно, цифры от шести до девяти представляют кодами 10001, 10010, 10100, 11000 соответственно; выполнение сложения кодов триггеров первого - четвертого двоичных разрядов и нулевого значения одновременно всех упомянутых разрядов выполняют с помощью матрицы сложения на пять горизонтальных входов, при этом первый - четвертый горизонтальные входы соединены с выходами третьих элементов И первого - четвертого двоичных разрядов соответственно, а нулевой горизонтальный вход матрицы соединен с выходом шестого элемента И, входы которого соединены с выходами третьих элементов НЕ, являющихся нулевыми выходами каждого триггера первого - четвертого двоичных разрядов первого слагаемого, на пять вертикальных входов, при этом первый - четвертый входы подключены к единичным выходам триггеров первого - четвертого разрядов соответственно, а нулевой вертикальный вход соединен с выходом седьмого элемента И, входы которого связаны с нулевыми выходами триггеров первого - четвертого второго слагаемого; в каждой точке пересечения горизонтальных и вертикальных входов матрицы устанавливают элементы И, с помощью каждого элемента И вырабатывают потенциал суммы, соответствующий сумме одной из десятичных цифр, выходы элементов И, установленных на одной диагональной линии матрицы сложения, объединяют через элементы ИЛИ, выходы которых являются выходами суммы матрицы сложения от 0 до 8; одновременно формируют потенциал переноса в пятый двоичный разряд, который вырабатывают при значениях суммы 5, 6, 7, 8, а также при наличии потенциала переноса из младшего десятичного разряда и суммы, равной 4, упомянутые потенциалы переносов объединяют с помощью элемента ИЛИ, выход которого является входом переноса одноразрядного трехвходового сумматора пятого двоичного разряда, второй и третий входы которого являются значениями триггеров пятого двоичного разряда первого и второго слагаемых, сумматор работает по известным правилам двоичного сложения и вырабатывает потенциал суммы пятого двоичного разряда, прямой и инверсный потенциалы переноса в старший десятичный разряд; по завершению формирования переноса и суммы в каждом десятичном разряде результат суммирования, полученный с выходов матрицы сложения и равный цифрам 1, 2, 3, 4 и при отсутствии потенциала переноса из младшего десятичного разряда, через первую группу элементов И, ИЛИ пересылают на входы парафазного приема кода триггеров первого - четвертого двоичных разрядов, при поступлении потенциала переноса из младшего десятичного разряда, результат с выходов матрицы сложения увеличивается на одну единицу за счет пересылки кода через вторую группу элементов И-ИЛИ, обеспечивающую сдвиг результата суммирования на один разряд влево, в сторону старших разрядов, при этом сумма, сформированная в одноразрядном трехвходовом сумматоре, передается прямо на входы элементов парафазного приема кода триггера пятого двоичного разряда; для занесения результата суммирования в триггеры первого - пятого двоичных разрядов на вход управления приемом суммы в триггеры первого слагаемого подают исполнительный импульс, который устанавливает в нуль или единицу триггеры первого слагаемого в зависимости от значения сигнала суммы, при этом сигнал установки нуля используют для задержки выключения третьего элемента И, инверсное значение сигнала установки единиц используют для запрета включения третьего элемента И на время длительности исполнительного импульса, упомянутая задержка сигнала с выхода третьего элемента И позволяет выполнять суммирование на основе двух триггерных регистров.

2. Устройство суммирования двоично-десятичных кодов, содержащее в каждом десятичном разряде пять двоичных разрядов, каждый из которых содержит первый и второй RS-триггеры, отличающееся тем, что первый и второй элементы И подключены через первый и второй элементы НЕ к нулевому и единичному входам первого RS-триггера, выход первого элемента И соединен с входом первого элемента ИЛИ, второй вход которого подключен к единичному выходу первого RS-триггера, а выход упомянутого элемента ИЛИ соединен с первым входом третьего элемента И, второй вход которого подключен к выходу второго элемента НЕ, выход третьего элемента И соединен с первым входом первого элемента И и входом третьего элемента НЕ, выход этого элемента НЕ соединен с первым входом второго элемента И, вторые входы первого и второго элементов И подключены к выходу и входу четвертого элемента НЕ, третьи входы первого и второго элементов И подключены к входу управления приемом суммы в первый RS-триггер, входы четвертых элементов НЕ первого, второго, третьего и четвертого двоичных разрядов соединены с выходами вторых элементов ИЛИ, входы которых соединены с выходами четвертых и пятых элементов И упомянутых разрядов; каждый десятичный разряд содержит матрицу сложения двух десятичных чисел от нуля до четырех включительно, выполненную на элементах И, ИЛИ, имеющую пять горизонтальных входов значений чисел первого слагаемого, пять вертикальных входов значений чисел второго слагаемого и девять выходов, соответствующих результатам суммирования десятичных чисел от нуля единиц до восьми единиц, в каждой точке пересечения вертикальных и горизонтальных входов матрицы установлены элементы И, вырабатывающие потенциал суммы двух слагаемых, выходы элементов И, расположенных на одной диагональной линии матрицы, объединены через элементы ИЛИ и соединены соответственно с нулевым - восьмыми выходами матрицы сложения, одноразрядный трехвходовый сумматор комбинационного типа для суммирования кода пятого двоичного разряда, шестой, седьмой и восьмой элементы И, третий, четвертый, пятый и шестой элементы ИЛИ, при этом выходы третьих элементов НЕ первого, второго, третьего и четвертого двоичных разрядов соединены с входами шестого элемента И, выход которого связан с нулевым горизонтальным входом матрицы сложения, выходы третьих элементов И первого, второго, третьего и четвертого двоичных разрядов соединены с первым, вторым, третьим и четвертым горизонтальными входами матрицы сложения, нулевые выходы вторых RS-триггеров первого, второго, третьего и четвертого двоичных разрядов соединены с входами седьмого элемента И, выход которого соединен с нулевым вертикальным входом матрицы сложения, единичные выходы упомянутых триггеров связаны соответственно с первым, вторым, третьим и четвертым вертикальными входами матрицы сложения, первый, второй и третий выходы матрицы сложения соединены с первыми входами третьего, четвертого и пятого элементов ИЛИ, четвертый выход матрицы сложения соединен со вторым входом четвертого элемента И четвертого разряда и первым входом восьмого элемента И, пятый, шестой, седьмой и восьмой выходы матрицы сложения соединены с входами шестого элемента ИЛИ, шестой, седьмой и восьмой выходы матрицы сложения связаны с вторыми входами третьего, четвертого и пятого элементов ИЛИ, выход шестого элемента ИЛИ подключен к третьему входу одноразрядного трехвходового сумматора пятого разряда, первый и второй входы этого сумматора связаны с выходом третьего элемента И упомянутого разряда и с единичным выходом второго RS-триггера этого же разряда, первый выход сумматора соединен с входом четвертого элемента НЕ и вторым входом второго элемента И пятого разряда, а второй и третий выходы сумматора являются прямым и инверсным выходами переноса из i-го десятичного разряда и соединены соответственно с вторыми входами пятых элементов И первого, второго, третьего и четвертого двоичных разрядов и восьмого элемента И (i+1)-го десятичного разряда и с первыми входами четвертых элементов И первого - четвертого двоичных разрядов (i+1)-го десятичного разряда, вторые входы четвертых элементов И первого, второго и третьего разрядов соединены соответственно с выходами третьего, четвертого и пятого элементов ИЛИ, первые входы пятых элементов И второго - четвертого разрядов соединены с выходами упомянутых элементов ИЛИ, а первый вход пятого элемента И первого разряда связан с нулевым выходом матрицы сложения, выход восьмого элемента И связан с пятым входом шестого элемента ИЛИ.