Способ скалярного управления матричным преобразователем частоты

Иллюстрации

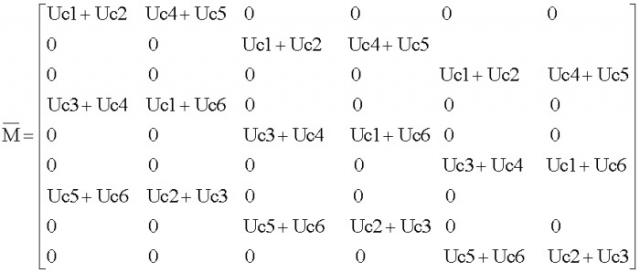

Показать всеИзобретение относится к области электротехники и может быть использовано в частотно-регулируемом электроприводе для регулирования трехфазного напряжения и частоты на выходе матричного преобразователя, который выполнен на 9 транзисторах в узлах решетки, образованной пересечениями i=1, 2 трехфазных горизонтальных шин питания и j=1, 2 трехфазных вертикальных шин нагрузки. Техническим результатом является поддержание высокого качества регулирования в нижней части диапазона с возможностью установки любых значений коэффициента сдвига тока на сетевом входе. Переключения транзисторов осуществляют с помощью управляющих импульсов, которые вырабатывают в соответствии с уравнением , где - матрица, размерностью 9×6, которую формируют с помощью синхронизирующих импульсов длительностью π/3, совпадающих с интервалами, на которых междуфазные напряжения питающей сети изменяются в заданном диапазоне; - шестимерный вектор модулированных по ширине первичных управляющих импульсов, которые вырабатывают на высокой несущей частоте в результате сравнения трехфазной системы задающих сигналов гармонической формы с опорным сигналом. Последний получают непрерывным интегрированием указанных междуфазных напряжений сети и их инвертированием при каждом достижении опорным сигналом установленного порогового уровня. 1 з.п. ф-лы, 3 ил., 1 табл.

Реферат

Изобретение относится к преобразовательной технике, используемой в частотно-регулируемом электроприводе. В настоящее время в указанной области начинают получать применение матричные преобразователи частоты (МПЧ), выполняемые на транзисторных ключах с двухсторонней проводимостью тока. Наибольшим признанием пользуется МПЧ на девяти транзисторных ключах, установленных в узлах решетки, образованной пересечением трех подключенных к фазам питающей сети А, В, С горизонтальных шин с номерами i=1, 2, 3 и подключенных к фазам а, b, с нагрузки вертикальных шин с порядковыми номерами j=1, 2, 3 (см. Виноградов А.Б. Новые алгоритмы пространственно-векторного управления матричным преобразователем частоты. - Электричество, №3/2008). Аналогично тому, как это делается в 3-фазных автономных инверторах напряжения (АИН), выходное напряжение данных преобразователей может быть представлено в векторной или скалярной форме. Получающий в АИН применение известный алгоритм скалярного управления основывается на широтно-импульсной модуляции 3-фазного напряжения (см. Соколовский Г.Г. Электроприводы переменного тока с частотным регулированием. - М.: Изд. «Академия», 2006, с.83-90). Для его реализации предусматривается выработка первичных управляющих импульсов на выходе широтно-импульсного модулятора и последующее распределение этих импульсов по транзисторным ключам с помощью специального распределителя. Как правило, формирование первичных импульсов в модуляторе происходит в моменты равенства периодически изменяющегося опорного сигнала тактовой частоты с 3-фазной системой задающих напряжений гармонической формы. Осуществляемое в процессе регулирования изменение амплитуды и частоты задающих сигналов сопровождается модуляцией ширины первичных импульсов и, соответственно, таким же изменением параметров основной гармоники 3-фазного напряжения на выходе АИН. В этом и состоит основная сущность рассматриваемого алгоритма. Однако реализация скалярного управления в схемах МПЧ пока не получила приемлемого решения, так как затруднена более сложной, чем в АИН, топологией силовой схемы, большим количеством комбинаций включаемых вентилей, а также тем, что питание данных устройств происходит от источника переменного многофазного напряжения, что снижает качество выходной ЭДС в связи с попаданием в нагрузку низкочастотных сетевых пульсаций. В свою очередь векторный способ управления может быть реализован лишь на основе высокопроизводительных микропроцессоров и потому ограничен в массовом применении. В этой связи целью изобретения являлась разработка сравнительно простого способа скалярного управления матричным преобразователем, реализация которого была бы возможной как на цифровой, так и аналоговой элементной базе.

Для решения этих задач предлагается:

- указанный опорный сигнал получать непрерывным интегрированием сетевого выпрямленного напряжения, который, в свою очередь, можно получить на выходе вспомогательного 3-фазного двухполупериодного выпрямителя и инвертированием этого напряжения при каждом достижении опорным сигналом установленного порогового уровня;

- распределение управляющих импульсов по транзисторам производить по команде логических синхронизирующих сигналов, совпадающих с временными промежутками, на которых междуфазные напряжения сети изменяются в пределах от 0,86 до 1 по отношению к амплитудному значению, согласно уравнению ,

где: - вектор логических сигналов в виде управляющих импульсов для транзисторных ключей с указанием в виде индексов порядковых номеров присоединенных к транзистору горизонтальных и вертикальных шин матричного преобразователя;

- модуляционная матрица, образованная логическими сигналами синхронизирующих импульсов;

- вектор модулированных по ширине первичных управляющих импульсов;

- в отличие от перечисленного, в нижней части диапазона регулирования синхронизирующие сигналы вырабатывать таким образом, чтобы они совпадали с промежутками времени, на которых междуфазное выпрямленное напряжение сети изменяется в пределах от 0,5 до 0,86 своего амплитудного значения, соответственно этому опорный сигнал получать непрерывным интегрированием указанного напряжения с его инвертированием в моменты достижения опорным сигналом установленного порогового уровня.

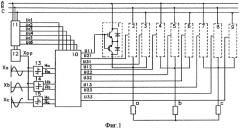

На фиг.1 изображена схема матричного преобразователя, а на фиг.2, 3 - полученные компьютерным моделированием диаграммы работы данного устройства в соответствии с предлагаемым способом управления. Силовая часть преобразователя выполнена на транзисторных ключах 1-9, обладающих двухсторонней проводимостью тока. Ключи располагаются на пересечении горизонтальных шин с порядковыми номерами i=1, 2, 3, подключенных к фазам питающей сети А, В, С и вертикальных шин с номерами j=1, 2, 3, присоединенных к фазам нагрузки а, b, с, соответственно. На управляющие входы транзисторов с выхода распределителя 10 поступают управляющие сигналы Uij с индексами, соответствующими номерам указанных горизонтальных и вертикальных шин, на пересечении которых установлен тот или иной транзистор. На входы распределителя с выходов широтно-импульсного модулятора поступают первичные управляющие импульсы Ha, , Hb, , Hc, , распределение которых происходит по команде синхронизирующих сигналов Uc1, Uc2, Uc3, Uc4, Uc5, Uc6, поступающих с выходов формирователя 11, имеющего в своем составе вспомогательный 3-фазный неуправляемый двухполупериодный выпрямитель на диодах, причем последний подключен своими входами к фазам А, В, С питающей сети. Своими другими выходами указанный выпрямитель подключен к формирователю 12 опорного сигнала тактовой частоты Хор. Этот сигнал поступает на первые входы широтно-импульсного модулятора, содержащего компараторы 13, 14, 15, на вторые входы которых поступают 3-фазные задающие напряжения Ха, Xb, Хс синусоидальной формы. При этом импульсы в виде инверсных по отношению друг к другу логических переменных На, формируются на выходах компаратора 13 в результате сравнения Хор с задающим напряжением фазы А (Ха), а импульсы Hb, , Hc, формируются аналогичным образом на выходах компараторов 14, 15 в результате сравнения Хор с задающими напряжениями фаз В, С (Xb, Хс) соответственно.

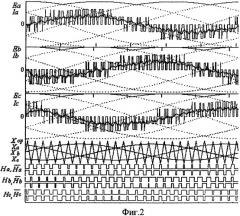

Согласно предлагаемым техническим решениям, мгновенные значения фазных ЭДС Еа, Eb, Ес на выходе матричного преобразователя повторяют ту или иную кривую выпрямленного напряжения сети с меняющимся коэффициентом масштабирования ±1/3, ±2/3. Известно, что частота пульсаций в результате 3-фазного двухполупериодного выпрямления сравнительно низка и составляет 300 Гц. Скомпенсировать влияние низкочастотных пульсаций на полезную составляющую ЭДС и тока нагрузки на выходе преобразователя можно добавочным изменением ширины первичных управляющих импульсов, получаемых на выходах компараторов 13-15. Для этого опорный сигнал Хор предлагается получать в блоке 12 путем непрерывного интегрирования поступающего из блока 11 выпрямленного напряжения сети и инвертирования последнего при каждом достижении сигналом Хор некоторого порогового уровня. Получаемый таким образом сигнал Хор, как это видно из диаграмм фиг.2, 3, имеет циклически повторяющуюся квазипилообразную форму, которая содержит информацию об интегральных значениях сетевого напряжения. Очевидно, что при такой форме опорного сигнала процессу широтно-импульсной модуляции будут подвергаться не мгновенные, а усредненные значения пульсирующего напряжения сети, в результате влияние низкочастотных пульсаций на ток в цепях индуктивной нагрузки будет устранено. Можно заметить, что в отличие от традиционных методов стабилизации напряжения, предлагаемый способ подавления пульсаций проще в реализации, так как не требует применения специальных цепей обратных связей. Видно также, что изменением порогового уровня можно установить любые пределы изменения тактовой частоты модуляции, что также упрощает реализацию предлагаемого решения.

Порядок переключения транзисторных ключей в схеме фиг.1 задается управляющими импульсами Uij с выходов распределителя 10. Распредедитель может быть выполнен на двухвходовых логических схемах совпадения, на первые входы которых подаются первичные управляющие импульсы Ha, , Hb, , Hc, , а на вторые (разрешающие) входы - синхронизирующие сигналы Uc1, Uc2, Uc3, Uc4, Uc5, Uc6. Согласно первому предложению полагается, что каждый из этих сигналов имеет конечную длительность Uc1=Uab; Uc2=Uac; Uc3=Ubc; Uc4=Uba; Uc5=Uca; Uc6=Ucb, равную тому интервалу времени, на котором соответствующее индексу питающее междуфазное напряжение сети изменяется в пределах от 0,86 до 1 по отношению к амплитуде, то есть имеет наиболее положительные по сравнению с другими значения. Независимо от формы и расположения синхроимпульсов алгоритм формирования управляющих сигналов на выходе распределителя можно представить логическим уравнением в универсальной матричной форме записи

где:

- вектор логических сигналов управления транзисторными ключами с указанием в виде индексов места присоединения ключа к горизонтальным и вертикальным шинам матричного преобразователя;

- модуляционная матрица, образованная синхронизирующими логическими сигналами;

вектор логических сигналов в виде модулированных по ширине первичных управляющих импульсов.

Рассмотрим работу устройства на интервале T=π/3, когда наибольшие положительные значения имеет междуфазное напряжение сети ЕАВ, а синхронизирующие импульсы представлены выражениями Uc1=Uab=1, Uc2=Uc3=Uc4=Uc5=Uc6=0. На данном интервале, так же как и на любом другом, три логических переменных На, Hb, Нс могут образовывать 23=8 комбинаций, каждой из которых соответствуют определенные значения фазных ЭДС на выходе преобразователя. Задаваясь в уравнении (1) одной из комбинаций На=1, , Hb=1, , Hc=1, ,видим, что она приведет к появлению на выходах распределителя единичных сигналов U11=U22=U32=1,в то время, как на остальных выходах распределителя управляющие сигналы будут равны нулю. В соответстветствии с этими сигналами произойдет включение транзисторных ключей с номерами 1, 5, 6, что в итоге приведет к появлению в цепях нагрузки фазных ЭДС величиной Еа=-+2/3ЕАВ; Eb=-1/3ЕАВ,

Ес=-1/3ЕАВ, где EAB - сетевое междуфазное напряжение питания, принимающее на рассматриваемом интервале наибольшие положительные значения. Аналогичным образом будет происходить работа МПЧ и при других комбинациях управляющих и синхронизирующих импульсов.

Второе предложение направлено на поддержание высокого качества регулирования в нижней части диапазона, когда снижение скважности импульсной ЭДС заметно увеличивает глубину пульсаций тока нагрузки. Уменьшить глубину пульсаций тока можно за счет сочетания широтной и амплитудной модуляции выходной ЭДС. При этом необходимого снижения питающего напряжения можно добиться, включая транзисторы на тех интервалах времени, когда междуфазное сетевое напряжение изменяется в пределах от 0,5 до 0,86 амплитудного значения. Для этого синхронизирующие сигналы должны формироваться в соответствии со следующими логическими уравнениями:

;

,

где U〈ab〉, U〈ac〉, U〈bc〉, U〈ba〉, U〈ca〉, U〈cb〉 - синхронизирующие импульсы длительностью 2π/3, располагающиеся симметрично относительно ранее упоминавшихся импульсов Uab, Uca, Ubc, Uba, Uca, Ucb. Диаграммы на фиг.3 подтверждают, что в этом случае фазные ЭДС Еа, Eb, Ес на выходе преобразователя начинают формироваться из участков выпрямленного напряжения меньшего уровня, сохраняя тем самым высокое качество тока нагрузки в нижней части диапазона регулирования. Полный набор возможных комбинаций включаемых вентилей при указанных алгоритмах двухуровневого регулирования отражен в сводной таблице 1.

| Таблица 1 | ||||||||

| Uc1=1 | ||||||||

| На | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| Hb | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| Hc | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| Ключи | 4 | 4 | 4 | 4 | 1 | 1 | 1 | 1 |

| 5 | 5 | 2 | 2 | 5 | 5 | 2 | 2 | |

| 6 | 3 | 6 | 3 | 6 | 3 | 6 | 3 | |

| Еа | 0 | -1/3ЕАВ | -1/3ЕАВ | -2/3ЕАВ | 2/3ЕАВ | 1/3ЕАВ | 1/3ЕАВ | 0 |

| Eb | 0 | -1/3ЕАВ | 2/3ЕАВ | 1/3ЕАВ | -1/3ЕАВ | -2/3ЕАВ | 1/3ЕАВ | 0 |

| Ec | 0 | 2/3ЕАВ | -1/3ЕАВ | 1/3ЕАВ | -1/3ЕАВ | 1/3ЕАВ | -2/3ЕАВ | 0 |

| Uc2=1 | ||||||||

| На | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| Hb | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| Hc | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| Ключи | 7 | 7 | 7 | 7 | 1 | 1 | 1 | 1 |

| 8 | 8 | 2 | 2 | 8 | 8 | 2 | 2 | |

| 9 | 3 | 9 | 3 | 9 | 3 | 9 | 3 | |

| Еа | 0 | -1/3ЕАС | -1/3ЕАС | -2/3ЕАС | 2/3ЕАС | 1/3ЕАС | 1/3ЕАС | 0 |

| Eb | 0 | -1/3ЕАС | 2/3ЕАС | 1/3ЕАС | -1/3ЕАС | -2/3ЕАС | 1/3ЕАС | 0 |

| Ec | 0 | 2/3ЕАС | -1/3ЕАС | 1/3ЕАС | -1/3ЕАС | 1/3ЕАС | -2/3ЕАС | 0 |

| Uc3=1 | ||||||||

| На | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| Hb | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| Hc | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| Ключи | 7 | 7 | 7 | 7 | 4 | 4 | 4 | 4 |

| 8 | 8 | 5 | 5 | 8 | 8 | 5 | 5 | |

| 9 | 6 | 9 | 6 | 9 | 6 | 9 | 6 | |

| Еа | 0 | -1/3ЕВС | -1/3ЕВС | -2/3ЕВС | 2/3ЕВС | 1/3ЕВС | 1/3ЕВС | 0 |

| Eb | 0 | -1/3ЕВС | 2/3ЕВС | 1/3ЕВС | -1/3ЕВС | -2/3ЕВС | 1/3ЕВС | 0 |

| Ec | 0 | 2/3ЕВС | -1/3ЕВС | 1/3ЕВС | -1/3ЕВС | 1/3ЕВС | -2/3ЕВС | 0 |

| Продолжение табл.1 | ||||||||

| Uc4=1 | ||||||||

| На | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| Hb | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| Hc | 0 | 1 | 0 | I | 0 | 1 | 0 | 1 |

| Ключи | 4 | 4 | 4 | 4 | 1 | 1 | 1 | 1 |

| 5 | 5 | 2 | 2 | 5 | 5 | 2 | 2 | |

| 6 | 3 | 6 | 3 | 6 | 3 | 6 | 3 | |

| Еа | 0 | 1/3ЕВА | 1/3ЕВА | 2/3ЕВА | -2/3ЕВА | -1/3ЕВА | -1/3ЕВА | 0 |

| Eb | 0 | 1/3ЕВА | -2/3ЕВА | -1/3ЕВА | 1/3ЕВА | 2/3ЕВА | -1/3ЕВА | 0 |

| Ec | 0 | -2/3ЕВА | 1/3ЕВА | -1/3ЕВА | 1/3ЕВА | -1/3ЕВА | 2/3ЕВА | 0 |

| Uc5=1 | ||||||||

| На | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| Hb | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| Hc | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| Ключи | 7 | 7 | 7 | 7 | 1 | 1 | 1 | 1 |

| 8 | 8 | 2 | 2 | 8 | 8 | 2 | 2 | |

| 9 | 3 | 9 | 3 | 9 | 3 | 9 | 3 | |

| Еа | 0 | 1/3ЕСА | 1/3ЕСА | 2/3ЕСА | -2/3ЕСА | -1/3ЕСА | -1/3ЕСА | 0 |

| Eb | 0 | 1/3ЕСА | -2/3ЕСА | -1/3ЕСА | 1/3ЕСА | 2/3ЕСА | -1/3ЕСА | 0 |

| Ec | 0 | -2/3ЕСА | 1/3ЕСА | -1/3ЕСА | 1/3ЕСА | -1/3ЕСА | 2/3ЕСА | 0 |

| Uc6=1 | ||||||||

| На | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| Hb | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| Hc | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| Ключи | 7 | 7 | 7 | 7 | 4 | 4 | 4 | 4 |

| 8 | 8 | 5 | 5 | 8 | 8 | 5 | 5 | |

| 9 | 6 | 9 | 6 | 9 | 6 | 9 | 6 | |

| Еа | 0 | 1/3ЕСВ | 1/3ЕСВ | 2/3ЕСВ | -2/3ECB | -1/3ЕСВ | -1/3ЕСВ | 0 |

| Eb | 0 | 1/3ЕСВ | -2/3ЕСВ | -1/3ЕСВ | 1/3ЕСВ | 2/3ЕСВ | -1/3ЕСВ | 0 |

| Ec | 0 | -2/3ЕСВ | 1/3ЕСВ | -1/3ЕСВ | 1/3ЕСВ | -1/3ЕСВ | 2/3ЕСВ | 0 |

1. Способ скалярного управления матричным преобразователем частоты, выполненным в виде решетки на пересечениях, подключенных к фазам питающей сети А, В, С горизонтальных шин с номерами i=1, 2, 3, и подключенных к фазам a, b, c нагрузки вертикальных шин с номерами j=1, 2, 3 соответственно, с установленными в узлах девятью транзисторными ключами, обладающими двухсторонней проводимостью тока и управляемыми импульсами Uij, состоящий в том, что с помощью широтно-импульсного модулятора вырабатывают шесть последовательностей первичных управляющих импульсов в виде логических сигналов На, , Hb, , Hc, , сформированных и модулированных по ширине путем сравнения трехфазной системы задающих напряжений синусоидальной формы с периодически изменяющимся опорным сигналом тактовой частоты, причем противофазные импульсы На, формируют путем сравнения опорного сигнала с задающим напряжением фазы А, а импульсы Hb, , Hc, формируют аналогичным образом в результате сравнений создающими напряжениями фаз В и С соответственно, а для распределения первичных управляющих импульсов по транзисторным ключам используют логические синхронизирующие сигналы Uc1, Uc2, Uc3, Uc4, Uc5, Uc6, совпадающие с интервалами максимальных значений выпрямленного напряжения, которое вырабатывают на выходе вспомогательного трех фазного двухполупериодного неуправляемого выпрямителя, отличающийся тем, что опорный сигнал получают непрерывным интегрированием упомянутого выпрямленного напряжения и его инвертированием при каждом достижении опорным сигналом установленного порогового уровня, а упомянутое распределение первичных управляющих импульсов осуществляют по разрешающей команде синхронизирующих сигналов, совпадающих с временными промежутками, на которых междуфазные напряжения сети изменяются в пределах от 0,86 до 1 по отношению к амплитудному значению, в соответствии с логическим уравнением , где - вектор логических сигналов управления транзисторными ключами с указанием в виде индексов места присоединения ключа к горизонтальным и вертикальным шинам матричного преобразователя; - модуляционная матрица, образованная сигналами синхронизирующих импульсов; - вектор модулированных по ширине первичных управляющих импульсов.

2. Способ управления по п.1, отличающийся тем, что в нижней части диапазона регулирования синхронизирующие сигналы вырабатывают таким образом, чтобы они совпадали с промежутками времени, на которых междуфазные напряжения сети изменялись в пределах от 0,5 до 0,86 своего амплитудного значения, соответственно этому, формирование опорного сигнала осуществляют непрерывным интегрированием указанного напряжения.