Устройство для мажоритарного выбора сигналов

Иллюстрации

Показать всеИзобретение относится к области автоматики и вычислительной техники и может быть использовано при построении высоконадежных резервированных устройств и систем с возможностью обеспечения синхронной работы всех резервных каналов. Техническим результатом изобретения является повышение надежности функционирования за счет исключения сбоев в устройстве. Технический результат достигается благодаря тому, что устройство для мажоритарного выбора сигналов содержит n каналов, в каждый из которых включены реверсивный счетчик, мажоритарный элемент, D-триггеры, генератор, элементы И и И-НЕ. Устройство исключает возможность "противоборства" фронтов входных импульсов разных каналов, которое может возникать из-за отсутствия синхронизации входных импульсов. Это "противоборство" может приводить к сбою устройства и, как следствие, к потере работоспособности. Устройство повышает надежность функционирования за счет исключения сбоев. 1 ил.

Реферат

Предлагаемое изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении высоконадежных резервированных устройств и систем, например резервированных систем для обработки числоимпульсных кодов с возможностью обеспечения синхронной работы всех резервных каналов.

Известно устройство для мажоритарного выбора сигналов [1], содержащее резервируемые блоки, мажоритарный элемент, в каждом канале реверсивный счетчик, элементы ИЛИ, элементы И, элементы И-НЕ, инверторы, элемент сравнения, элемент задержки.

Недостаток этого устройства состоит в сложности реализации и низкой надежности.

Наиболее близким решением к предлагаемому является устройство для мажоритарного выбора сигналов [2], содержащее n каналов, каждый из которых включает m-разрядный реверсивный счетчик, первый и второй элементы И, первый и второй элементы И-НЕ, подключенные своими выходами к первым входам соответственно первого и второго элементов И, выходы которых соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика, первые входы первого и второго элементов И-НЕ соединены с прямым и инверсным выходами (m-1)-го разряда реверсивного счетчика, а вторые входы этих элементов И-НЕ соединены соответственно с инверсным и прямым выходом m-го разряда реверсивного счетчика, соединенного своим выходом с первым входом мажоритарного элемента и соответствующими входами мажоритарного элемента других каналов.

Недостаток известного решения [2] состоит в том, что входные импульсные последовательности не синхронизированы между собой, поэтому импульс, поступающий с выхода мажоритарного элемента на суммирующий вход реверсивного счетчика, может совпасть с входным импульсом одной из последовательностей, поступающим на вычитающий вход реверсивного счетчика. В результате возможного "противоборства" фронтов может произойти сбой в работе известного устройства (непредусмотренное изменение кодового состояния реверсивного счетчика). Кроме того, если в результате "противоборства" будет потерян импульс с выхода мажоритарного элемента, известное устройство может сформировать лишний выходной импульс, что соответствует сбою известного устройства.

Задача изобретения - повышение надежности функционирования за счет исключения сбоев устройства.

Эта задача достигается тем, что в устройство для мажоритарного выбора сигналов, содержащее n каналов, каждый из которых включает m-разрядный реверсивный счетчик, первый и второй элементы И, первый и второй элементы И-НЕ, подключенные своими выходами к первым входам соответственно первого и второго элементов И, выходы которых соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика, первые входы первого и второго элементов И-НЕ соединены с прямым и инверсным выходами (m-1)-го разряда реверсивного счетчика, а вторые входы этих элементов И-НЕ соединены соответственно с инверсным и прямым выходом m-го разряда реверсивного счетчика, соединенного своим выходом с первым входом мажоритарного элемента и соответствующими входами мажоритарного элемента других каналов, в каждый канал дополнительно введены первый D-триггер, генератор и последовательно соединенные второй, третий, четвертый и пятый D-триггеры, при этом второй вход второго элемента И соединен с выходом первого D-триггера, вход D которого подключен к входной шине, а вход С первого D-триггера соединен с прямым выходом генератора и входом С четвертого D-триггера, инверсный выход генератора соединен с входом С третьего и пятого D-триггера, выход которого подключен к входу R второго D-триггера, вход D которого соединен с его высокопотенциальной шиной питания, вход С подключен к выходу мажоритарного элемента, а выход второго D-триггера соединен с выходной шиной канала, выход третьего D-триггера соединен с вторым входом первого элемента И.

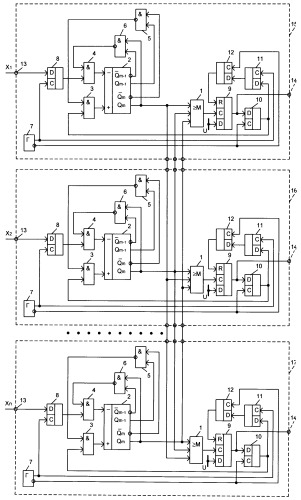

На чертеже приведена блок-схема устройства для мажоритарного выбора сигналов. На этой схеме 1 - мажоритарный элемент, 2 - реверсивный счетчик, 3 и 4 - первый и второй элементы И соответственно, 5 и 6 - первый и второй элементы И-НЕ соответственно, 7 - генератор, 8, 9, 10, 11 и 12 - первый, второй, третий, четвертый и пятый D-триггеры соответственно, 13 - входная шина, 14 - выходная шина, 15 - первый канал, 16 - второй канал, 17 - n-й канал.

Выходы первого 5 и второго 6 элементов И-НЕ подключены к первым входам соответственно первого 3 и второго 4 элементов И, выходы которых соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика 2. Первые входы первого 5 и второго 6 элементов И-НЕ соединены с прямым и инверсным выходами (m-1)-го разряда реверсивного счетчика 2, а вторые входы этих элементов И-НЕ соединены соответственно с инверсным и прямым выходом m-го разряда реверсивного счетчика 2. Выход реверсивного счетчика 2 соединен с первым входом мажоритарного элемента 1 и соответствующими входами мажоритарного элемента других каналов. Последовательно соединены второй 9, третий 10, четвертый 11 и пятый 12 D-триггеры, второй вход второго элемента И 4 соединен с выходом первого D-триггера 8, вход D которого подключен к входной шине 13, а вход С первого D-триггера 8 соединен с прямым выходом генератора 7 и входом С четвертого D-триггера 11, инверсный выход генератора 7 соединен с входом С третьего 10 и пятого 12 D-триггера, выход которого подключен к входу R второго D-триггера 9, вход D которого соединен с его высокопотенциальной шиной питания U, вход С второго D-триггера 9 подключен к выходу мажоритарного элемента 1, а выход второго D-триггера 9 соединен с выходной шиной канала 14, выход третьего D-триггера 10 соединен с вторым входом первого элемента И 3.

Устройство для мажоритарного выбора сигналов работает следующим образом. Входные сигналы X1, X2, ХП поступают на входы 13 (входы D первого D-триггера 8) соответствующих каналов устройства. Для наглядности примем, что n=3 и все реверсивные счетчики находятся в нулевом состоянии, а логической единице соответствует высокий уровень сигнала. В этом случае нулевые уровни с прямых выходов (m-1)-го и m-го разрядов реверсивного счетчика 2 поступают на первый вход первого элемента И-НЕ 5 и второй вход второго элемента И-НЕ 6 соответственно. В результате на их выходах будет высокий уровень, который и поступит на первые входы первого 3 и второго 4 элементов И. Входной импульс, например X1, появляется на выходе D-триггера 8 по переднему фронту импульса с прямого выхода генератора 7 (период следования импульсов ТГ генератора 7 выбирается меньше длительности ТИ входного импульса X1). Импульс с выхода D-триггера 8 поступает на второй вход второго элемента И 4 и формирует на его выходе высокий уровень, который, поступая на вычитающий вход реверсивного счетчика 2, переводит его в состояние "минус единица" (во всех разрядах единицы). В результате высокий уровень с его прямого выхода старшего разряда m поступит на первый вход мажоритарного устройства 1 первого канала 15 и соответствующие входы остальных каналов. Нулевые уровни с инверсных выходов (m-1)-го и m-го разрядов реверсивного счетчика 2 поступят на первый вход первого элемента И-НЕ 5 и второй вход второго элемента И-НЕ 6, в результате чего на их выходах останется высокий уровень. После того как на любой другой вход устройства, например на второй, поступит импульс X2, он также будет воспринят реверсивным счетчиков второго канала 16. В результате высокий уровень с прямого выхода его старшего разряда попадает на вход мажоритарного устройства 1 своего канала и соответствующие входы мажоритарного устройства других каналов. При наличии двух высоких уровней на входах мажоритарного элемента 1 всех каналов на его выходе появится высокий уровень, который поступает на вход С второго D-триггера 9 всех каналов. На входе D этого триггера постоянно присутствует высокий уровень U, в результате чего D-триггер 9 устанавливается в единичное состояние по переднему фронту выходного импульса мажоритарного элемента 1. Выходной сигнал второго D-триггера 9 всех каналов поступает на выходную шину 14 и вход D третьего D-триггера 10. Далее последовательно будут устанавливаться в единичное состояние третий D-триггер 10 по переднему фронту импульса с инверсного выхода генератора 7, четвертый D-триггер 11 по переднему фронту импульса с прямого выхода генератора 7, пятый D-триггер 12 по переднему фронту импульса с инверсного выхода генератора 7. Выходной импульс третьего D-триггера 10 всех каналов поступает на второй вход первого элемента И 3 и формирует на его выходе высокий уровень, который поступает на суммирующий вход реверсивного счетчика 2. В результате состояние всех реверсивных счетчиков увеличится на единицу - реверсивный счетчик 2 первого канала 15 и реверсивный счетчик 2 второго канала 16 будут обнулены, а реверсивный счетчик 2 третьего канала 17 перейдет в состояние "+1" (единица в младшем разряде). Если далее на вход третьего канала 17 поступит импульс Х3, то в соответствии с приведенным описанием этот импульс проходит на вычитающий вход реверсивного счетчика 2 своего канала и переводит реверсивный счетчик 2 третьего канала 17 в нулевое состояние.

После установки пятого D-триггера 12 в единичное состояние его выходной сигнал устанавливает второй D-триггер 9 в нулевое состояние, после чего происходит последовательная установка в нулевое состояние третьего 10, четвертого 11 и пятого 12 D-триггеров и схема приходит в исходное состояние.

Таким образом, устройство выбирает среднюю по числу импульсов последовательность и все выходные сигналы устройства формируются синхронно.

Оценим устойчивость к сбоям предлагаемого и известного [2] устройства. Как следует из приведенного описания устройства для мажоритарного выбора сигналов, вычитание импульсов реверсивным счетчиком 2 производится по переднему фронту импульса с прямого выхода генератора 7, суммирование импульсов производится по переднему фронту импульса с инверсного выхода генератора 7. Это означает, что совпадение моментов суммирования и вычитания импульсов в предлагаемой схеме невозможно, а значит, невозможно "противоборство" фронтов входного импульса на вычитающем входе и импульса с выхода третьего D-триггера 10 на суммирующем входе реверсивного счетчика 2.

В известном [2] устройстве возможно совпадение фронтов входного импульса на вычитающем входе и импульса с выхода мажоритарного элемента на суммирующем входе реверсивного счетчика. Такое совпадение приводит к сбою устройства. Оценим частоту такого события. Пусть период T1 входных импульсов X1 первого канала отличается от периода Т2 входных импульсов Х2 второго канала на величину ΔТ. Число периодов n, по истечении которых входные импульсы совпадут, будет равно

Время t, по истечении которого будет повторяться совпадение входных импульсов X1 и Х2, можно определить в виде

Частоту f появления сбоев можно определить в виде

Если, например, T1=10 мс, ΔT=10-2 мс, то f=0,1 с-1. Иначе говоря, через каждые 10 секунд возможен сбой устройства, который сопровождается потерей либо прохождением лишнего импульса. В течение некоторого времени число этих сбоев станет недопустимым, и это состояние рассматривается как отказ устройства.

В предлагаемом устройстве для мажоритарного выбора сигналов такие сбои исключены, что повышает надежность функционирования устройства.

Предлагаемая совокупность признаков в рассмотренных авторами решениях не встречалась для решения поставленной задачи и не следует явным образом из уровня техники, что позволяет сделать вывод о соответствии технического решения критериям "новизна" и "изобретательский уровень". В качестве элементов для реализации устройства можно использовать стандартные элементы: реверсивные счетчики, логические микросхемы, мажоритарные элементы, триггеры, генераторы.

Литература

1. Авторское свидетельство СССР №1215113, кл. G06F 11/18, Устройство для мажоритарного выбора асинхронных сигналов.

2. Патент Российской Федерации № 2110835, кл. G06F 11/18, Н05К 10/00, Устройство для мажоритарного выбора сигналов.

Устройство для мажоритарного выбора сигналов, содержащее n каналов, каждый из которых включает m-разрядный реверсивный счетчик, первый и второй элементы И, первый и второй элементы И-НЕ, подключенные своими выходами к первым входам соответственно первого и второго элементов И, выходы которых соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика, первые входы первого и второго элементов И-НЕ соединены с прямым и инверсным выходами (m-1)-го разряда реверсивного счетчика, а вторые входы этих элементов И-НЕ соединены соответственно с инверсным и прямым выходом m-го разряда реверсивного счетчика, соединенного своим выходом с первым входом мажоритарного элемента и соответствующими входами мажоритарного элемента других каналов, отличающееся тем, что в каждый канал дополнительно введены первый D-триггер, генератор и последовательно соединенные второй, третий, четвертый и пятый D-триггеры, при этом второй вход второго элемента И соединен с выходом первого D-триггера, вход D которого подключен к входной шине, а вход С первого D-триггера соединен с прямым выходом генератора и входом С четвертого D-триггера, инверсный выход генератора соединен с входом С третьего и пятого D-триггера, выход которого подключен к входу R второго D-триггера, вход D которого соединен с его высокопотенциальной шиной питания, вход С подключен к выходу мажоритарного элемента, а выход второго D-триггера соединен с выходной шиной канала, выход третьего D-триггера соединен с вторым входом первого элемента И.