Аналоговый перемножитель напряжений

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в фазовых детекторах и модуляторах, а также в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Технический результат заключается во введении новых связей, что позволяет снижать напряжение питания АПН до уровня ±(1÷1,5 В) при одновременном упрощении схемы, и в расширении полосы пропускания АПН путем повышения симметрии каналов передачи напряжения ux, повышении мощности перемножения сигналов ux и uy на высоких частотах. Заявленное устройство содержит первый источник первого перемножаемого напряжения ux, второй источник первого перемножаемого напряжения ux, противофазный первому источнику, первый и второй противофазные источники второго перемножаемого напряжения uy, первый, второй, третий и четвертый входные транзисторы, первый и второй токостабилизирующие двухполюсники, первый элемент нагрузки, включены новые связи - база второго входного транзистора соединена с первым источником второго перемножаемого напряжения uy, база четвертого входного транзистра соединена со вторым источником второго перемножаемого напряжения uy, причем между эмиттером первого входного транзистора и шиной источника питания включен по переменному току первый дополнительный конденсатор, а между эмиттером третьего входного транзистора и шиной источника питания включен по переменному току второй дополнительный конденсатор. 1 з.п. ф-лы, 10 ил.

Реферат

Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в фазовых детекторах и модуляторах, а также в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Аналоговый перемножитель является базовым узлом современных систем приема и обработки сигналов ВЧ и СВЧ-диапазонов, аналоговой вычислительной и измерительной техники.

В настоящее время в аналоговой микросхемотехнике в составе перемножителей двух напряжений, систем электронной регулировки усиления широкое применение находит так называемая перемножающаяся ячейка Джильберта (фиг.1). Такая структура стала основой построения практически всех известных в настоящее время прецизионных аналоговых перемножителей сигналов на основе дифференциальных каскадов [1-36]. В этой связи задача улучшения параметров этого функционального узла относится к числу достаточно актуальных задач современной микроэлектроники.

В цифровых интегральных микросхемах результатом увеличения скорости обработки информации стали тенденции постоянного уменьшения напряжения питания, что является «анафемой» в аналоговом проектировании с высокими характеристиками. При технологических нормах 350 нм (напряжение питания 3.3 В) по-прежнему достаточно схемотехнических возможностей для аналоговых проектирований с высокими характеристиками, хотя наличие 5 В питания было бы предпочтительнее. При нормах 180 нм (1.8 В) процесс усложняется и статические характеристики аналоговых устройств страдают. При 90÷130 нм технологии необходимо развитие новых подходов к проектированию микросхем, ориентированных на обеспечение работоспособности при низковольтном питании.

В рамках собственных программ развития ряд ведущих микроэлектронных фирм, в т.ч. российских, начинают использовать технологическое оборудование для 0,25 мкм SiGe-технологии SGB25VD, способное в рамках единого цикла изготовить высококачественные гетеропереходы. Это позволяет реализовать субмикронные транзисторы X диапазона, а также использовать экономичные режимы для СВЧ интегральных схем относительно высокого уровня интеграции. Однако технология SGB25VD накладывает дополнительные и существенные для схемотехники аналоговых микросхем ограничения, выражающиеся в невозможности использования комплементарных транзисторов и относительно низковольтных режимов их работы (Uкэ.max=2,9÷3,0 В). Создание IP блоков для SiGe технологии SGB25VD является (наряду с ее освоением) важнейшей задачей для зарубежных и отечественных центров проектирования аналоговых микросхем.

Таким образом, последние несколько лет источники питания с напряжением 5 В вытесняются более низковольтными. Требования к уменьшению рассеиваемой мощности и уменьшению числа батарей в таких приложениях, как беспроводные устройства связи и персональные компьютеры, привели к снижению напряжения питания в цифровых схемах до уровня 1,5 В. Эта тенденция, как отмечалось выше, реализована в современных SiGe транзисторах, которые сконструированы так, чтобы обеспечить максимальную частоту среза (f1) в компромиссе с напряжением пробоя (Uпp). Для кремниевых транзисторов существует следующее фундаментальное ограничение: f1×Uпр≈const, т.е. малые размеры транзисторов, обеспечивающие высокие значения f1 (до 200 ГГц), привели к снижению напряжения питания микросхем до 1,2÷1,5 В.

Уменьшение напряжения питания (Еп) в биполярных схемах приводит к появлению новых проблем, и некоторые из них становятся особенно важными при напряжении питания менее 2 В. Принципиальная сложность уменьшения напряжения Еп состоит в том, что биполярный транзистор имеет фиксированное напряжение база-эмиттер Uбэ, которое не уменьшается линейно с уменьшением технологических норм, так как

,

где φт=kT/q, Iк - ток коллектора и Is - обратный ток эмиттерного р-n перехода. При этом параметры транзистора и уровни тока оказывают слабое влияние на напряжение Uбэ. На практике плотность тока в биполярном транзисторе (Iк/Is), изменяя свое значение, также слабо влияет на напряжение Uбэ. Если в используемой технологии Uбэ≈0,7 В, то использование 1,5 В источника питания приводит к тому, что между «землей» и шиной Еп не может быть включено больше чем один р-n переход.

Учитывая вышесказанное, а также численные значения напряжения Uбэ≈700 мВ, можно сделать вывод о том, что при напряжении питания меньше чем 1,5 В запрещается использовать многоярусные дифференциальные пары или каскодные конфигурации (архитектуры).

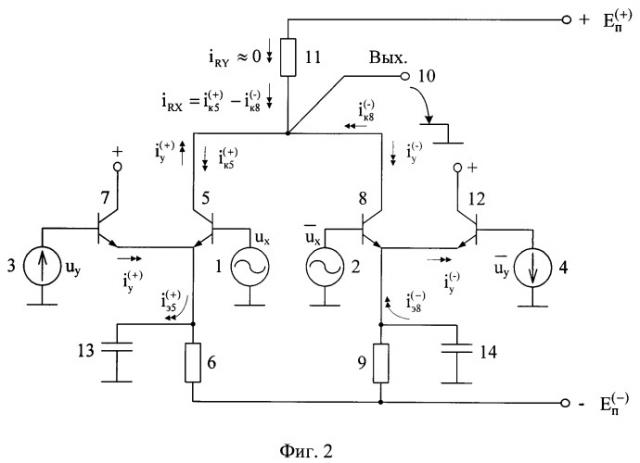

Ближайшим прототипом заявляемого устройства является аналоговый перемножитель напряжений (АПН, фиг.1), рассмотренный в патентной заявке фирмы Sharp US №2006/0066362, fig. 15, содержащий первый 1 источник первого перемножаемого напряжения ux, второй 2 источник первого перемножаемого напряжения ux, противофазный первому 1 источнику, первый 3 и второй 4 противофазные источники второго перемножаемого напряжения uy, первый 5 входной транзистор, база которого подключена к первому 1 источнику первого перемножаемого напряжения ux, эмиттер соединен с первым 6 токостабилизирующим двухполюсником, второй 7 входной транзистор, эмиттер которого соединен с эмиттером первого 5 входного транзистора, третий 8 входной транзистор, база которого подключена ко второму 2 источнику первого перемножаемого напряжения ux, эмиттер соединен со вторым 9 токостабилизирующим двухполюсником, а коллектор подключен к коллектору первого 5 входного транзистора, первому 1 выходу аналогового перемножителя напряжения и первому 11 элементу нагрузки, четвертый 12 входной транзистор, эмиттер которого соединен с эмиттером третьего 8 входного транзистора.

Существенный недостаток известного АПН состоит в том, что для его реализации необходимы два управляемых напряжениями ux(3) и (4) транзисторных управляемых источника токов 6 и 9, которые (при их традиционном построении) «съедают» 1,4÷1,5 В напряжения питания . Как следствие, известный АПН не может работать при низковольтном питании ±(1÷1,5 В).

Недостаток известного перемножителя напряжений (фиг.1) состоит также в том, что он характеризуется многоканальной передачей перемножаемого сигнала ux к выходному узлу 10 АПН. Многоканальный характер передачи напряжения ux создает проблему обеспечения широкополосности и быстродействия АПН. Это обусловлено разной инерционностью каналов передачи ux, а также фазовыми характеристиками каналов. Например, прямая паразитная неинвертирующая передача сигнала от источника 2 к выходу 10 через емкость коллектор-база Ск8 транзистора 8 увеличивается с повышением частоты. С другой стороны, неинвертирующая передача сигнала ux (источник 1) к выходу 10 через транзисторы 12 и 8 уменьшается с повышением частоты, так как этот канал шунтируется паразитной емкостью на подложку С9 транзисторов, образующих управляемый двухполюсник 9.

Следует заметить, что фазы выходных сигналов по паразитным каналам не совпадают, что создает проблему их согласования, а также ухудшает погрешность перемножения на высоких частотах.

Основная цель предлагаемого изобретения - снижение напряжения питания АПН до уровня ±(1÷1,5 В) при одновременном упрощении схемы.

Дополнительная цель состоит в расширении полосы пропускания АПН путем повышения симметрии каналов передачи напряжения ux, повышении точности перемножения сигналов ux и uy на высоких частотах.

Поставленная цель достигается тем, что в АПН, содержащем первый 1 источник первого перемножаемого напряжения ux, второй 2 источник первого перемножаемого напряжения ux, противофазный первому 1 источнику, первый 3 и второй 4 противофазные источники второго перемножаемого напряжения uy, первый 5 входной транзистор, база которого подключена к первому 1 источнику первого перемножаемого напряжения ux, эмиттер соединен с первым 6 токостабилизирующим двухполюсником, второй 7 входной транзистор, эмиттер которого соединен с эмиттером первого 5 входного транзистора, третий 8 входной транзистор, база которого подключена ко второму 2 источнику первого перемножаемого напряжения ux, эмиттер соединен со вторым 9 токостабилизирующим двухполюсником, а коллектор подключен к коллектору первого 5 входного транзистора, первому 1 выходу аналогового перемножителя напряжения и первому 11 элементу нагрузки, четвертый 12 входной транзистор, эмиттер которого соединен с эмиттером третьего 8 входного транзистора, предусмотрены новые элементы и связи - база второго 7 входного транзистора соединена с первым 3 источником второго перемножаемого напряжения uy, база четвертого 12 входного транзистора соединена со вторым 4 источником второго перемножаемого напряжения uy, причем между эмиттером первого 5 входного транзистора и шиной источника питания включен по переменному току первый 13 дополнительный конденсатор, а между эмиттером третьего 8 входного транзистора и шиной источника питания включен по переменному току второй 14 дополнительный конденсатор.

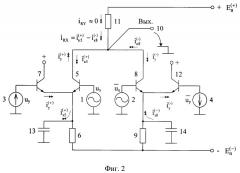

На фиг.1 показана схема АПН-прототипа, а на фиг.2 - схема заявляемого АПН в соответствии с п.1 формулы изобретения.

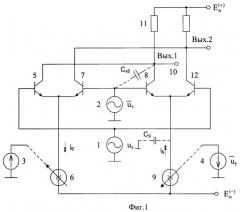

На фиг.3 представлена схема АПН в соответствии с п.2 формулы изобретения.

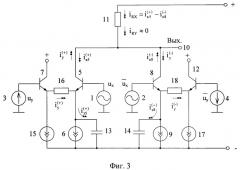

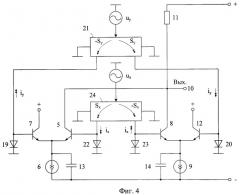

На фиг.4 показан частный вариант АПН с расширенным диапазоном линейного перемножения сигналов ux и uy, основанный на использовании логарифмирующих р-n переходов и преобразователей «напряжение-ток» 21 и 24.

Схема на фиг.5 иллюстрирует способ получения двух противофазных напряжений ux и на базе высокочастотного трансформатора. Возможны и другие способы формирования ux и .

На фиг.6 приведена схема АПН (фиг.2) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП HПП "Пульсар», а на фиг.7 показана зависимость коэффициента усиления по напряжению Ku=uвых/ux АПН (фиг.2) от уровня напряжения Uy на входах канала «У» (V7, V10) в частотном диапазоне. Такой режим измерения Ku характеризует применение заявляемого АПН в качестве управляемого усилителя.

Фиг.8 иллюстрирует зависимость модуля Ku=f(Uy) в диапазоне средних частот АПН (фиг.6).

На фиг.9 показаны результаты моделирования заявляемого АПН (фиг.6) в режиме смесителя двух сигналов для случая, когда на вход «X» (V8, V9) подается частота 10 МГц, а на вход «У» (V7, V10) - 1 МГц. На фиг.10 представлены результаты компьютерного моделирования переходных процессов смесителя (фиг.6) для тех же сигналов.

Заявляемый АПН (фиг.2) содержит первый 1 источник первого перемножаемого напряжения ux, второй 2 источник первого перемножаемого напряжения ux, противофазный первому 1 источнику, первый 3 и второй 4 противофазные источники второго перемножаемого напряжения uy, первый 5 входной транзистор, база которого подключена к первому 1 источнику первого перемножаемого напряжения ux, эмиттер соединен с первым 6 токостабилизирующим двухполюсником, второй 7 входной транзистор, эмиттер которого соединен с эмиттером первого 5 входного транзистора, третий 8 входной транзистор, база которого подключена ко второму 2 источнику первого перемножаемого напряжения ux, эмиттер соединен со вторым 9 токостабилизирующим двухполюсником, а коллектор подключен к коллектору первого 5 входного транзистора, первому 1 выходу аналогового перемножителя напряжения и первому 11 элементу нагрузки, четвертый 12 входной транзистор, эмиттер которого соединен с эмиттером третьего 8 входного транзистора. База второго 7 входного транзистора соединена с первым 3 источником второго перемножаемого напряжения uy, база четвертого 12 входного транзистора соединена со вторым 4 источником второго перемножаемого напряжения uy, причем между эмиттером первого 5 входного транзистора и шиной источника питания включен по переменному току первый 13 дополнительный конденсатор, а между эмиттером третьего 8 входного транзистора и шиной источника питания включен по переменному току второй 14 дополнительный конденсатор.

В схеме на фиг.3 в соответствии с п.2 формулы изобретения эмиттер второго 7 входного транзистора связан с первым 15 вспомогательным двухполюсником и через первый 16 дополнительный резистор соединен с эмиттером первого 5 входного транзистора, эмиттер четвертого 12 входного транзистора связан со вторым 17 вспомогательным двухполюсником и через второй 18 дополнительный резистор соединен с эмиттером третьего 8 входного транзистора. Это расширяет диапазон линейной работы канала «Y».

В схеме на фиг.4 противофазные источники 1-2 и 3-4 (фиг.3) реализованы на основе р-n переходов 19, 20 и преобразователе «напряжение-ток» 21 (канал «Y»), а также р-n переходов 22, 23 и преобразователе «напряжение-ток» 24 (канал «X»). В качестве преобразователей 21 и 24 могут использоваться классические дифференциальные каскады.

В схеме на фиг.5 для получения противофазных напряжений канала «X» ux и используется высокочастотный трансформатор 25 со средней точкой.

Рассмотрим работу заявляемого АПН (фиг.2).

В статическом режиме, когда напряжение управления равно нулю (uy=0), эмиттерные и коллекторные токи транзисторов схемы на фиг.2 устанавливаются двухполюсниками 6 и 9. При этом

где Iкi - коллекторные токи транзисторов 5, 7, 8, 12.

I6, I9 - токи двухполюсников 6 и 9.

Емкость конденсатов 13, 14 (C13=C14) выбирается такой, чтобы во всем частотном диапазоне ωх сигнала ux выполнялось неравенство

где ωх - частота сигнала по каналу «X»;

rэ7 - сопротивление эмиттерного перехода транзистора 7;

φт≈26 мВ - температурный потенциал.

Поэтому коэффициент усиления по напряжению от источника 1:

где Rн.экв - эквивалентное сопротивление нагрузки 11 (Rн.экв≈R11).

Если напряжения uy увеличиваются, то это приводит к появлению приращений токов и . Приращение передается на выход 10 через транзистор 5, а с другой стороны поступает в нагрузку 11 в противофазе через транзисторы 12 и 8. Если во всем диапазоне частот ωy сигнала uy выполняется неравенство

то все приращение практически без потерь поступает в цепь нагрузки 10 и компенсирует составляющую коллекторного тока . В результате на выходе 10 обеспечивается полное подавление сигнала управления Uy. Как следствие, уровень постоянной составляющей выходного напряжения АПН не изменяется, что позволяет применять непосредственную связь между каскадами, связанными с дальнейшей обработкой сигналов перемножения.

В схеме на фиг.2 при увеличении uy коэффициент усиления по напряжению каскада на транзисторах 7 и 5 уменьшается

а каскада на транзисторах 8 и 12 увеличивается

где Rн.экв - эквивалентное сопротивление нагрузки 11;

rэi - сопротивление эмиттерного перехода i-го транзистора.

Поэтому переменное выходное напряжение АПН пропорционально произведению ux и uy (при их изменении в небольших пределах):

Следует заметить, что в схеме на фиг.2 каналы передачи напряжения ux от источников сигналов 1 и 2 идентичны, что расширяет полосу пропускания АПН по выходу 10 (особенно при малых величинах uy, ux).

Замечательная особенность схемы на фиг.2 - подавление передачи сигнала uy на выход 10. Действительно, при изменении токов и коллекторные токи транзисторов 5 и 8 изменяются относительно нагрузки 11 противофазно, что стабилизирует статическое напряжение на резисторе 11.

Кроме этого в АПН (фиг.3, фиг.4) обеспечивается взаимная компенсация влияния емкостей коллекторных переходов транзисторов 5 и 8 на работу схемы, что снижает погрешность перемножения ux и uy в диапазоне высоких частот.

Для существенного расширения динамического диапазона перемножаемых сигналов ux и uy следует использовать их предварительное логарифмирование (фиг.4).

Представленные на фиг.7 и фиг.8 графики показывают, что в режиме управляемого усилителя Ku заявляемого АПН при выбранных сопротивлениях резисторов нагрузки изменяется в диапазоне 0÷70.

Рассмотрим факторы, ограничивающие уровень напряжения питания в АПН-прототипе (фиг.1).

Величина положительного напряжения источника питания зависит от статического падения напряжения на резисторе нагрузки R11, а также необходимого диапазона изменения выходного напряжения Uвых.max:

где I0 - статический ток через резистор нагрузки 11.

С другой стороны, для исключения насыщения транзисторов 5, 7, 8, 12 при изменении uвых необходимо обеспечить

Таким образом, из (4) и (5) следует, что минимально возможное напряжение питания АПН (фиг.1) находится из уравнения:

Следовательно, при малых Uвых.max АПН (фиг.1) обеспечивает устойчивую работу при .

Однако из-за двухъярусной структуры АПН (фиг.1) не может работать при малых напряжениях . В этой схеме отрицательное напряжение питания должно быть больше чем

где Uэб.5≈0,7 В - напряжение на переходе эмиттер-база транзистора 5, (7, 8, 12);

U6≈0,7 В - минимально возможное напряжение на двухполюснике 6 (при его классическом построении на базе токовых зеркал U6≈0,7 В).

Из (7) следует, что АПН-прототип требует отрицательного напряжения питания не менее чем .

Рассмотрим далее ограничения на в заявляемом АПН.

Величина напряжения положительного источника питания определяется так же, как и АПН-прототипе формулой (4).

Минимальное напряжение отрицательного источника питания АПН (фиг.2) находится с учетом второго закона Кирхгофа из решения следующей системы неравенств, полученных при малых величинах ux и uy:

где Uэб.7=Uэб.8≈0,7 В - напряжение эмиттер-база транзисторов 7 и 8;

U6min=U9min=0,1÷0,3 В - минимально допустимое напряжение на резисторах 6 и 9, при котором обеспечивается заданная стабильность статистического режима транзисторов.

Результаты эксперимента подтверждают работоспособность заявляемого АПН при .

Применение заявляемого АПН качестве управляемого усилителя (фиг.6) показывает (фиг.8), что в таком включении АПН обеспечивается достаточно линейная характеристика управления Ku=f(Uy), где Uy - напряжение на входе «Y» схемы (фиг.6) (V7, V10).

Предлагаемый АПН может эффективно использоваться в качестве «миксера» двух сигналов (фиг.6). Переходный процесс в АПН (фиг.6) при смешении сигналов с частотами fx=10 МГц и fy=1 МГц приведен на фиг.9. График на фиг.9 характеризует спектр выходного напряжения смесителя (фиг.6). Из этого графика следует, что основная гармоника на выходе существенно подавляется.

Свойства заявляемого АПН в режиме перемножения двух напряжений (фиг.10) показывают, что предлагаемое техническое решение может использоваться в качестве модулятора.

При использовании двух схем АПН (фиг.2) возможно построение перемножителей с дифференциальным выходом.

Таким образом, предлагаемая схема АПН имеет более низкие значения напряжений питания, что позволяет использовать для ее построения более высокочастотные SiGe транзисторы и расширить при этом диапазон рабочих частот.

Предлагаемое техническое решение является альтернативой широко распространенной перемножающей ячейки Джильберта [1-36] и характеризуется более высокими качественными параметрами.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент GB 2.318.470, H03f 3/45

2. Патент ЕР 1.369.992

3. Патент США №5.874.857

4. Патент США №6.456.142, фиг.8

5. Патент США №3.931.583, фиг.9

6. Патентная заявка США №2007/0139114, фиг.1

7. Патентная заявка США №2005/0073362, фиг.1

8. Патент США №5.057.787

9. Патентная заявка WO 2004/041298

10. Патент США №5.389.840, фиг.1А

11. Патент США №5.883.539, фиг.1

12. Патентная заявка США №2005/0052239

13. Патент США №5.151.625, фиг.1

14. Патент США №4.458.211, фиг.5

15. Патентная заявка США №2005/0030096, фиг.6

16. Патентная заявка США №2007/0090876

17. Патент США №6.727.755

18. Патент США №5.552.734, фиг.13, фиг.16

19. Патентная заявка США №2006/0232334

20. Патент США №5.767.727

21. Патент США №6.229.395, фиг.2

22. Патент США №5.115.409

23. Патентная заявка США №2005/0231283, фиг.1

24. Патентная заявка США №2006/0066362, фиг.15

25. Патент США №5.151.624, фиг.1, фиг.2

26. Патент США №5.329.189, фиг.2

27. Патент США №4.704.738

28. Патент США №4.480.337

29. Патент США №5.825.231

30. Патент США №6.211.718, фиг.1, фиг.2

31. Патент США №5.151.624

32. Патент США №5.329.189

33. Патент США №5.331.289

34. Патент GB №2.323.728

35. Патентная заявка США №2008/0122540, фиг.1

36. Патент США №4.965.528

1. Аналоговый перемножитель напряжений ux и uy, содержащий первый (1) источник первого перемножаемого напряжения ux, второй (2) источник первого перемножаемого напряжения ux, противофазный первому (1) источнику, первый (3) и второй (4) противофазные источники второго перемножаемого напряжения uy, первый (5) входной транзистор, база которого подключена к первому (1) источнику первого перемножаемого напряжения ux, эмиттер соединен с первым (6) токостабилизирующим двухполюсником, второй (7) входной транзистор, эмиттер которого соединен с эмиттером первого (5) входного транзистора, третий (8) входной транзистор, база которого подключена ко второму (2) источнику первого перемножаемого напряжения ux, эмиттер соединен со вторым (9) токостабилизирующим двухполюсником, а коллектор подключен к коллектору первого (5) входного транзистора, первому (1) выходу аналогового перемножителя напряжения и первому (11) элементу нагрузки, четвертый (12) входной транзистор, эмиттер которого соединен с эмиттером третьего (8) входного транзистора, отличающийся тем, что база второго (7) входного транзистора соединена с первым (3) источником второго перемножаемого напряжения uy, база четвертого (12) входного транзистора соединена со вторым (4) источником второго перемножаемого напряжения uy, причем между эмиттером первого (5) входного транзистора и шиной источника питания включен по переменному току первый (13) дополнительный конденсатор, а между эмиттером третьего (8) входного транзистора и шиной источника питания включен по переменному току второй (14) дополнительный конденсатор.

2. Устройство по п.1, отличающееся тем, что эмиттер второго (7) входного транзистора связан с первым (15) вспомогательным двухполюсником и через первый (16) дополнительный резистор соединен с эмиттером первого (5) входного транзистора, эмиттер четвертого (12) входного транзистора связан со вторым (17) вспомогательным двухполюсником и через второй (18) дополнительный резистор соединен с эмиттером третьего (8) входного транзистора.