Устройство для вычисления квадратного корня

Иллюстрации

Показать всеРеферат

О П И C А Н И Е 239665

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства ¹

Заявлено 27.1.1966 (№ 1051261/18-24) с присоединением заявки №

ПриОритет

Опубликовано 1969. Бюллетень № 11

Дата опубликования описания 14ХП1.1969

Кл 42гпз, 7! 38

МПК G 06E

УДК 681.325.59 (088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Автор изобретения

В. В. Алексейчик

Заявитель

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КВАДРАТНОГО КОРНЯ

Изобретение относится к области цифровой вычислительной техники.

Известны устройства для вычисления квадратного корня, содержащие регистры, сумматор и счетчик циклов. Недостатком известных устройств является их громоздкость.

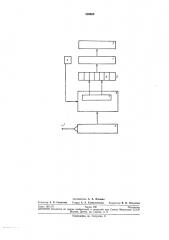

Предлагаемое устройство отличается тем, что оно содержит дешифратор со схемами объединения на выходе, входы которого подключены к выходам счетчика цикла и к выходу триггера знакового разряда сумматора, выходы дешифратора через схемы объединения подсоединены к соответствующим разрядам регистра, выходы регистра сдвига соединены со входами сумматора.

Это позволяет упростить устройство.

На чертеже показана схема устройства.

В сумматоре 1 хранится подкоренное выражение, в регистре 2 формируется переменный код, в регистре 8 накапливается результат вычисления квадратного корня.

Счетчик циклов 4 с дешифратором 5 используется для записи кодов 101 или 011 в зависимости от знака сумматора 6 с помощью схем объединения 7 в триггеры 8.

Перед началом вычисления подкоренное выражение находится в сумматоре 1. Выполнение операции,в описываемой схеме сводится к формированию переменного кода в регистре 2 путем записи кодов 101 или 011 в триггеры 8 по следующему правилу: если знак сумматора 6 положителен, то в разряды (2i — 3), (2с — 2), (2i — 1) записывается код

101 соответственно; если знак сумматора 6 отрицателен, то в разряды (2i — 3), (2i — 2), (2i — 1) записывается код 011 соответственно, где i — номер цикла; и записи «1» в младший разряд регистра 8, если знак сумматора

6 положителен, или записи «О», если знак

10 сумматора 6 отрицателен. Далее, выполнение операции сводится к сдвигу содержимого регистра 2 на один разряд вправо и содержимого регистра 3 на один разряд влево; вычитание содержимого регистра 2 из содержимого сумматора l, если знак сумматора 6 положителен, или сложению, если знак сумматора 6 отрицателен.

После выполнения цикла к содержимому счетчика циклов 4 добавляется «1».

Для записи кодов 101 или 011 в определенные разряды регистра 2 в соответствии с номером цикла используется дешифратор на счетчике циклов 4 со схемами объединения 7.

Ошибка вычисления квадратного корня не превышает единицы младшего разряда (как при выполнении операции деления).

Пример а=5 К=З

Вычислить )/ 0,10101.

Исходное состояние регистров 2 и 8 (P2 и

30 Р3 соответственно) и сумматора 1 (СМ).

239665

РЗ = 0.00000 (СМ) = 00,10101.000 Р2 = 0,00000.000 (СМ) (Р2) доп. (СМ) РЗ = 0.00001

РЗ = 0.00010

Р2 = 0.10000.000

Р2 = 0.01000.000

2 цикл i =2 (CM) = 00.01101.000

+ сдвиг

= 11.10110.000

= 00.00011.000

Р2 = 0.10100.000

Р2 = 0.01010.000

РЗ = 0.00011

РЗ = 0.00110 (Р2) доп. (СМ) Р2 = 0.01101.000

Р2 = 0,00110.100

РЗ = 0.00111

РЗ = 0.01110 (СМ) (Р2) доп. (СМ) 4 цикл i =4

= 11.11100.100

+ сдвиг

= 00.00011.011

= 11.11111.111

Р2 = 0.00110,110

Р2 = 0.00011.011

РЗ = 0.01110

РЗ = 0.11100 (СМ) (Р2) пр. (СМ) 5 цикл i=5

= 11.11111.111

+ сдвиг

= 00.00001.100

= 00.00001.011

Р2 = 0.00011.001

Р2 = 0.00001.100

РЗ = 0.11100

РЗ = 0.11000

)СМ) (Р2) пр. (СМ) Р2 = 0.00001 100

Р2 = 0.00000,110

РЗ = 0.11001

РЗ = 0.11001 (СМ) ! Р2) пр.

СМ) 1 цикл i =-1

= 00.10101.000

+ сдвиг

= 11.11000.000

= 00.1101.000

3 цикл 1=3

= 00.00011.000

+ сдвиг

= 11.11100.100

= 11.11100.100

6 цикл i=6

= 00.00001,011

+ сдвиг

= 11.11111.010

= 00.00000.101

В последнем цикле (=6) сдвиг на регистре 8 не производится. Результат выполнения операции находится на регистре 3.

Реау.тьтат Р 0,10101 = 0,11001.

Предмет изобретения

Устройство для вычисления квадратного корня, содержащее параллельный сумматор, регистры и счетчик циклов, отличающееся тем, что, с целью упрощения устройства, оно содержит дешифратор со схемами объединения на выходе, входы которого подключены к выходам счетчика цикла и к выходу триггера знакового разряда сумматора, выходы дешифратора через схемы объединения подсоединены к соответствующим разрядам регистра, выходы регистра сдвига соединены со

10 входами сумматора.

239665

Составитель А. А. Плащин

Редактор Е. В. Семанова Техред А. А. Камышникова Корректор В. П. Федулова

Заказ 1811/19 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2