Декодер сверточных кодов для dvb-t приемника

Иллюстрации

Показать всеИзобретение относится к устройствам цифровой связи, в частности к декодерам сверточных кодов, работающим на основе алгоритма Витерби. Декодер предназначен для использования в высокоскоростных телевизионных системах, работающих в стандарте DVB-T, и аппаратной реализации на программируемых логических или интегральных схемах. Техническим результатом является улучшение помехоустойчивости декодера и увеличение скорости обработки информации. Указанный технический результат достигается тем, что декодер состоит из последовательно соединенных блока вычисления метрик, блока суммирования-сравнения-выбора, блока памяти переходов, блока восстановления кодовых комбинаций и блока памяти кодовых комбинаций, последовательно соединенных блока выбора кодовых комбинаций и блока задержки, и выходного демультиплексора. При этом выход блока суммирования-сравнения-выбора соединен со входом блока выбора кодовых комбинаций, выход блока памяти кодовых комбинаций соединен со входом данных выходного демультиплексора, а выход блока задержки - с адресным входом выходного демультиплексора. 9 ил.

Реферат

Изобретение относится к устройствам цифровой связи, в частности к декодерам сверточных кодов, работающим на основе алгоритма Витерби. Устройство предназначено для использования в высокоскоростных телевизионных системах связи, работающих в стандарте DVB-T (ETSI EN 300744 v1.5.1. "Digital Video Broadcasting (DVB); Framing Structure, Channel Coding And Modulation For Digital Terrestrial Television") [l], и аппаратной реализации на программируемых логических или интегральных схемах.

Декодеры сверточных кодов с большим количеством состояний (более 32), работающие на основе алгоритма Витерби (декодеры Витерби), требуют увеличения вычислительных затрат, причем ресурсоемкость устройства существенно возрастает с ростом кодового ограничения. Большинство существующих в настоящее время устройств предполагает проведение последовательных вычислений, однако при больших значениях кодового ограничения и высоких скоростях следования данных объем производимых операций возрастает настолько, что их выполнение в реальном масштабе времени становится технически затрудненным. Еще одним недостатком большинства существующих декодеров Витерби является избыточное вычисление метрик при декодировании (для всех возможных межсимвольных переходов), вследствие чего существенно возрастают аппаратные затраты, особенно при работе в режиме мягкого решения.

Изобретение направлено на улучшение помехоустойчивости декодера Витерби и увеличение скорости декодирования благодаря усовершенствованию алгоритма, заключающемуся в вычислении наиболее вероятной кодовой комбинации после приема каждого символа и осуществлении в блоке суммирования-сравнения-выбора операции вычитания минимальной метрики, и способа аппаратной реализации, заключающемся во введении новых блоков, распараллеливании и конвейеризации вычислений.

Анализ известных решений показал, что большинство существующих в настоящее время декодеров Витерби имеют схожую структуру и содержат следующие основные блоки: блок вычисления метрик, блок суммирования-сравнения-выбора, блок памяти для хранения переходов и блок восстановления кодовых комбинаций.

Известно устройство «Viterbi Decoder» (патент US 2007/0168845 А1 от 19.07.07), не имеющее с предлагаемым общих признаков, но обладающее тем же назначением и схожим алгоритмом восстановления кодовых комбинаций. Оно предполагает программное декодирование информации и состоит из входного буфера (Input Buffer, IBUF), центрального процессорного устройства (CPU), блока памяти (Memory), декодирующей программы (Decoding Processing Program) и выходного буфера (Output Buffer, OBUF), попарно соединенных между собой.

Недостатком данного устройства является требование конечной длины кодового слова, что возможно выполнить не во всех приемных устройствах; при полубесконечной длине кодового слова определение наиболее вероятной кодовой комбинации в данном устройстве осуществляется по завершении приема блока данных длиной, равной глубине декодирования, вследствие чего ухудшается его помехоустойчивость, так как метрика выбранной кодовой комбинации может оказаться минимальной только после приема последнего символа в силу сложившейся помеховой обстановки, и выбор неверной кодовой комбинации будет влиять на весь принятый блок. Следует также отметить, что вычисление метрик производится для всех возможных межсимвольных переходов, что отнимает значительную часть процессорного времени и повышает требования к памяти; вычисления проводятся последовательно, что затрудняет применение этого устройства для декодирования высокоскоростных потоков данных в реальном масштабе времени.

Известно устройство «Viterbi Decoder» (патент US 2006/0209995 А1 от 21.09.06), состоящее из блока вычисления метрик (Branch Metric Calculation Section), блока суммирования-сравнения-выбора (Add-Compare-Select Calculation Section), блока хранения метрик кодовых комбинаций (Path Metric Storage Section), и последовательно соединенных блока временного хранения переходов (Path Select Signal Temporary Storage Section), блока хранения переходов (Path Select Signal Storage Section) и блока восстановления кодовых комбинаций (Traceback Processing Section), причем выход блока вычисления метрик соединен с первым входом блока суммирования-сравнения-выбора, первый и второй выходы блока суммирования-сравнения-выбора - со входами блока временного хранения переходов и блока хранения метрик кодовых комбинаций соответственно, выход блока хранения метрик кодовых комбинаций - со вторым входом блока суммирования-сравнения-выбора.

Недостатком данного устройства является ухудшение помехоустойчивости вследствие только однократного определения наиболее вероятной кодовой комбинации в течение следования блока данных с длиной, равной глубине декодирования. Данное устройство требует больших объемов вычислений и памяти вследствие организации вычисления метрик для всех возможных переходов между состояниями кода, что является избыточным. Использование данного устройства для декодирования высокоскоростных потоков данных в реальном масштабе времени затруднено вследствие последовательного выполнения вычислений. По схожести большинства признаков данное устройство выбрано за прототип.

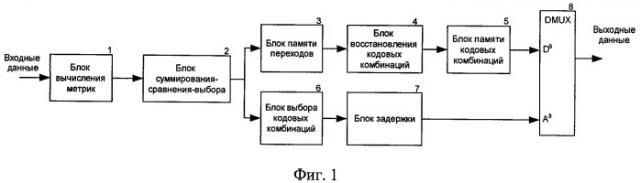

Сущностью изобретения является декодер сверточных кодов, работающий на основе алгоритма Витерби, предназначенный для применения в высокоскоростных телевизионных системах, работающих в стандарте DVB-T (ETSI EN 300744 v1.5.1. "Digital Video Broadcasting (DVB); Framing Structure, Channel Coding And Modulation For Digital Terrestrial Television") [1] и аппаратной реализации на программируемых логических или интегральных схемах, предполагающий полубесконечную длину кодового слова, параллельное вычисление метрик в реальном масштабе времени и - выбор наиболее вероятной кодовой комбинации после приема каждого символа и состоящий из последовательно соединенных блока вычисления метрик 1, блока суммирования-сравнения-выбора 2, блока памяти переходов 3, блока восстановления кодовых комбинаций 4 и блока памяти кодовых комбинаций 5, последовательно соединенных блока выбора кодовых комбинаций 6 и блока задержки 7, и выходного демультиплексора 8, причем выход блока суммирования-сравнения-выбора 2 соединен со входом блока выбора кодовых комбинаций 6, выход блока памяти кодовых комбинаций 5 - со входом данных, а выход блока задержки 7 - с адресным входом выходного демультиплексора 8 (Фиг.1); а блоки памяти переходов 3 и памяти кодовых комбинаций 5 построены по принципу FILO («First In-Last Out», «пришел первым - вышел последним»).

Сопоставительный анализ с прототипом показывает, что предлагаемое устройство отличается наличием новых элементов: последовательно соединенных блока выбора кодовых комбинаций 6 и блока задержки 7, а также выходного демультиплексора 8, причем выход блока суммирования-сравнения-выбора 2 соединен со входом блока выбора кодовых комбинаций 6, выход блока памяти кодовых комбинаций 5 - со входом данных, а выход блока задержки 7 - с адресным входом выходного демультиплексора 8, блок памяти переходов 3 и блок памяти кодовых комбинаций 5 организованны по принципу FILO («пришел первым - вышел последним»), а блок суммирования-сравнения-выбора 2 содержит операцию вычитания значения минимальной метрики. Таким образом, устройство удовлетворяет критерию «новизна».

Изобретение поясняется следующим графическим материалом:

Фиг.1. Общая функциональная схема декодера.

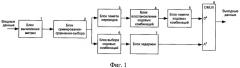

Фиг.2. Структурная схема блока вычисления метрик.

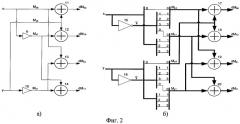

Фиг.3. Структурная схема блока суммирования-сравнения-выбора.

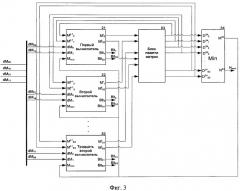

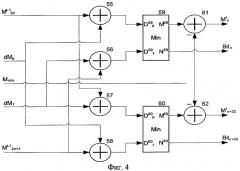

Фиг.4. Структурная схема вычислителя блока суммирования-сравнения-выбора.

Фиг.5. Структурная схема блока памяти переходов.

Фиг.6. Структурная схема блока восстановления кодовых комбинаций.

Фиг.7. Структурная схема блока выбора кодовых комбинаций.

Фиг.8. Структурная схема подблока демультиплексирования блока выбора кодовых комбинаций.

Фиг.9. Схема подрешетки графа состояний сверточного кода.

В случае сверточного кода скоростью 1/2 с величиной кодового ограничения Lc=7 (число состояний М=64), который используется в стандарте DVB-T (ETSI EN 300 744 v1.5.1. "Digital Video Broadcasting (DVB); Framing Structure, Channel Coding And Modulation For Digital Terrestrial Television") [1], декодер сверточного кода работает следующим образом. Предусмотрено два режима работы - режим жесткого решения и режим мягкого решения.

В режиме жесткого решения входные символы x и y представлены однобитными, а в режиме N-битного мягкого решения - N-битными числами в дополнительном коде, количественно характеризующими соответствие принимаемых данных единичному или нулевому символу. При этом нулевому символу соответствует максимально положительное число, а единичному - максимально отрицательное.

Блок вычисления метрик 1 производит вычисление хеммингова расстояния в случае жесткого решения и евклидова расстояния - в случае мягкого для принятого символа xy относительно всех возможных входных комбинаций декодера. Вычисленные данные подаются на вход блока суммирования-сравнения-выбора 2, в котором для каждого из состояний кода вычисляются метрики двух кодовых комбинаций, соответствующих текущему состоянию, из каждой пары выбирается комбинация с наименьшей метрикой, и вырабатывается сигнал перехода. После этого вычисляется номер состояния, которому соответствует минимальное из выбранных значений метрик и осуществляется операция вычитания этого значения из значений всех вычисленных метрик. Сигналы переходов из блока суммирования-сравнения-выбора 2 передаются в блок памяти переходов 3 и в блок выбора кодовых комбинаций 7. В блок выбора кодовых комбинаций 7 также передается номер состояния с минимальной метрикой. Блок памяти переходов 3 накапливает пакет входных данных длиной, равной глубине декодирования, после чего эти данные выдаются в обратном порядке в блок восстановления кодовых комбинаций 4, где производится их обработка для каждого из состояний сверточного кода. Одновременно с выдачей данных в блок восстановления кодовых комбинаций 4 блок памяти переходов 3 производит накопление следующего пакета. По мере обработки данные поступают в блок памяти кодовых комбинаций 5, который функционирует аналогично блоку памяти переходов 3. Блок выбора кодовых комбинаций 6 на основе сигналов переходов и номера состояния с минимальной метрикой, сформированных в блоке суммирования-сравнения-выбора 2, вырабатывает сигнал выбора кодовой комбинации для каждого из состояний, устанавливающий их соответствие данным, обрабатываемым в текущий момент в блоке восстановления кодовых комбинаций 4. Сигнал выбора кодовых комбинаций, соответствующий состоянию с минимальной метрикой поступает в блок задержки 7 с целью его синхронизации с соответствующим ему выходным словом блока памяти кодовых комбинаций 5. Декодированная последовательность формируется выходным демультиплексором 8 путем выдачи на выход символа выходного слова памяти кодовых комбинаций 6 с адресом, поступающим с блока задержки 7.

Блок вычисления метрик 1 предназначен для вычисления хеммингова расстояния dMXY=(x⊕Х)+(y⊕Y), где ⊕ - операция «исключающего или», в режиме жесткого решения и евклидова расстояния dMXY=|x-Х|+|y-Y| - в режиме мягкого, для входного символа xy, относительно всех возможных входных комбинаций XY. В режиме жесткого решения (Фиг.2а) блок вычисления метрик 1 состоит из инверторов: первого 9 и второго 10, и сумматоров: первого 11, второго 12, третьего 13 и четвертого 14, а в режиме мягкого решения (Фиг.2б) - из инверторов: третьего 15 и четвертого 16, и сумматоров: пятого 17, шестого 18, седьмого 19 и восьмого 20, причем инверторы: первый 9 и второй 10, и сумматоры: первый 11, второй 12, третий 13 и четвертый 14, являются однобитными, а инверторы: третий 15 и четвертый 16, и сумматоры: пятый 17, шестой 18, седьмой 19 и восьмой 20 - четырехбитными. В режиме жесткого решения вход x блока вычисления метрик 1 объединен со входом первого инвертора 9, с первым входом первого сумматора 11 и вторым входом третьего сумматора 13, вход y блока вычисления метрик 1 объединен со входом второго инвертора 10 и со вторыми входами первого сумматора 11 и второго сумматора 12; выход первого инвертора 9 соединен с первым входом второго сумматора 12 и со вторым входом четвертого сумматора 14; выход второго инвертора 10 соединен с первыми входами третьего сумматора 13 и четвертого сумматора 14. В режиме четырехбитного мягкого решения входы x и y блока вычисления метрик 1 объединены со входами третьего и четвертого инверторов 15 и 16 соответственно, сигнал с выхода третьего инвертора 15, старший бит которого является старшим битом сигнала со входа x блока вычисления метрик 1, подается на первый вход пятого сумматора 17 и второй вход седьмого сумматора 19; сигнал с выхода четвертого инвертора 16, старший бит которого является старшим битом сигнала со входа у блока вычисления метрик 1, подается на вторые входы пятого сумматора 17 и шестого сумматора 18; сигнал со входа x блока вычисления метрик 1, старший бит которого является старшим битом сигнала с выхода третьего инвертора 15, подается на первый вход шестого сумматора 18 и второй вход восьмого сумматора 20; сигнал со входа у блока вычисления метрик 1, старший бит которого является старшим битом сигнала с выхода четвертого инвертора 16, подается на первые входы седьмого сумматора 19 и восьмого сумматора 20.

Блок вычисления метрик 1 работает следующим образом. В режиме жесткого решения значения (Фиг.2а) приращений метрик dMx0 и dMy0 для входных сигналов x и y относительно нулевого символа равны значениям самих сигналов x и y, а значения приращений метрик dMx1 и dMy1 относительно единичного символа - их инвертированным значениям. На выходах первого 11, второго 12, третьего 13 и четвертого 14 сумматоров формируются четыре значения приращений метрик dM00, dM01, dM10 и dM11 соответственно, вычисленные согласно формуле (I):

В режиме четырехбитного мягкого решения (Фиг.26) приращения метрик входных значений x и y относительно единичного символа равны соответственно dMx1=х+8 и dMy1=y+8. Такая операция эквивалентна инверсии старшего (знакового) бита, причем приращения метрик dMx1 и dMy1 будут четырехбитными беззнаковыми числами. Вследствие того, что сумма приращений метрик относительно нулевого и единичного символов равна dMx0+dMx1=dMy0+dMy1=15, приращение метрики относительно нулевого символа равно проинвертированному приращению метрики относительно единичного: и , то есть при вычислении приращений метрик dMx0 и dMy0 символов x и y относительно нулевого символа инвертируются все биты, кроме старшего. Метрики dM00, dM01, dM10 и dM11 входного символа относительно возможных опорных значений формируются на выходах сумматоров: первого 17, второго 18, третьего 19 и четвертого 20 соответственно согласно формуле (1). Такой способ построения блока вычисления метрик 1 существенно упрощает его структуру.

При декодировании прореженных сверточных кодов (со скоростями 2/3, 3/4, 5/6 и 7/8) [1] в блоке вычисления метрик 1 выколотые позиции символов заполняются постоянными значениями, а приращения метрик относительно этих значений считаются равными нулю.

Блок суммирования-сравнения-выбора 2 (Фиг.3) состоит из идентичных вычислителей с первого по тридцать второй 21-52 соответственно, блока памяти метрик 53 и первого вычислителя минимального значения 54, причем блок памяти метрик 53 является набором из шестидесяти четырех регистров, первые выходы вычислителей с первого по тридцать второй 21-52 соединены со входами регистров с первого по тридцать второй блока памяти метрик 53 соответственно, вторые выходы вычислителей с первого по тридцать второй 21-52 - со входами регистров с тридцать третьего по шестьдесят четвертый блока памяти метрик 53 соответственно; выходы нечетных регистров с первого по шестьдесят третий блок памяти метрик 53 соединены с первыми входами вычислителей с первого по тридцать второй 21-52 соответственно и с четными входами D54 0…D54 62 первого вычислителя минимального значения 54 соответственно, а выходы четных регистров со второго по шестьдесят четвертый блока памяти метрик 53 - со вторыми входами вычислителей с первого по тридцать второй 21-52 соответственно и с нечетными входами D54 1…D54 63 первого вычислителя минимального значения 54 соответственно; первый выход М54 первого вычислителя минимального значения 54 соединен с пятыми входами вычислителей с первого по тридцать второй 21-52.

Вычислители с первого по тридцать второй 21-52 (Фиг.4) состоят из девятого 55, десятого 56, одиннадцатого 57 и двенадцатого 58 сумматоров, второго 59 и третьего 60 вычислителей минимального значения и первого 61 и второго 62 вычитателей, причем первый вход вычислителя объединен с первым входом девятого сумматора 55 и со вторым входом одиннадцатого сумматора 57; второй вход вычислителя - со вторым входом десятого сумматора 56 и первым входом двенадцатого сумматора 58; третий вход dM0 вычислителя - со вторыми входами девятого сумматора 55 и двенадцатого сумматора 58; четвертый вход dM1 вычислителя - с первыми входами десятого сумматора 56 и одиннадцатого сумматора 57; выходы девятого сумматора 55 и десятого сумматора 56 соединены с первым D59 0 и вторым D59 1 входами второго вычислителя минимального значения 59 соответственно, а выходы одиннадцатого сумматора 57 и двенадцатого сумматора 58 - с первым D60 0 и вторым D60 1 входами третьего вычислителя минимального значения 60 соответственно. Выходы М59 второго вычислителя минимального значения 59 и М60 третьего вычислителя минимального значения 60 соединены с прямыми входами первого вычиталеля 61 и второго вычитателя 62 соответственно, а пятый вход Mmin вычислителя - с инверсными входами первого вычитателя 61 и второго вычитателя 62.

Блок суммирования-сравнения-выбора 2 работает следующим образом. Граф состояний сверточного кода может быть разбит на 32 подрешетки, показанные на Фиг.9. Переходам из состояния 2n в состояние n и из состояния 2n+1 в состояние n+32 на графе соответствуют одинаковые символы на входе устройства, а переходам 2n→n+32 и 2n+1→n - логически проинвертированные символы. Исходя из этого вычисление метрик состояний в блоке суммирования-сравнения-выбора 2 реализовано тридцатью двумя идентичными вычислителями 21-52, функционирующими в соответствии с графом состояний сверточного кода (Фиг.9). Каждый вычислитель 21-52 работает согласно следующему алгоритму:

;

;

где и - значения метрик, формируемые для n-го и (n+32)-го состояний на первом и втором выходе вычислителя соответственно, а Bitn и Bitn+32 - сигналы переходов, формируемые для этих состояний на третьем и четвертом выходах вычислителя соответственно. На первый и второй входы вычислителей 21-52 подаются значения метрик и кодовых комбинаций соответственно, формируемые на выходе блока памяти метрик 53 и соответствующие после приема предыдущего символа состояниям с номерами 2n и 2n+1; на третий и четвертый входы - сформированные в блоке вычисления метрик 1 значения приращений метрик dM0 и dM1, входного символа xy относительно опорных символов XY и соответственно, изображенных на ребрах подрешеток графа состояний сверточного кода (Фиг.9); на пятый вход - значение минимальной метрики Mmin после приема предыдущего символа, формируемое в первом вычислителе минимального значения 54.

Операция вычитания минимальной метрики Mmin позволяет избежать переполнения разрядной сетки при работе декодера в условиях низкого отношения сигнал-шум.

На втором выходе N54 первого вычислителя минимального значения 54 формируется индекс, соответствующий минимальному значению, и подаваемый на блок выбора кодовых комбинаций 6; на первом выходе М54 - само минимальное значение. Сигналы переходов с третьего Bitn и четвертого Bitn+32 выходов вычислителей 21-52 блока суммирования-сравнения-выбора 2 формируют входное 64-разрядное слово Bits для блока памяти переходов 3. Сигналы с третьих выходов Bitn вычислителей с первого по тридцать второй 21-52 являются нечетными битами с первого по шестьдесят третий выходного слова блока суммирования-сравнения-выбора 2 соответственно, а сигналы с четвертых выходов Bitn+32 вычислителей 21-52 - четными битами со второго по шестьдесят четвертый выходного слова соответственно.

Блоки памяти переходов 3 и кодовых комбинаций 5 (Фиг.5) состоят из ОЗУ 63 и счетчика 64, причем выход счетчика 64 соединен с адресным входом А63, а вход блока памяти переходов 3 или блока памяти кодовых комбинаций 5 объединен со входом данных D63 ОЗУ 63.

Работа блоков памяти переходов 3 и памяти кодовых комбинаций 5 организована по принципу FILO («вошел первым - вышел последним»). Разрядность ОЗУ 63 равна 128×64 бита. Счетчик 64 адреса ОЗУ 63 меняет направление счета на границе разрядной сетки. Для каждого значения адреса производится чтение данных из ОЗУ 63, выдача их на выход, а затем запись входных данных по текущему адресу.

Блок восстановления кодовых комбинаций 4 (Фиг.6) предназначен для обработки шестидесяти четырех последовательностей, соответствующих каждому из возможных состояний кода после приема блока данных длиной Ld=128, равной глубине декодирования, и состоит из шестидесяти четырех идентичных каналов 65-128, каждый из которых включает в себя последовательно соединенные сдвиговый регистр 129 и демультиплексор 130, причем входные данные подаются на вход данных D130 демультиплексора 130, выход которого соединен со входом разряда D129 5 сдвигового регистра 129; выходы разрядов D129 0…D129 5 сдвигового регистра 129, объединенные в шестибитное слово, соединены с адресным входом А130 демультиплексора 130; выходные данные снимаются с выхода D129 0 сдвигового регистра 129 каждого канала.

В каналах с первого по шестьдесят четвертый 65-128 блока восстановления кодовых комбинаций 4 производится восстановление последовательностей, соответствующих состояниям 0…63 соответственно в результате приема блока данных длиной Ld=128. На вход D129 5 сдвигового регистра 129 подается символ с адресом во входном слове, равным состоянию сдвигового регистра 129. Выходные биты старших разрядов D129 0 сдвиговых регистров 129 каналов с первого по шестьдесят четвертый 65-128 образуют входное слово блока памяти кодовых комбинаций 5. Перед началом восстановления сдвиговые регистры каналов с первого по шестьдесят четвертый 65-128 сбрасываются в состояния 0…63 соответственно.

Блок выбора кодовых комбинаций 6 (Фиг.7) предназначен для синтеза сигнала, определяющего соответствие состояния с минимальной метрикой одной из кодовых комбинаций, обрабатываемых в блоке восстановления кодовых комбинаций 4, и состоит из идентичных подблоков демультиплексирования с первого по тридцать второй 131-162, блока памяти сигналов выбора кодовых комбинаций 163 и первого демультиплексора 164, причем блок памяти сигналов выбора кодовых комбинаций 163 является набором из шестидесяти четырех регистров, первые выходы подблоков демультиплексирования с первого по тридцать второй 131-162 соединены со входами регистров с первого по тридцать второй блока памяти сигналов выбора кодовых комбинаций 163 соответственно, вторые выходы подблоков демультиплексирования с первого по тридцать второй 131-162 соединены со входами регистров с тридцать третьего по шестьдесят четвертый блока памяти сигналов выбора кодовых комбинаций 163 соответственно; выходы нечетных регистров с первого по шестьдесят третий блока памяти сигналов выбора кодовых комбинаций 163 соединены с первыми входами подблоков демультиплексирования с первого по тридцать второй 131-162 соответственно и с четными входами данных D164 0…D164 62 первого демультиплексора 164 соответственно, выходы четных регистров со второго по шестьдесят четвертый блока памяти сигналов выбора кодовых комбинаций 163 соединены со вторыми входами подблоков демультиплексирования с первого по тридцать второй 131-162 соответственно и с нечетными входами данных D164 1…D164 63 демультиплексора 164; третьи выходы вычислителей с первого по тридцать второй 21-52 блока суммирования-сравнения-выбора 2 соединены с третьими входами подблоков демультиплексирования с первого по тридцать второй 131-162 соответственно, а четвертые выходы вычислителей с первого по тридцать второй 21-52 блока суммирования-сравнения-выбора 2 соединены с четвертыми входами подблоков демультиплексирования с первого по тридцать второй 131-162 соответственно; второй выход N54 первого вычислителя минимального значения 54 блока суммирования-сравнения-выбора 2 соединен с адресным входом А164 первого демультиплексора 164.

Подблоки демультиплексирования с первого по тридцать второй 131-162 (Фиг.8) состоят из второго 165 и третьего 166 демультиплексоров, причем первый вход подблока демультиплексирования соединен с первыми входами D165 0 второго демультиплексора 165 и D166 0 третьего демультиплексора 166, второй вход подблока демультиплексирования - со вторыми входами D166 0 второго демультиплексора 165 и D166 1 третьего демультиплексора 166, третий An и четверый An+32 входы подблока демультиплексирования - с адресными входами А165 второго демультиплексора 165 и А166 третьего демультиплексора 166 соответственно

На выходы первого 165 и второго 166 демультиплексоров подается значение , если значения на адресных входах А165 и А166 соответственно равны нулю, и значение - в противном случае. В регистрах с первого во шестьдесят четвертый блока памяти сигналов выбора кодовых комбинаций 163 сохраняются номера каналов блока восстановления кодовых комбинаций 4, в которых обрабатываются последовательности, соответствующие состояниям 0…63 соответственно. На выход первого демультиплексора 164 подаются данные с выхода блока памяти сигналов выбора кодовых комбинаций 163, с адресом, сформированным на адресном входе А164. По завершении приема очередного блока данных длиной, равной глубине декодирования, второй блок памяти сигналов выбора кодовых комбинаций 163 сбрасывается, его регистры с первого по шестьдесят четвертый устанавливаются в состояния 0…63 соответственно.

Блок задержки 7 является шестидесятичетырехразрядным сдвиговым регистром с глубиной, равной глубине декодирования Ld=128, и осуществляет задержку входного сигнала на величину глубины декодирования Ld.

Выходной демультиплексор 8 выдает на выход устройства декодированный символ, поступающий из блока памяти кодовых комбинаций 6, с адресом, поступающим с выхода блока задержки 7.

Предлагаемое устройство позволяет декодировать высокоскоростные потоки данных в реальном масштабе времени благодаря распараллеливанию и конвейеризации вычислений, причем благодаря усовершенствованию алгоритма, заключающемуся в определении наиболее вероятной кодовой комбинации после приема каждого символа и осуществлении в блоке суммирования-сравнения-выбора операции вычитания минимальной метрики, улучшена его помехоустойчивость по сравнению с прототипом. Благодаря устранению избыточных вычислений метрик для всех возможных межсимвольных переходов количество вычислительных операций в блоке вычисления метрик уменьшено по сравнению количеством вычислений, проводимых в аналогичном блоке прототипа. Благодаря организации блоков памяти переходов и памяти кодовых комбинаций по принципу FILO («пришел первым - вышел последним») минимизировано увеличение аппаратных затрат по сравнению с прототипом.

Источник информации

1. "Digital Video Broadcasting (DVB); Framing Structure, Channel Coding And Modulation For Digital Terrestrial Television." Final draft ETSI EN 300744, v1.5.1. (2004-06). European standart (Telecommunication series).

Декодер сверточных кодов, работающий на основе алгоритма Витерби, состоящий из последовательно соединенных блока вычисления метрик, блока суммирования-сравнения-выбора, блока памяти переходов и блока восстановления кодовых комбинаций, отличающийся наличием новых элементов: блока памяти кодовых комбинаций, выходного демультиплексора и последовательно соединенных блока выбора кодовых комбинаций и блока задержки, причем блок суммирования-сравнения-выбора соединен с блоком выбора кодовых комбинаций, а блок восстановления кодовых комбинаций соединен с блоком памяти кодовых комбинаций, соединенным со входом данных выходного демультиплексора, ко входу адреса которого подсоединен блок задержки; блоки памяти переходов и памяти кодовых комбинаций выполнены с возможностью накапливать входные данные и выдавать их в обратном порядке, а блок суммирования-сравнения-выбора содержит операцию вычитания минимальной метрики.