Способ и система для предоставления энергетически эффективного регистрового файла

Иллюстрации

Показать всеИзобретение относится к регистровым файлам, в частности к способам и системам для предоставления энергетически эффективных регистровых файлов. Техническим результатом является предотвращение недостоверных операций считывания. Файловый регистр содержит множество регистров, каждый из которых содержит множество ячеек памяти, при этом первая ячейка из множества ячеек памяти регистра сконфигурирована для хранения сигнала готовности, состояние которого указывает, достоверны ли хранящиеся в регистре данные, а остальные ячейки из множества ячеек регистра сконфигурированы для хранения данных в регистре; и декодер, сконфигурированный для приема адреса целевого регистра, выбранного из множества регистров, причем декодер в ответ на сигнал готовности, сохраненный в первой ячейке памяти целевого регистра, избирательно отклоняет вывод данных с целевого регистра, когда состояние сигнала готовности, сохраненного в первой ячейке памяти целевого регистра, указывает, что данные в регистре недействительны, и разрешает выводить данные целевого регистра, когда состояние сигнала готовности, сохраненного в первой ячейке памяти целевого регистра, указывает, что данные в регистре действительны. Способ описывает работу регистрового файла. 3 н. и 18 з.п. ф-лы, 2 ил.

Реферат

Область техники

Настоящее изобретение относится в общем к регистровым файлам и, более определенно, к способам и системам для предоставления энергетически эффективных регистровых файлов.

Уровень техники

Конструкция встроенного процессора обычно включает в себя в себя такую временную память, как кэши команд, кэши данных и регистровые файлы, и т.д. Эти элементы памяти представляют собой относительно небольшие, высокоскоростные блоки памяти, увеличивающие скорость процессора, уменьшая число обращений процессора к более медленной внешней памяти. К сожалению, этим элементам памяти свойственно большое энергопотребление из-за переключающихся емкостных нагрузок. Большие элементы должны переключать больше емкостных нагрузок, нежели меньшие элементы, и поэтому потребляют больше энергии. Например, после кэширования команд и данных, регистровые файлы, которые используются как универсальные регистры, обычно потребляют больше энергии, чем большинство других, меньших элементов в конструкции встроенного процессора.

Когда команда выполняется, необходимые исходные операнды первыми извлекаются из соответствующего регистрового файла(ов). После того как команда выполнена, результаты, если таковые имеются, записываются снова в регистровый(е) файл(ы). Однако прежде, чем эти результаты снова записываются в регистровый(е) файл(ы), один или несколько этих результатов часто необходимы для последующей команды как исходный операнд и, таким образом, берутся трансляционной сетью для дальнейшей обработки. Чем длиннее конвейер, тем более вероятно, что исходные операнды будут доставлены в трансляционную сеть вместо регистрового файла; кроме того, чем чаще результаты берутся трансляционной сетью, тем дольше соответствующий регистровый(е) файл(ы) должен(ны) ждать, прежде чем они обновятся последними данными. Одна из возможностей при этом заключается в том, что недостоверные данные остаются в регистровом(ых) файле(ах) на более длительные промежутки времени. Если последующие операции считывания выполняются на регистровом(ых) файле(ах), имеющем недостоверные данные, то такие операции считывания приведут к недостоверным результатам, если они используются для выполнения команды. Кроме того, израсходованная на такие операции энергия оказывается потраченной впустую. Следовательно, было бы желательно предоставить энергетически эффективное средство для предотвращения недостоверных операций считывания.

Сущность изобретения

Настоящее изобретение направлено на устранение недостатков, известных из уровня техники, при этом задачей настоящего изобретения является улучшение эффективности считывания данных из регистрового файла, предотвращая недостоверные операции считывания.

Представлен регистровый файл. Регистровый файл включает в себя множество регистров и декодер, сконфигурированный для приема адреса для любого одного из регистров и отключения операции считывания адресного регистра, если данные в адресном регистре недостоверны.

Представлен другой регистровый файл. Регистровый файл включает в себя множество регистров, средство для приема адреса для любого одного из регистров и средство для отключения операции считывания адресного регистра, если данные в адресном регистре недостоверны.

Способ доступа к регистровому файлу, имеющему множество регистров, включает в себя прием адреса для одного из регистров, и отключение операции считывания адресного регистра, в ответ на то, что данные в адресном регистре недостоверны.

Из нижеследующего подробного описания специалистам в данной области техники должно быть ясно, что возможны другие варианты реализации настоящего изобретения, причем различные варианты реализации изобретения показаны ниже для примера. Понятно, что изобретение применимо к другим, отличающимся вариантам реализации, и различные его детали могут быть модифицированы в различных аспектах, но без отступления от сущности и объема настоящего изобретения. Соответственно, чертежи и подробное описание, по существу, имеют иллюстративный характер и не означают ограничений.

Краткое описание чертежей

Объекты настоящего изобретения показаны на соответствующих чертежах в качестве примера, а не для ограничения, причем на чертежах представлено следующее:

Фиг.1 изображает упрощенную блок-схему системы с энергетически эффективным регистровым файлом в соответствии с настоящим раскрытием существа изобретения;

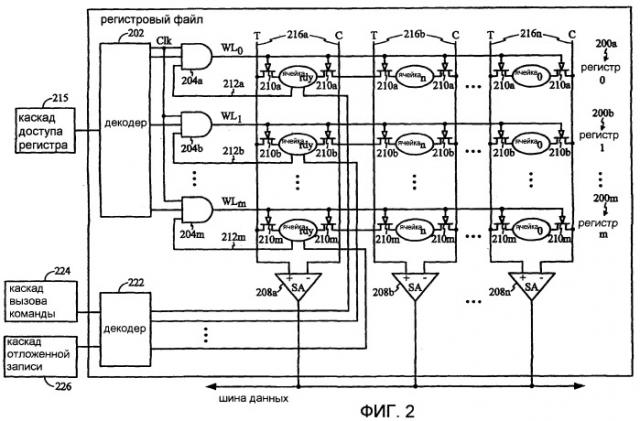

Фиг.2 - упрощенная блок-схема, иллюстрирующая один вариант реализации энергетически эффективного регистрового файла в соответствии с настоящим раскрытием сущности изобретения.

Подробное описание

Излагаемое ниже подробное описание вместе с приложенными чертежами представляет собой описание различных вариантов реализации настоящего изобретения, но не означает отображение только тех вариантов реализации, в которых настоящее изобретение может быть осуществлено. Подробное описание включает в себя конкретные детали для получения полного понимания настоящего изобретения. Однако специалистам в данной области техники будет ясно, что настоящее изобретение может быть осуществлено без этих конкретных деталей. В некоторых случаях, хорошо известные структуры и компоненты показаны в виде блок-схем, чтобы избежать неясностей в понимании концепции настоящего изобретения.

На Фиг.1 показана принципиальная блок-схема примерной системы 100 обработки данных, пригодной для обработки, поиска и хранения информации. Система 100 обработки данных может быть автономным компонентом или, альтернативно, может быть встроенной в устройство, например мобильный телефон, карманный компьютер, персональный компьютер, ноутбук, цифровую камеру, игровой пульт или любое другое подходящее устройство. Система 100 обработки данных может включать в себя процессор 102, например микропроцессор, процессор цифровых сигналов, видеопроцессор графических символов, или любой другой подходящий процессор. Система 100 обработки данных может также включать в себя память 104, которая содержит программные команды и данные, требующиеся процессору 102 для выполнения его функций.

Процессор 102 может быть сконфигурирован как процессор с конвейерной обработкой данных. Также могут быть предоставлены кэши 108 команд и данных для команд и данных, к которым обращались недавно. Регистровый файл 106 может быть предоставлен для хранения операндов, необходимых конвейеру 110 для выполнения команд. Когда команда должна выполняться, исходные операнды для такой команды могут быть извлечены из регистрового файла 106 и затем использованы в конвейере 110 для выполнения команды. После выполнения команды любые результаты могут быть записаны в регистровый файл 106 для использования в качестве исходных операндов для последующих команд или предоставлены в трансляционную сеть для дальнейшей обработки. Процессор 102 может также включать в себя периферийные устройства, или любые другие типы устройств, которые управляют вычислительными процессами или перемещением данных.

На Фиг.2 показана блок-схема, иллюстрирующая то, как процессор обращается к своему внутреннему регистровому файлу. Регистровый файл 106 может включать в себя множество регистров 200a-m. Каждый регистр 200 может использоваться для хранения данных. Такие данные могут использоваться как операнд для команды. Регистровый файл 106 может также включать в себя множество других компонентов, включая, например, декодер 202, и логические устройства 204a-m. Декодер 202 и логические устройства 204a-m показаны на Фиг.2 для иллюстрации того, как процессор считывает из регистрового файла. Схема, требуемая для записи в ячейки, хорошо известна в данной области техники и поэтому не показана.

Каждый из регистров 200a-m может включать в себя множество ячеек 206a-m и множество переключателей 210a-m. Внутреннее устройство и логические особенности ячеек 206a известны в данной области техники, и поэтому далее не рассматриваются. Переключатели показаны как полевые транзисторы (FET), но могут быть переключателями любого подходящего типа. Два переключателя используются с каждой ячейкой для подачи сохраненного бита и его дополнения в пару дифференциальных разрядных шин 216a-216n, когда его регистр разблокирован. Регистры могут быть разблокированы через их соответствующие логические устройства 204a-204m. Логические устройства 204a-204m используются для генерации разрешающего сигнала на одной из числовых шин WL0-WLm, которые выбирают соответствующий регистр. Логические устройства 204a-204m реализованы на Фиг.2 функцией «И», но могут быть реализованы любым подходящим образом. Сигнал 212a-212m готовности операнда от каждой ячейки 206a-m может быть предоставлен как входной сигнал на ее соответствующее логическое устройство 204a-m. Использование сигнала 212a-212m готовности операнда дополнительно рассмотрено ниже. Тактовый сигнал 218 также может быть предоставлен как входной сигнал на логические устройства 204a-m для управления их активацией на основе тактирования схемы. Поскольку в данный момент времени выбирается только один регистр, дифференциальные разрядные шины для каждой позиции двоичного разряда множества регистров могут совместно использовать тот же самый усилитель считывания. Усилители считывания 208a-208m предоставляют выходной сигнал исходя из их соответствующих дифференциальных разрядных шин.

Операции регистрового файла 106 дополнительно рассматриваются ниже. При операции считывания адрес 214 регистрового файла предоставляется на декодер 202 из каскада 215 регистрового доступа в конвейере процессора. Декодер 202 активизирует целевой регистр, предоставляя надлежащий управляющий сигнал на соответствующее логическое устройство. Логическое устройство, соответствующее целевому регистру, также принимает, как входной сигнал, сигнал 212a-m готовности от одной из ячеек, связанных с целевым регистром. Логическое устройство использует состояние сигнала 212a-m готовности для определения, следует ли разблокировать ячейки, связанные с целевым регистром. В зависимости от состояния сигнала готовности логическое устройство может тогда разблокировать целевой регистр, подключая целевые регистровые ячейки к дифференциальным разрядными шинам через их соответствующие переключатели, тем самым разрешая считывание данных, содержащихся в ячейках, через усилители 208a-n считывания.

Состояние сигнала 212 готовности указывает, достоверны ли хранящиеся в регистре 200a-m данные, или нет. Данные не достоверны, когда команда на запись в целевой регистр 200a-m находится в конвейере, но еще не записаны снова в целевой регистр 200a-m данные, следующие из выполнения этой команды. В течение такого периода сигнал готовности может быть переключен в состояние "отключено" для предотвращения команды считывания в конвейере, которая следует за командой записи, от доступа к целевому регистру.

Состояние сигнала 212 готовности может управляться множеством способов. Например, сигнал 212 готовности может быть переключен в состояние "отключено" для указания того, что данные не достоверны, когда команда, которая обновляет этот регистр, извлекается конвейером, и в состояние "включено", для указания того, что данные достоверны, когда данные, следующие из выполнения этой команды записи, были снова записаны в регистр.

Пример методологии обновления сигнала готовности показан на Фиг.2. Декодер 222 может быть сконфигурирован для предоставления сигнала "установка" и "сброс" в ячейке в каждом регистре, поддерживающем сигнал готовности. В этом примере сигнал "установка" используется для переключения сигнала готовности в состояние "включено", и сигнал "сброс" используется для переключения сигнала готовности в состояние "отключено". Полярности могут различаться в других вариантах реализации в зависимости от логического вентиля числовой шины WLX. Декодер 222 может управляться от различных каскадов в пределах конвейера в зависимости от конкретного применения и общих ограничений конструкции. По меньшей мере, в одном варианте реализации процессора сигнал готовности является "сбросом", когда команда записи извлекается конвейером. То есть адрес регистрового файла для команды записи, наряду с сигналом управления "сброс" предоставляется на декодер 222 из каскада 224 выбора команды в конвейер. Если работает команда записи, то она проходит через конвейер и достигает каскада 226 отложенной записи, адреса регистрового файла, и управляющий сигнал "установка" может быть предоставлен на декодер 222. Это заставляет декодер "установить" сигнал готовности в регистровом файле.

Другая методология обновления сигнала готовности заключается в использовании разрядных шин 216a способом, подобным тому, как записываются другие ячейки. Основываясь на данном рассмотрении и заявляемых положениях, специалист в данной области техники поймет, как использовать соответствующую логику, схемы и/или другие компоненты для осуществления сигнала 212 готовности операнда в соответствии с настоящим рассмотрением.

Когда состояние сигнала 212 готовности операнда указывает, что сохраняемые данные в целевом регистре не достоверны, соответствующее логическое устройство отключается (то есть соответствующий выходной сигнал числовой шины WLx из логики не активизирует переключатели, связанные с целевым регистром). В результате разрядные шины 2l6a-n удерживаются от переключения, что, в свою очередь, означает, что усилители считывания 208a-n также удерживаются от переключения. Поэтому данные, сохраненные в целевом регистре, не выводятся через усилители считывания 208a-n.

Ниже приводится пример, дополнительно иллюстрирующий операции регистрового файла 106. Предполагается, что адрес регистрового файла идентифицирует регистр 200a для операции считывания в соответствии с командой. Декодер 202 декодирует такую информацию и посылает соответствующий сигнал управления на логическое устройство 204a для указания того, что регистр 200a назначен для операции считывания. Другие управляющие сигналы также посылаются декодером 202 на другие логические устройства 204b-m для указания того, что другие регистры 200b-m не требуются для этой конкретной операции считывания.

Логическое устройство 204a также принимает сигнал 212a готовности операнда от одной из ячеек 206a, связанных с регистром 200a. Если сигнал 212a готовности операнда указывает, что данные в регистре 200a не достоверны, логическое устройство 204a отключается, то есть логическое устройство 204a выводит сигнал управления на числовую шину WL0, что предотвращает переключение переключателей 210a. В результате разрядные шины 216a-n не переключаются, и данные, сохраняемые в ячейках 206a, не выводятся через усилители считывания 208a-n. Альтернативно, если сигнал 212a готовности операнда указывает, что данные, сохраняемые в регистре 200a достоверны, логическое устройство 204a выводит управляющий сигнал на числовую шину WL0, которая задействует переключатели 210a. В результате данные от целевого регистра 200a помещаются в разрядные шины 216a-n и выводятся из регистрового файла 106 через усилители считывания 208a-n.

Различные примерные логические блоки, модули, схемы, элементы и/или компоненты, описанные в связи с представленными вариантами реализации, могут быть осуществлены или выполнены с универсальным процессором, цифровым сигнальным процессором (DSP), прикладной специализированной интегральной схемой (ASIC), программируемой вентильной матрицей (FPGA) или другими программируемыми логическими компонентами, дискретными элементами или транзисторной логикой, дискретными аппаратными компонентами или любой их комбинацией, сконструированной для выполнения рассмотренных функций. Универсальный процессор может быть микропроцессором, но в другом случае, процессор может быть любым обычным процессором, контроллером, микроконтроллером или конечным автоматом. Процессор может также быть осуществлен как комбинация вычислительных компонентов, например комбинация DSP и микропроцессора, множество микропроцессоров, один или несколько микропроцессоров вместе с ядром DSP или любая другая такая конфигурация.

Способы или алгоритмы, описанные в связи с представленными вариантами реализации, могут быть реализованы непосредственно в аппаратных средствах, в программном модуле, выполняемом процессором, или в виде их комбинации, в виде управляемой логики, программных команд, или других указаний. Программный модуль может постоянно находиться в памяти ОЗУ, флэш-памяти, памяти ПЗУ, памяти программируемого ПЗУ, памяти ЭСППЗУ, регистрах, жестком диске, съемном диске, ПЗУ на компакт-диске или носителе данных любого другого вида, известного в данной области техники. Носитель данных может быть связан с процессором так, что процессор может считывать информацию с носителя данных, и записывать информацию на носитель данных. Альтернативно, носитель данных может быть объединен с процессором.

Приведенное описание представленных вариантов реализации призвано дать возможность любому специалисту в данной области техники выполнить или использовать настоящее изобретение. Специалистам в данной области техники будут очевидны различные модификации этих вариантов реализации и то, что рассмотренные общие принципы могут быть применены к другим вариантам реализации, без отступления от сущности или объема изобретения. Таким образом, настоящее изобретение не ограничивается приведенными вариантами реализации, но должно соответствовать полному объему, согласованному с формулой изобретения, где упоминание отдельного элемента не означает "один и только один", если это специально не оговорено, а скорее "один или несколько". Все рассмотренные структурные и функциональные эквиваленты элементов различных вариантов реализации, описанных в настоящем раскрытии, которые известны или станут известными специалистам в данной области техники, подразумеваются и охватываются приведенной формулой изобретения. Более того, ничто из раскрытого здесь не предназначено для публичного представления, независимо от того, содержится ли это раскрытие в явной форме в формуле изобретения. Никакой элемент формулы изобретения не должен рассматриваться в связи с положением 35 U.S.C. §112, шестого параграфа, если элемент явно не представлен с использованием фразы "средство для" или, в случае пункта формулы на способ, элемент не представлен с использованием фразы "этап для".

1. Регистровый файл, содержащий:множество регистров, причем каждый регистр содержит множество ячеек памяти, при этом каждый регистр, включая первую ячейку из множества ячеек памяти регистра, сконфигурирован для хранения сигнала готовности, состояние которого указывает, достоверны ли хранящиеся в регистре данные, а остальные ячейки из множества ячеек регистра сконфигурированы для хранения данных в регистре; идекодер, сконфигурированный для приема адреса целевого регистра, выбранного из множества регистров, причем декодер в ответ на сигнал готовности, сохраненный в первой ячейке памяти целевого регистра, избирательно запрещает вывод данных с целевого регистра, когда состояние сигнала готовности, сохраненного в первой ячейке памяти целевого регистра, указывает, что данные в регистре недействительны, и разрешает выводить данные целевого регистра, когда состояние сигнала готовности, сохраненного в первой ячейке памяти целевого регистра, указывает, что данные в регистре действительны.

2. Регистровый файл по п.1, в котором декодер дополнительно сконфигурирован для формирования разрешающего сигнала в ответ на принятый адрес, и для стробирования разрешающего сигнала сигналом готовности, сохраненным в первой ячейке памяти целевого регистра, и для формирования сигнала запрещения или разрешения вывода данных из целевого регистра в соответствии с тем, указывает ли состояние сигнала готовности, сохраненного в первой ячейке памяти целевого регистра, что данные в регистре действительны или недействительны.

3. Регистровый файл по п.2, в котором декодер дополнительно сконфигурирован для стробирования разрешающего сигнала сигналом из первой ячейки памяти целевого регистра посредством функции «И».

4. Регистровый файл по п.1, в котором декодер дополнительно сконфигурирован для приема второго адреса, связанного со вторым целевым регистром, и для предоставления доступа ко вторым данным, сохраненным во втором целевом регистре, когда вторые данные действительны.

5. Регистровый файл по п.1, в котором, когда в конвейере, соединенном с регистровом файлом, обнаруживается команда записи, до выполнения команды записи, данные, сохраненные в целевом регистре, определяются как недействительные.

6. Регистровый файл по п.1, дополнительно содержащий множество усилителей считывания, причем каждый усилитель из множества усилителей считывания сконфигурирован для считывания выходных данных, предоставляемых соответствующей парой дифференциальных разрядных шин, причем каждая дифференциальная разрядная шина соединена с каждой ячейкой из множества ячеек посредством соответствующего переключателя, и каждая ячейка из множества ячеек находится в одном регистре из множества регистров.

7. Регистровый файл по п.1, в котором, по меньшей мере, два из множества регистров совместно используют общий усилитель считывания.

8. Регистровый файл по п.1, в котором данные в целевом регистре недействительны, когда результат выполнения команды записи в целевой регистр не был еще сохранен в целевой регистр.

9. Регистровый файл по п.1, в котором декодер содержит множество логических устройств, связанных соответствующим образом с множеством регистров, причем декодер сконфигурирован для декодирования команды считывания, имеющей адрес целевого регистра, и передавать сигнал управления одному из множества логических устройств для указания, что к соответствующему регистру было осуществлено обращение для операции считывания.

10. Регистровый файл, содержащий:первый регистр, включающий в себя первую ячейку памяти для хранения сигнала готовности и первое множество ячеек памяти, содержащее N ячеек памяти, причем первый регистр сконфигурирован для разрешения внешнего доступа к данным, сохраненным в первом множестве ячеек памяти, в ответ на прием первого разрешающего сигнала;второй регистр, включающий в себя вторую ячейку памяти для хранения сигнала готовности и второе множество ячеек памяти, содержащее N ячеек памяти, причем второй регистр сконфигурирован для разрешения внешнего доступа к данным, сохраненным во втором множестве ячеек памяти, в ответ на прием второго разрешающего сигнала;множество усилителей считывания, причем каждый усилитель считывания сконфигурирован для считывания выходных данных из ячейки памяти первого регистра или ячейки памяти второго регистра посредством избирательных переключателей;первое логическое устройство, соединенное с первым регистром через первую числовую шину, причем первое логическое устройство сконфигурировано для предоставления первого разрешающего сигнала первому регистру через первую числовую шину в ответ на прием первого сигнала управления в первом входе первого логического устройства и в ответ на прием первого сигнала готовности на втором входе первого логического устройства;второе логическое устройство, соединенное со вторым регистром через вторую числовую шину, причем второе логическое устройство сконфигурировано для предоставления второго разрешающего сигнала второму регистру через вторую числовую шину в ответ на прием второго сигнала управления в первом входе второго логического устройства и в ответ на прием второго сигнала готовности на втором входе второго логического устройства;первый декодер, сконфигурированный для предоставления первого сигнала управления на первый вход первого логического устройства в ответ на прием первого адреса регистра, связанного с первым регистром, и дополнительно сконфигурированный для предоставления второго сигнала управления на первый вход второго логического устройства в ответ на прием второго адреса регистра, связанного со вторым регистром; ивторой декодер, сконфигурированный для обновления состояния сигнала готовности, сохраненного в первой ячейке, причем состояние сигнала готовности указывает, действительны ли или нет данные в первом регистре.

11. Регистровый файл по п.10, в котором, когда первый декодер предоставляет сигнал управления на первый вход первого логического устройства, и когда второй декодер предоставляет значение сигнала готовности на первый регистр, внешний доступ к данным, сохраненным в первом регистре разрешен.

12. Регистровый файл по п.10, в котором второй декодер сконфигурирован для предоставления сигнала готовности с состоянием, указывающим, что данные в регистре недействительны, на первую ячейку памяти для сохранения сигнала готовности, когда команда записи в первый регистр находится в конвейере команд, связанном с процессором, и в котором второй декодер сконфигурирован для предоставления сигнала готовности с состоянием, указывающим, что данные в регистре действительны, после того, как команда записи в первый регистр была выполнена.

13. Регистровый файл по п.10, в котором каждое логическое устройство дополнительно сконфигурировано для приема тактового сигнала, причем тактовый сигнал активирует одно из множества логических устройств в течение тактового цикла.

14. Регистровый файл по п.10, в котором сигнал готовности имеет состояние, указывающее, что данные в регистре действительны, причем сигнал готовности первого регистра, предоставляемый первой ячейке памяти для хранения, также предоставляется первому логическому устройству для стробирования сигнала готовности с первым разрешающим сигналом.

15. Способ доступа к регистровому файлу, имеющему множество регистров, содержащий этапы, на которых:принимают адрес первого регистра из множества регистров, причем первый регистр имеет первую ячейку памяти для хранения сигнала готовности и множество оставшихся ячеек памяти для хранения данных;сохраняют сигнал готовности, имеющий значение сигнала готовности «установка», в первой ячейке памяти первого регистра, когда данные, сохраненные в первом регистре, действительны, и сигнал готовности, имеющий значение сигнала готовности «сброс», в первой ячейке памяти первого регистра, когда данные, сохраненные в первом регистре, недействительны;отключают операцию считывания первого регистра, когда значение сигнала готовности «сброс» сохранено в первой ячейке памяти первого регистра; иразрешают операцию считывания первого регистра, когда значение сигнала готовности «установка» сохранено в первой ячейке памяти первого регистра.

16. Способ по п.15, в котором каждый из множества регистров включает в себя соответствующую первую ячейку памяти, сконфигурированную для хранения значения сигнала готовности «установка» или значения сигнала готовности «сброс», указывающего действительны ли или нет данные, сохраненные в соответствующем регистре.

17. Способ по п.16, дополнительно содержащий этап, на котором изменяют значение сигнала готовности, сохраненное в первой ячейке памяти первого регистра, с «сброс» на «установка» после того, как команда записи первого регистра была выполнена.

18. Способ по п.17, в котором значение сигнала готовности, сохраненное в первой ячейке памяти первого регистра, изменяется перед тем, как адрес для адресованного первого регистра принят.

19. Способ по п.15, дополнительно содержащий этап, на котором предоставляют данные, сохраненные в первом регистре, в трансляционную сеть, когда данные, сохраненные в первом регистре, действительны.

20. Способ по п.15, в котором данные являются недействительными, когда команда записи для записи новых данных в первый регистр находится в конвейере команд, связанном с регистровым файлом, и данные являются действительными, когда отсутствует команда записи для записи новых данных в первый регистр в конвейере команд.

21. Способ по п.15, дополнительно содержащий этапы, на которых формируют разрешающий сигнал регистра в ответ на прием адреса регистра и стробируют разрешающий сигнал регистра сигналом, сохраненным в первой ячейке памяти первого регистра.