Каскодный дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, компараторах и прецизионных операционных усилителях (ОУ) с малыми значениями э.д.с. смещения нуля). Технический результат - уменьшение напряжения смещения. Каскодный дифференциальный усилитель содержит входной дифференциальный каскад (ДК) (1), первый (2) выходной транзистор (Т), эмиттер которого связан с первым (3) токовым выходом входного ДК (1), коллектор подключен ко входу токового зеркала (4), а база соединена со вспомогательным источником напряжения (5), второй (6) выходной Т, эмиттер которого связан со вторым (7) токовым выходом входного ДК (1), а коллектор подключен к выходу токового зеркала (4) и входу (8) буферного усилителя (9), причем проводимость входного Т (10) буферного усилителя (9) совпадает с проводимостью Т (2) и Т (6). База Т (6) соединена с эмиттером Т (2). 1 з.п. ф-лы, 12 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, компараторах и прецизионных операционных усилителях (ОУ) с малыми значениями э.д.с. смещения нуля).

В современной радиоэлектронной аппаратуре находят применение дифференциальные усилители (ДУ) с существенными различными параметрами. Особое место занимают ДУ с каскодной архитектурой (КДУ), характеризующиеся наибольшей широкополосностью. Предлагаемое изобретение относится к данному типу ДУ.

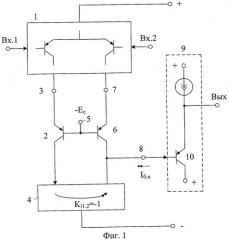

Наиболее близкой по технической сущности к заявляемому устройству является классическая схема КДУ, фиг.1, представленная в виде промежуточного каскада КДУ по патентной заявке США №2008/0136522, которая присутствует в ряде других патентов [1-10].

Существенный недостаток известного КДУ, фиг.1, состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля Uсм.

Основная цель предлагаемого изобретения состоит в уменьшении Uсм.

Поставленная цель достигается тем, что в каскодном дифференциальном усилителе, фиг.1, содержащем входной дифференциальный каскад 1, первый 2 выходной транзистор, эмиттер которого связан с первым 3 токовым выходом входного дифференциального каскада 1, коллектор подключен ко входу токового зеркала 4, а база соединена со вспомогательным источником напряжения 5, второй 6 выходной транзистор, эмиттер которого связан со вторым 7 токовым выходом входного дифференциального каскада 1, а коллектор подключен к выходу токового зеркала 4 и входу 8 буферного усилителя 9, причем проводимость входного транзистора 10 буферного усилителя 9 совпадает с проводимостью первого 2 и второго 6 выходных транзисторов, предусмотрены новые элементы и связи - база второго 6 выходного транзистора соединена с эмиттером первого 2 выходного транзистора.

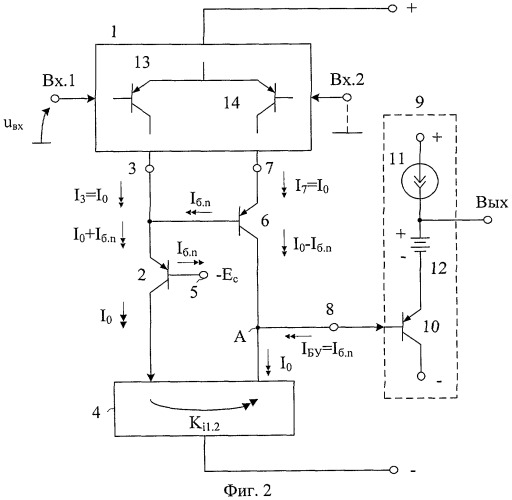

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения, реализованная на р-n-р транзисторах 2, 6, 10.

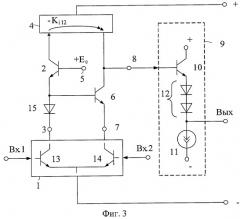

На фиг.3 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения, реализованная на n-р-n транзисторах 2, 6, 10.

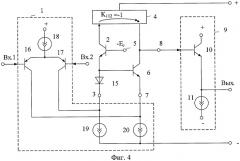

На фиг.4, соответствующей п.1 формулы изобретения, в качестве транзисторов 2, 6 и 10 используются n-p-n транзисторы, а во входном дифференциальном каскаде 1 - р-n-р транзисторы 16 и 17.

На фиг.5 представлена схема усилителя-прототипа в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.6 представлена схема заявляемого устройства в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» для случая, когда в схеме используется идеальное токовое зеркало.

На фиг.7 приведены графики температурной зависимости напряжения смещения нуля схем на фиг.5 и фиг.6.

На фиг.8 представлена схема прототипа - фиг.1 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» для случая, когда в ней используется реальное токовое зеркало Вильсона.

На фиг.9 представлена схема заявляемого устройства для случая, когда в ней используется реальное токовое зеркало Вильсона.

На фиг.10 приведены графики температурной зависимости напряжения смещения нуля схем на фиг.8 и фиг.9.

На фиг.11 показана схема на фиг.4 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП Hi ill «Пульсар», а на фиг.12 - схема усилителя-прототипа, соответствующая схеме на фиг.1.

Каскодный дифференциальный усилитель, фиг.2, содержит входной дифференциальный каскад 1, первый 2 выходной транзистор, эмиттер которого связан с первым 3 токовым выходом входного дифференциального каскада 1, коллектор подключен ко входу токового зеркала 4, а база соединена со вспомогательным источником напряжения 5, второй 6 выходной транзистор, эмиттер которого связан со вторым 7 токовым выходом входного дифференциального каскада 1, а коллектор подключен к выходу токового зеркала 4 и входу 8 буферного усилителя 9, причем проводимость входного транзистора 10 буферного усилителя 9 совпадает с проводимостью первого 2 и второго 6 выходных транзисторов. База второго 6 выходного транзистора соединена с эмиттером первого 2 выходного транзистора.

В схеме на фиг.3, а также на фиг.4 в соответствии с п.2 формулы изобретения эмиттер первого 2 выходного транзистора связан с первым 3 токовым выходом входного дифференциального каскада 1 через вспомогательный двухполюсник (p-n переход) 15.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля Uсм в схеме на фиг.2.

На основе первого закона Кирхгофа можно записать следующие уравнения для коллекторных (Iк) и эмиттерных (Iэ) токов транзисторов 2 и 6, а также входного (Iвх.4) и выходного (Iвых.4) токов токового зеркала 4:

где Iб.р - ток базы n-p-n транзисторов 2, 6, 10.

С учетом уравнений (1)-(6) находим, что в узле «А» происходит взаимная компенсация базовых токов однотипных транзисторов 6, 2, 10:

Как следствие, это не требует смещения нуля ДУ на величину напряжения Uсм, подача которого на входы Bx.(+)1, Bx.(-)2 компенсирует разностный ток Iр в узле «А». Таким образом, в заявляемом устройстве уменьшается систематическая составляющая Uсм, обусловленная конечной величиной β транзисторов и его радиационной или температурной зависимостью. Как следствие, это уменьшает Uсм, так как разностный ток Iр в узле «А» создает Uсм, зависящее от крутизны преобразования входного напряжения uвх ДУ, фиг.2, в выходной ток узла «А»

где rэ13=rэ14 - сопротивления эмиттерных переходов входных транзисторов 13 и 14 дифференциального каскада 1.

Поэтому для схемы на фиг.2

где φТ=26 мВ - температурный потенциал.

В ДУ-прототипе Ip≠0 (Iр=Iб.n), поэтому здесь систематическая составляющая Uсм получается на порядок больше (Uсм=-652 мкВ), чем в заявляемой схеме (Uсм=25 мкВ).

Компьютерное моделирование схем на фиг.5 и фиг.6, фиг.8 и фиг.9, фиг.11 и фиг.12 подтверждает данные теоретические выводы.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №4.801.893, fig.6a.

2. Патентная заявка США 2007/0115056, fig.1.

3. А.с. СССР №922698.

4. Патент США №4.232.273.

5. Патент Японии №53-35352.

6. Патент Японии №1264806.

7. Патентная заявка США 2007/0188191.

8. Патентная заявка США 2007/0188191.

9. Патент Франции №2227574.

10. Патент США №3.482.177 fig.5.

1. Каскодный дифференциальный усилитель, содержащий входной дифференциальный каскад (1), первый (2) выходной транзистор, эмиттер которого связан с первым (3) токовым выходом входного дифференциального каскада (1), коллектор подключен ко входу токового зеркала (4), а база соединена со вспомогательным источником напряжения (5), второй (6) выходной транзистор, эмиттер которого связан со вторым (7) токовым выходом входного дифференциального каскада (1), а коллектор подключен к выходу токового зеркала (4) и входу (8) буферного усилителя (9), причем проводимость входного транзистора (10) буферного усилителя (9) совпадает с проводимостью первого (2) и второго (6) выходных транзисторов, отличающийся тем, что база второго (6) выходного транзистора соединена с эмиттером первого (2) выходного транзистора.

2. Устройство по п.1, отличающееся тем, что эмиттер первого (2) выходного транзистора связан с первым (3) токовым выходом входного дифференциального каскада (1) через вспомогательный двухполюсник (15).