Каскодный дифференциальный усилитель с малым напряжением смещения нуля

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в компараторах и прецизионных операционных усилителях (ОУ) с малыми значениями эдс смещения нуля). Технический результат: уменьшение абсолютного значения напряжения смещения и его температурного дрейфа. Каскодный дифференциальный усилитель содержит входной дифференциальный каскад (ДК) (1) с первым (2) и вторым (3) токовыми выходами, первый (4) и второй (5) выходные транзисторы (Т) с объединенными базами, вспомогательный источник напряжения питания (6), первое токовое зеркало (ТЗ) (7), вход которого соединен с коллектором Т (4), выход - подключен к коллектору Т (5) и входу (8) буферного усилителя (9), содержащего входной Т (10), причем тип проводимости входного Т (10) буферного усилителя (9) идентичен типу проводимости Т (4) и Т (5), эмиттер Т (4) связан с первым (2) выходом ДК (1), а эмиттер Т (5) соединен со вторым (3) токовым выходом ДК (1). В схему введено второе ТЗ (16), вход которого связан с базами Т (4) и Т (5), выход - подключен к эмиттеру Т (5), а общий узел - связан со вспомогательным источником напряжения питания (6). 8 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в компараторах и прецизионных операционных усилителях (ОУ) с малыми значениями эдс смещения нуля).

В современной радиоэлектронной аппаратуре находят применение дифференциальные усилители (ДУ) с существенно различными параметрами. Особое место занимают каскодные ДУ с простейшей двухкаскадной архитектурой, содержащие небольшое число элементов и характеризующиеся повышенным частотным диапазоном [1-12]. На их основе выполняются, например, различные классы селективных цепей, где число маломощных усилителей может измеряться десятками единиц. Предлагаемое изобретение относится к данному типу ДУ.

В качестве прототипа авторами выбран каскодный дифференциальный усилитель, входящий в структуру повторителя напряжения (стабилизатора) по патенту Франции 2.227.574 (схема fig.1 при использовании следующих сочетаний функциональных узлов: fig.3с и fig.4a). Это же техническое решение запатентовано еще в трех странах NL, DE, JP [12].

Существенный недостаток известного ДУ фиг.1 состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм), зависящей от свойств его архитектуры.

Основная цель предлагаемого изобретения состоит в уменьшении абсолютного значения Uсм и его температурного дрейфа.

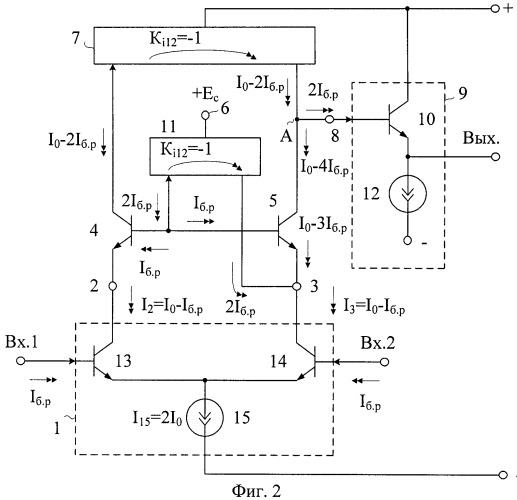

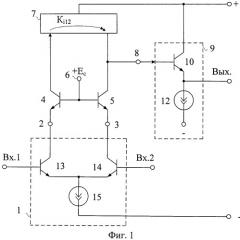

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первый 4 и второй 5 выходные транзисторы с объединенными базами, вспомогательный источник напряжения питания 6, первое токовое зеркало 7, вход которого соединен с коллектором первого 4 выходного транзистора, выход - подключен к коллектору второго 5 выходного транзистора и входу 8 буферного усилителя 9, содержащего входной 10 транзистор, причем тип проводимости входного 10 транзистора буферного усилителя 9 идентичен типу проводимости первого 4 и второго 5 выходных транзисторов, эмиттер первого 4 выходного транзистора связан с первым 2 токовым выходом входного дифференциального каскада, а эмиттер второго 5 выходного транзистора соединен со вторым 3 токовым выходом входного дифференциального каскада 1, предусмотрены новые элементы и связи - в схему введено второе токовое зеркало 16, вход которого связан с базами первого 4 и второго 5 выходных транзисторов, выход - подключен к эмиттеру второго 5 выходного транзистора, а общий узел - связан со вспомогательным источником напряжения питания 6.

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с формулой изобретения.

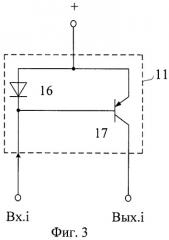

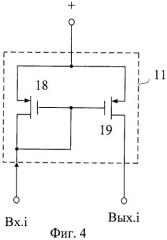

На фиг.3 и 4 показаны частные случаи выполнения токового зеркала 11.

На фиг.5 приведена схема заявляемого устройства для случая, когда в ней используется так называемый «перегнутый» каскод (элементы 4, 5, 7, 10, 12).

В схеме фиг.6, соответствующей фиг.2, введен дополнительный транзистор терморадиационной компенсации 26.

На фиг.7 показаны схемы дифференциального усилителя - прототипа (левая часть) и заявляемого ДУ (правая часть) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.8 приведены температурные зависимости напряжения смещения нуля схем фиг.7.

Каскодный дифференциальный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, первый 4 и второй 5 выходные транзисторы с объединенными базами, вспомогательный источник напряжения питания 6, первое токовое зеркало 7, вход которого соединен с коллектором первого 4 выходного транзистора, выход - подключен к коллектору второго 5 выходного транзистора и входу 8 буферного усилителя 9, содержащего входной 10 транзистор, причем тип проводимости входного 10 транзистора буферного усилителя 9 идентичен типу проводимости первого 4 и второго 5 выходных транзисторов, эмиттер первого 4 выходного транзистора связан с первым 2 токовым выходом входного дифференциального каскада, а эмиттер второго 5 выходного транзистора соединен со вторым 3 токовым выходом входного дифференциального каскада 1. В схему введено второе токовое зеркало 16, вход которого связан с базами первого 4 и второго 5 выходных транзисторов, выход - подключен к эмиттеру второго 5 выходного транзистора, а общий узел - связан со вспомогательным источником напряжения питания 6.

В частном случае буферный усилитель 9 в схеме фиг.2 содержит токостабилизирующий двухполюсник 12, а входной параллельно-балансный каскад 1 реализован на транзисторах 13, 14 и двухполюснике 15.

Токовые зеркала 11 на фиг.3 и 4 выполнены на элементах 16, 17, 18 и 19.

В схеме фиг.5 входной параллельно-балансный каскад 1 реализован на транзисторах 20 и 21, а также двухполюсниках 22, 23 и 24, а в буферный усилитель 9 введена цепь согласования потенциалов 25.

В схеме фиг.6 введен транзистор терморадиационной компенсации 26, имеющий (так же как и транзистор 17 токового зеркала 11) р-n переход на подложку 27, идентичный р-n переходу 28 транзистора 17.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля UCM в схеме фиг.2, т.е. зависящие от схемотехники ДУ.

Если ток двухполюсника 15 равен величине 2I0, то токи выходов 2 и 3, входной (Iвх.7) и выходной (IВых.7) токи подсхемы 7:

где Iб.р=Iэ.i/βi - ток базы n-p-n транзисторов 4, 5, 13, 14, 10 при эмиттерном токе Iэ.i=I0;

βi - коэффициент усиления по току базы n-p-n транзистора.

Как следствие, разность токов в узле «А» при его коротком замыкании на эквипотенциальную общую шину

где IБУ=2Iб.р - ток базы n-p-n транзистора 10 буферного усилителя 9. Подставляя (3)÷(6) в (7) находим, что разностный ток, определяющий Uсм,

Как следствие, при Iр=0 не требуется смещения нуля ДУ1 фиг.2 на величину Uсм, подача которого на его входы Вх.(+)1, Вх.(-)2 компенсирует разностный ток Iр в узле «А».

Таким образом, в заявляемом устройстве уменьшается систематическая составляющая Uсм, обусловленная конечной величиной β транзисторов и его радиационной (или температурной) зависимостью. Как следствие, это уменьшает Uсм, так как разностный ток Iр в узле «А» создает Uсм, зависящее от крутизны преобразования входного дифференциального напряжения Uвх ДУ в выходной ток узла «А»:

где rэ14=rэ13 - сопротивления эмиттерных переходов входных

транзисторов 14 и 13 дифференциального каскада 1.

Поэтому для схемы фиг.2

где φт=26 мВ - температурный потенциал.

В ДУ-прототипе фиг.1 Iр≠0, поэтому здесь систематическая составляющая Uсм.1 получается на порядок больше (UCM.1=-1,17 мВ), чем в заявляемой схеме (UCM.1 = 43 мкВ, (фиг.8)).

Компьютерное моделирование схем фиг.3 подтверждает (фиг.4) данные теоретические выводы.

Если необходимо обеспечить симметрию амплитуд положительных и отрицательных полуволн выходного напряжения ДУ фиг.7, то следует ввести вторую цепь смещения потенциалов V4.

Для минимизации Uсм.1 при повышенных температурах (t°>80°C) в схеме фиг.6 предусмотрен транзистор 26, который находится в закрытом состоянии. Однако ток через его р-n переход на подложку 27, который существенно возрастает на высоких температурах (или при радиационных воздействиях), компенсирует соответствующий ток на подложку через р-n переход 28 транзистора 17. Это существенно уменьшает производную dUсм/dT при t°>80°C.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока.

Источники информации

1. Патент США №6.114.234.

2. Патент США №5.091.701, fig.1.

3. Патент США №5.140.280.

4. Патент США №5.786.729.

5. Патент США №6.448.853.

6. Патент США №4.390.850.

7. Патент США №5.327.100 fig.2.

8. Патент США №6.4383.382 fig.2, fig.1.

9. Патент США №5.374.897.

10. Патент США №6.529.076.

11. Патент США №5.627.495 fig.2.

12. Патент Франции №2.227.574 fig.1, fig.3с, fig.4а.

Каскодный дифференциальный усилитель с малым напряжением смещения нуля, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, первый (4) и второй (5) выходные транзисторы с объединенными базами, вспомогательный источник напряжения питания (6), первое токовое зеркало (7), вход которого соединен с коллектором первого (4) выходного транзистора, выход подключен к коллектору второго (5) выходного транзистора и входу (8) буферного усилителя (9), содержащего входной (10) транзистор, причем тип проводимости входного (10) транзистора буферного усилителя (9) идентичен типу проводимости первого (4) и второго (5) выходных транзисторов, эмиттер первого (4) выходного транзистора связан с первым (2) токовым выходом входного дифференциального каскада, а эмиттер второго (5) выходного транзистора соединен со вторым (3) токовым выходом входного дифференциального каскада (1), отличающийся тем, что в схему введено второе токовое зеркало (16), вход которого связан с базами первого (4) и второго (5) выходных транзисторов, выход подключен к эмиттеру второго (5) выходного транзистора, а общий узел связан со вспомогательным источником напряжения питания (6).