Устройство обмена данными между четырехфазным самосинхронным и синхронным параллельным интерфейсом

Иллюстрации

Показать всеИзобретение относится к устройствам обработки цифровых данных с помощью электрических устройств, в частности к соединительным устройствам передачи информации для функциональных элементов, и может использоваться при построении самосинхронных цифровых вычислительных устройств и систем обработки информации на базе микросхем большой и сверхбольшой степени интеграции. Достигаемый технический результат - обеспечение двусторонней взаимосвязи цифровых микроэлектронных устройств с синхронным параллельным интерфейсом и самосинхронного с четырехфазным интерфейсом с возможностью сигнализации готовности принятия данных. Устройство состоит из канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный и канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный. 5 ил.

Реферат

Изобретение относится к устройствам обработки цифровых данных с помощью электрических устройств, в частности к соединительным устройствам передачи информации для функциональных элементов, и является устройством сопряжения самосинхронного и синхронного интерфейсов цифровой техники, и может использоваться при построении самосинхронных цифровых вычислительных устройств и систем цифровой обработки информации на базе микросхем сверхбольшой степени интеграции.

При разработке интегральных микросхем сверхбольшой степени интеграции (СБИС), например систем на кристалле, одной из важнейших задач является сопряжение входящих в них функциональных блоков. В современных СБИС совместно используются цифровые устройства, работающие по синхронному принципу, и устройства с самосинхронизацией [2]. Использование четырехфазных интерфейсов в функциональных блоках с самосинхронизацией является наиболее эффективным с точки зрения конструкции и энергопотребления благодаря уменьшению разрядности шин данных (относительно интерфейса с парафазным представлением данных) и количества элементов в схеме сопряжения интерфейсов. Унификация внутренних межблочных интерфейсов позволяет существенно улучшить временные и стоимостные показатели разработки.

Существующие в настоящее время устройства сопряжения синхронных параллельных интерфейсов [1] и интерфейсов устройств с самосинхронизацией являются однонаправленными и не могут являться универсальными, так как не содержат сигналов обратной связи, сигнализирующих о готовности к получению данных блоком-приемником, что является их основным недостатком.

Известно устройство «SYNCHRONOUS INTERFACE TO A SELF-TIMED MEMORY ARRAY» (патент US 006,601,293 A от 09.05.2000) того же назначения, что и предлагаемое, но не имеющее с ним общих признаков, выбранное за прототип и состоящее из канала данных, канала адреса и канала синхронизации, причем канал данных состоит из идентичных подканалов, каждый из которых содержит буфер входных данных (Input Buffer), соединенный со входом данных первой защелки (1st Stage Transparent Latches), выход которой подсоединен со входом данных первого тактируемого триггера (2-nd Stage Pulsed Latches) и первому инвертору, выход которого подсоединен ко входу данных второго тактируемого триггера; канал адреса состоит из последовательно соединенных входного буфера строба адреса (Input Buffer), второй защелки (Transparent Latches) и третьего тактируемого триггера; канал синхронизации состоит из последовательно соединенных буфера тактового сигнала (Input Buffer), настраиваемой линии задержки (Setup-Hold Adj. Delay) и последовательно соединенных второго и третьего инвертора, причем выход второго инвертора соединен со входами разрешения первой и второй защелки, выход второго инвертора - с тактовым входом первого, второго и третьего, а выход второй защелки - со входами разрешения первого и второго тактируемых триггеров.

Основным недостатком рассмотренного устройства является то, что в нем предусмотрена передача информации только в одном направлении, от синхронного интерфейса к самосинхронному; другим недостатком является отсутствие сигналов обратной связи сигнализирующих о готовности к получению данных блоком-приемником; не ставится и не решается задача сопряжения синхронного и четырехфазного самосинхронного интерфейсов.

Сущностью изобретения является устройство обмена данными для сопряжения цифровых функциональных блоков СБИС с четырехфазным интерфейсом с самосинхронизацией [2] и с синхронным параллельным интерфейсом, предназначенное для передачи информации между унифицированными микроэлектронными устройствами, использующими различные протоколы передачи данных внутри СБИС, и позволяющее сигнализировать передающему блоку о возможности принять данные приемным.

Техническим результатом является обеспечение двусторонней взаимосвязи цифровых микроэлектронных устройств с синхронным параллельным интерфейсом и самосинхронным четырехфазным интерфейсом с возможностью сигнализации готовности принятия данных внутри СБИС.

Сопоставительный анализ с прототипом показывает, что предлагаемое устройство отличается наличием новых элементов: канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный, и состоящий из схемы формирования сигнала ПОДТВЕРЖДЕНИЕ, схемы формирования сигнала РАЗРЕШЕНИЕ и схемы передачи данных, причем

схема формирования сигнала ПОДТВЕРЖДЕНИЕ состоит из первого буфера с третьим состоянием, соединенного с первым и вторым входом первого элемента «И-НЕ», выход которого соединен с тактовым входом первого D-триггера, ко входу сброса которого подсоединен выход третьего элемента «И», а неинвертированный выход которого соединен со входом первого формирователя импульса, выход которого соединен с входом первого элемента «НЕ», соединенного с первым входом второго элемента «И-НЕ», выход которого соединен со входом установки первого RS-триггера, неинвертированный выход которого соединен со входом данных второго буфера с третьим состоянием, со вторым входом третьего элемента «И», выход которого соединен со входом сброса первого D-триггера, а инверсный выход первого RS-триггера соединен со вторым входом первого элемента «И», выход которого соединен со входом сброса второго D-триггера, а первый вход объединен со вторым входом второго элемента «И-НЕ» и вторым входом второго элемента «И»; первого элемента «И», выход которого соединен со входом сброса второго D-триггера, неинвертированный выход которого соединен со входом второго формирователя импульса, соединенного с первым входом второго элемента «И», выход которого соединен со входом сброса первого RS-триггера, причем выход первого буфера с третьим состоянием соединен со входом данных второго D-триггера, а вход установки объединен со входами данных и установки первого D-триггера и с лог. «1»;

схема формирования сигнала РАЗРЕШЕНИЕ состоит из третьего буфера с третьим состоянием, соединенного со входом данных третьего D-триггера, неинвертированный выход которого соединен со входом данных четвертого буфера с третьим состоянием, со вторым входом четвертого элемента «И» и со входом данных четвертого D-триггера, инверсный выход которого соединен со вторым входом пятого элемента «И», вход установки - с лог. «1», а вход сброса - с выходом четвертого элемента «И», причем первый вход пятого элемента «И» объединен со вторым входом четвертого элемента «И», а выход соединен со входом сброса третьего D-триггера, вход установки которого соединен с лог. «1»;

схема передачи данных состоит из пятого буфера с третьим состоянием, соединенного со входом данных регистра, выход которого соединен со входом данных шестого буфера с третьим состоянием,

а канал передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный, выход которого соединен со входом, а вход - с выходом канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный, состоит из седьмого буфера с третьим состоянием, выход которого соединен со вторым входом первого элемента «ИЛИ» и с третьим формирователем импульса, соединенным с входом второго элемента «НЕ», выход которого соединен с первым входом третьего элемента «И-НЕ», а выход соединен со входом установки второго RS-триггера, выход которого соединен с первым входом первого элемента «ИЛИ» и входом данных восьмого буфера с третьим состоянием; девятого буфера с третьим состоянием, а выход соединен со входом данных пятого D-триггера, сигнал установки - с лог. «1», а неинвертированный выход - с четвертым формирователем импульса, выход которого соединен с первым входом пятого элемента «И», соединного со входом сброса второго RS-триггера; третьего элемента «НЕ», соединенного с управляющим входом одиннадцатого буфера с третьим состоянием и управляющими входами седьмого, восьмого, девятого и десятого буферов с третьим состоянием.

Следовательно, устройство удовлетворяет критерию «новизна».

Сравнение с другими техническими решениями показывает, что в устройстве присутствуют элементы, обеспечивающие двустороннюю взаимосвязь устройства с синхронным параллельным интерфейсом и самосинхронного устройства с четырехфазным интерфейсом с возможностью сигнализации готовности принятия данных.

Изобретение поясняется чертежами:

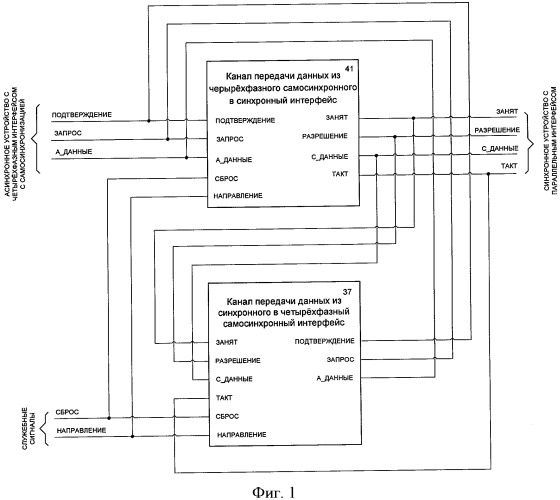

фиг.1 - структурная схема устройства обмена данными между четырехфазным самосинхронным и синхронным параллельным интерфейсом;

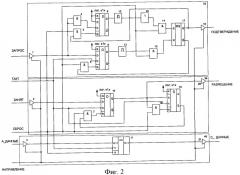

фиг.2 - функциональная схема канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный;

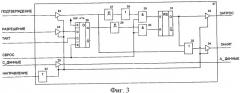

фиг.3 - функциональная схема канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный;

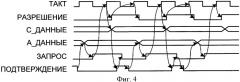

фиг.4 - временная диаграмма, поясняющая принцип работы устройства в режиме передачи данных из четырехфазного с самосинхронизацией в параллельный синхронный интерфейс;

фиг.5 - временная диаграмма, поясняющая принцип работы устройства в режиме передачи данных из синхронного параллельного в четырехфазный интерфейс с самосинхронизацией.

Устройство обмена данными между четырехфазным самосинхронным и синхронным параллельным интерфейсом (фиг.1) состоит из канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный 41, состоящего из схемы формирования сигнала ПОДТВЕРЖДЕНИЕ 35, схемы формирования сигнала РАЗРЕШЕНИЕ 36 и схемы передачи данных 40 (фиг.2), и канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный 37 (фиг.3), выход которого соединен со входом, а вход - с выходом канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный 41, причем

схема формирования сигнала ПОДТВЕРЖДЕНИЕ 35 (фиг.2) состоит из первого буфера с третьим состоянием 1, вход которого является входом ЗАПРОС, соединенного с первым и вторым входом первого элемента «И-НЕ» 4, выход которого соединен с тактовым входом С первого D-триггера 8, ко входу сброса R которого подсоединен выход третьего элемента «И» 5, а неинвертированный выход Q соединен со входом первого формирователя импульса 12, выход которого соединен с входом первого элемента «НЕ» 38, соединенного с первым входом второго элемента «И-НЕ» 14, выход которого соединен со входом установки S первого RS-триггера 17, неинвертированный выход Q которого соединен со входом данных второго буфера с третьим состоянием 19, выход которого является выходом ПОДТВЕРЖДЕНИЕ, со вторым входом третьего элемента «И» 5, выход которого соединен со входом сброса R первого D-триггера 8, а первый вход объединен со входом СБРОС, а инверсный выход первого RS-триггера 17 соединен со вторым входом первого элемента «И» 6, выход которого соединен со входом сброса R второго D-триггера 9, а первый вход объединен со вторым входом второго элемента «И-НЕ» 14, вторым входом второго элемента «И» 15 и входом СБРОС; первого элемента «И» 6, выход которого соединен со входом сброса R второго D-триггера 9, неинвертированный выход Q которого соединен со входом второго формирователя импульса 13, соединенного с первым входом второго элемента «И» 15, выход которого соединен со входом сброса R первого RS-триггера 17, причем выход первого буфера с третьим состоянием 1 соединен со входом данных D второго D-триггера 9, тактовый вход С которого объединен с сигналом ТАКТ, а вход установки S объединен со входами данных D и установки S первого D-триггера 8 и с лог. «1», а управляющие входы первого 1 и второго 19 буферов с третьим состоянием объединены со входом НАПРАВЛЕНИЕ;

схема формирования сигнала РАЗРЕШЕНИЕ 36 (фиг.2) состоит из третьего буфера с третьим состоянием 2, вход которого является входом ЗАНЯТ, соединенного со входом данных D третьего D-триггера 10, неинвертированный выход Q которого соединен со входом данных четвертого буфера с третьим состоянием 20, выход которого является выходом РАЗРЕШЕНИЕ, со вторым входом четвертого элемента «И» 16 и со входом данных D четвертого D-триггера 18, инверсный выход которого соединен со вторым входом пятого элемента «И» 7, вход установки S соединен с лог.«1», тактовый вход С объединен со входом ТАКТ, а вход сброса R соединен с выходом четвертого элемента «И» 16, причем первый вход пятого элемента «И» 7 объединен со вторым входом четвертого элемента «И» 16 и со входом СБРОС, а выход соединен со входом сброса R третьего D-триггера 10, тактовый вход С которого объединен со входом ТАКТ, вход установки которого S соединен с лог. «1»; управляющие входы третьего 2 и четвертого 20 буферов с третьим состоянием объединены и соединены со входом НАПРАВЛЕНИЕ;

схема передачи данных 40 (фиг.2) состоит из пятого буфера с третьим состоянием 3, вход данных которого объединен со входом А_ДАННЫЕ, соединенного со входом данных D регистра 11, тактовый вход С которого объединен с сигналом ТАКТ, вход сброса объединен со входом СБРОС, а выход Q соединен со входом данных шестого буфера с третьим состоянием 21, выход которого является выходом С_ДАННЫЕ, причем управляющие входы пятого 3 и шестого 21 буферов с третьим состоянием соединены со входом НАПРАВЛЕНИЕ,

а канал передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный 37 (фиг.3) состоит из седьмого буфера с третьим состоянием 23, вход данных которого объединен со входом ПОДТВЕРЖДЕНИЕ, а выход соединен со вторым входом первого элемента «ИЛИ» 32 и с третьим формирователем импульса 27, соединенным с входом второго элемента «НЕ» 39, выход которого соединен с первым входом третьего элемента «И-НЕ» 29, второй вход соединен со входом СБРОС, а выход - со входом установки S второго RS-триггера 31, выход которого соединен с первым входом первого элемента «ИЛИ» 32 и входом данных восьмого буфера с третьим состоянием 33, выход которого является выходом ЗАПРОС; девятого буфера с третьим состоянием 24, вход данных которого является входом РАЗРЕШЕНИЕ, а выход соединен со входом данных D пятого D-триггера 26, тактовый вход C которого соединен со входом ТАКТ, сигнал установки S соединен с лог. «1», вход сброса R - со входом СБРОС, а неинвертированный выход Q - с четвертым формирователем импульса 28, выход которого соединен с первым входом пятого элемента «И» 30, второй вход которого соединен с входом СБРОС, а выход соединен со входом сброса R второго RS-триггера 31; третьего элемента «НЕ» 22, вход которого является входом НАПРАВЛЕНИЕ, соединенного с управляющим входом одиннадцатого буфера с третьим состоянием 25, вход которого является входом С_ДАННЫЕ, а выход - выходом А_ДАННЫЕ, и управляющими входами седьмого 23, восьмого 33, девятого 24 и десятого 34 буферов с третьим состоянием соответственно.

Устройство работает следующим образом.

На входе НАПРАВЛЕНИЕ устройства устанавливается логический сигнал, определяющий режим (направление) передачи данных.

В режиме передачи данных от четырехфазного интерфейса с самосинхронизацией к синхронному параллельному, при лог. «0» на входе НАПРАВЛЕНИЕ схема формирования сигнала ПОДТВЕРЖДЕНИЕ 35 через первый буфер с третьим состоянием 1 и второй буфер с третьим состоянием 19, схема формирования сигнала РАЗРЕШЕНИЕ 36 через третий буфер с третьим состоянием 2 и четвертый буфер с третьим состоянием 20 и схема передачи данных 40 через пятый буфер с третьим состоянием 3 и шестой буфер с третьим состоянием 21 подключаются к входам и выходам устройства. Канал передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный 37 отключен от входов и выходов устройства с помощью седьмого 23, восьмого 33, девятого 24, десятого 34 и одиннадцатого 25 буферов с третьим состоянием. По отрицательному фронту сигнала ПОДТВЕРЖДЕНИЕ на вход устройства А_ДАННЫЕ подаются передаваемые данные (фиг.4). После подачи данных сигнал на выходе ЗАПРОС устанавливается в лог. «1», устройство переходит в режим ожидания прихода переднего фронта тактового сигнала ТАКТ. По переднему фронту тактового сигнала на входе ТАКТ на выходе схемы С_ДАННЫЕ устанавливается логическая величина, снятая с входа А_ДАННЫЕ, на выходе РАЗРЕШЕНИЕ устанавливается лог. «1», удерживающаяся в течение периода тактового сигнала. После установления нового значения на выходе устройства С_ДАННЫЕ, на выходе ПОДТВЕРЖДЕНИЕ устанавливается лог.«1», после чего устройство ожидает установления на входе ЗАПРОС лог. «0»; при наступлении данного события на выходе ПОДТВЕРЖДЕНИЕ устанавливается лог. «0». Изменение уровня сигнала на выходе ПОДТВЕРЖДЕНИЕ с лог. «1» на лог. «0» сигнализирует о готовности устройства принять и передать новое данное.

После установления сигнала на входе ЗАПРОС в лог. «1» по переднему фронту тактового сигнала на входе ТАКТ на прямом выходе Q второго D-триггера 9 появляется лог. «1». При изменении входного сигнала с лог. «0» на лог. «1» первый формирователь импульса 13 формирует импульс на выходе, который через второй элемент «И» 15 подается на вход сброса R первого RS-триггера 17 и через первый элемент «НЕ» 38 - на второй элемент «И-НЕ» 14, на выходе которого устанавливается лог. «0». В соответствии со стандартной таблицей истинности первый RS-триггер 17 устанавливается на прямом выходе Q в состояние лог. «1», а на инверсном - в лог. «0». С инверсного выхода RS-триггера 17 сигнал подается через элемент «И» 6 на вход сброса RD-триггера 9, на прямом выходе Q которого формируется значение лог. «0», с прямого Q - через элемент«И» 5 на вход сброса RD-триггера 8.

После изменения уровня сигнала на входе ЗАПРОС с лог. «1» на лог. «0» на выходе первого элемента «И-НЕ» 4 происходит изменение сигнала с лог. «0» на лог. «1». По образовавшемуся в результате перехода положительному фронту на прямом выходе Q первого D-триггера 8 устанавливается лог. «1». После изменения сигнала на входе первого формирователя импульса 12 с лог. «0» до лог. «1» на выходе последнего формируется импульс, поступающий на вход второго элемента «И-НЕ» 14. В соответствии со стандартной таблицей истинности на прямом выходе Q первого RS-триггера 17 устанавливается сигнал лог. «0», а на инверсном - лог. «1», который поступает через первый элемент «И» 6 на вход сброса R второго D-триггера 9, а сигнал с прямого выхода - через третий элемент «И» 5 на вход сброса R первого D-триггера 8, на прямом выходе Q устанавливается лог. «0».

Сигнал со входа ЗАНЯТ поступает через третий буфер с третьим состоянием 2 на вход D третьего D-триггера 10. При установке лог. «1» на входе D по положительному фронту тактового сигнала со входа ТАКТ на прямом выходе Q третьего D-триггера 10 и выходе устройства РАЗРЕШЕНИЕ устанавливается лог. «1». После установки лог. «1» на входе D четвертого D-триггера 18 на его инверсном выходе по положительному фронту тактового сигнала ТАКТ устанавливается сигнал лог. «0», передающийся через пятый элемент «И» 7 на вход сброса R третьего D-триггера 10, на прямом выходе Q которого устанавливается лог. «0».

Сигнал со входа А_ДАННЫЕ через пятый буфер с третьим состоянием 3 поступает на вход D регистра 11 и по положительному фронту тактового сигнала ТАКТ через шестой буфер с третьим состоянием 21 передается на выход С_ДАННЫЕ устройства.

В режиме передачи данных от синхронного параллельного интерфейса к четырехфазному с самосинхронизацией, при лог. «1» на входе НАПРАВЛЕНИЕ, канал передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный 37 подключается к входам и выходам устройства с помощью седьмого 23, восьмого 33, девятого 24, десятого 34 и одиннадцатого 25 буферов с третьим состоянием. При лог. «0» на входе ПОДТВЕРЖДЕНИЕ и при лог. «1» на входах РАЗРЕШЕНИЕ по положительному фронту тактового сигнала ТАКТ на выходах ЗАНЯТ и ЗАПРОС устанавливаются лог. «1» (фиг.5). Когда на выходе ЗАНЯТ устанавливается лог. «1», устройство не принимает новых данных для передачи. Когда на выходе ЗАПРОС установилось лог. «1», устройство ожидает установления на входе ПОДТВЕРЖДЕНИЕ лог. «1», после чего на выходе ЗАПРОС устанавливается лог. «1», а на выходе ЗАНЯТ устанавливается лог. «0», что сигнализирует о готовности устройства принять новые данные для последующей передачи. На выход устройства А_ДАННЫЕ входные сигналы идут напрямую.

В момент установления лог. «0» на входе СБРОС D-триггеры: первый 8, второй 9, третий 10, четвертый 18, пятый 26, и RS-триггеры: первый 17, второй 31, а также регистр 11 устанавливаются в исходное состояние; при этом на их неинвертирующих выходах устанавливаются лог. «0».

После установки на входе сигнала РАЗРЕШЕНИЕ в лог. «1», который поступает через девятый буфер с третьим состоянием 24 на вход D пятого D-триггера 26, после прихода переднего фронта тактового сигнала со входа ТАКТ, на прямом выходе Q которого устанавливается сигнал лог. «1», поступающий на вход четвертого формирователя импульса 28, на выходе которого появляется импульс, поступающий через пятый элемент «И» 30 на вход сброса R второго RS-триггера 31, после чего на его прямом выходе Q устанавливается сигнал лог. «1», поступающий через восьмой буфер с третьим состоянием 33 на выход ЗАПРОС устройства.

После установления на входе ПОДТВЕРЖДЕНИЕ устройства лог. «1», поступающего через седьмой буфер с третьим состоянием 23 на вход третьего формирователя импульса 27, на выходе последнего формируется импульс, поступающий через второй элемент «НЕ» 39 на вход третьего элемента «И-НЕ» 29 и с его выхода - на вход установки S второго RS-триггера 31, на прямом выходе Q которого устанавливается лог. «0». Сигналы с выхода седьмого буфера с третьим состоянием 23 и прямого выхода Q второго RS-триггера 31 поступают на входы второго элемента «ИЛИ» 32, с выхода которого через десятый буфер с третьим состоянием 34 передается сигнал на выход ЗАНЯТ устройства.

Данные со входа устройства С_ДАННЫЕ через одиннадцатый буфер с третьим состоянием 25 подаются на выход устройства А_ДАННЫЕ.

Сигнал со входа СБРОС поступает через элементы «И»: третий 5, первый 6, пятый 7 и четвертый 16 на вход сброса R D-триггеров: первого 8, второго 9, третьего 10 и четвертого 18 соответственно; через второй элемент «И-НЕ» 14 и второй элемент «И» 15 - на вход сброса R первого RS-триггера 17; через третий элемент «И-НЕ» 29 и пятый элемент «И» 30 - на вход сброса R второго RS-триггера 31 и непосредственно - на вход сброса R пятого D-триггера 26 и регистра 11. При лог. «0» на входе сброса R прямые выходы Q триггеров и регистра находятся в лог. «0», а инверсные - в лог. «1».

Формирователи импульса: первый 12, второй 13, третий 27 и четвертый 28, могут быть выполнены по схеме с триггером Шмитта и RC-цепью, приведенной в [3], стр.83.

В результате обеспечивается двусторонний обмен данными между устройством с синхронным параллельным интерфейсом и устройством с самосинхронным четырехфазным интерфейсом; при этом обеспечивается сигнализация готовности принятия данных получателем во всех режимах работы устройства.

Источники информации

1. Патент US 006,601,293 A от 09.05.2000 ((SYNCHRONOUS INTERFACE TO A SELF-TIMED MEMORY ARRAY».

2. Jens Spars⌀, Steve Furber. Principles of asynchronous circuit design - A System Perspective. Kluwer Academic Publishers. ISBN 0-7923-7613-7.

3. Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования. - М.: Мир, 2001. - 379 с., ил. - (Современная схемотехника). ISBN 5-03-003449.

Устройство обмена данными между четырехфазным самосинхронным и синхронным параллельным интерфейсом, содержащее канал передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный и канал передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный, выход данных которого соединен с соответствующим входом, а вход данных - с соответствующим выходом канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный, выход ПОДТВЕРЖДЕНИЕ канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный соединен со входом ПОДТВЕРЖДЕНИЕ канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный, выход РАЗРЕШЕНИЕ канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный соединен со входом РАЗРЕШЕНИЕ канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный, выход ЗАПРОС канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный соединен со входом ЗАПРОС канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный, выход ЗАНЯТ канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный соединен со входом ЗАНЯТ канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный, отличающееся тем, что канал передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный состоит из схемы формирования сигнала ПОДТВЕРЖДЕНИЕ, схемы формирования сигнала РАЗРЕШЕНИЕ и схемы передачи данных, причем схема формирования сигнала ПОДТВЕРЖДЕНИЕ состоит из первого буфера с третьим состоянием, вход данных которого является входом ЗАПРОС канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный, а выход соединен с первым и вторым входами первого элемента «И-НЕ», выход которого соединен с тактовым входом первого D-триггера, ко входу сброса которого подсоединен выход третьего элемента «И», а неинвертированный выход которого соединен со входом первого формирователя импульса, выход которого соединен с входом первого элемента «НЕ», выход которого соединен с первым входом второго элемента «И-НЕ», выход которого соединен со входом установки первого RS-триггера, неинвертированный выход которого соединен со входом данных второго буфера с третьим состоянием, со вторым входом третьего элемента «И», выход которого соединен со входом сброса первого D-триггера, а инверсный выход первого RS-триггера соединен со вторым входом первого элемента «И», выход которого соединен со входом сброса второго D-триггера, а первый вход соединен со вторым входом второго элемента «И-НЕ» и вторым входом второго элемента «И», неинвертированный выход второго D-триггера соединен со входом второго формирователя импульса, выход которого соединен с первым входом второго элемента «И», выход которого соединен со входом сброса первого RS-триггера, причем выход первого буфера с третьим состоянием соединен со входом данных второго D-триггера, а вход установки объединен со входами данных и установки первого D-триггера и с входом лог.«1» канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный, выход второго буфера является выходом ПОДТВЕРЖДЕНИЕ канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный; схема формирования сигнала РАЗРЕШЕНИЕ состоит из третьего буфера с третьим состоянием, вход данных которого является входом ЗАНЯТ канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный, а выход соединен со входом данных третьего D-триггера, неинвертированный выход которого соединен со входом данных четвертого буфера с третьим состоянием, со вторым входом четвертого элемента «И» и со входом данных четвертого D-триггера, инверсный выход которого соединен со вторым входом пятого элемента «И», вход установки - с входом лог.«1» канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный, а вход сброса - с выходом четвертого элемента «И», причем первый вход пятого элемента «И» объединен со вторым входом четвертого элемента «И», а выход соединен со входом сброса третьего D-триггера, вход установки которого соединен с входом лог.«1» канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный, выход второго буфера является выходом РАЗРЕШЕНИЕ канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный; схема передачи данных состоит из пятого буфера с третьим состоянием, вход которого является входом НАПРАВЛЕНИЕ канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный, а выход соединен со входом данных регистра, выход которого соединен со входом данных шестого буфера с третьим состоянием, выход которого является выходом данных канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный, тактовые входы второго, третьего D-триггеров и регистра являются тактовым входом канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный, второй вход второго элемента «И-НЕ», первый вход третьего элемента «И», второй вход второго элемента «И», первый вход первого элемента «И», первый вход пятого элемента «И», второй вход шестого элемента «И» и выход сброса регистра являются входом сброса канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный, управляющие входы первого, второго, третьего, четвертого, пятого, шестого буферов являются входом НАПРАВЛЕНИЕ канала передачи данных из четырехфазного самосинхронного интерфейса в синхронный параллельный; канал передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный состоит из седьмого буфера с третьим состоянием, вход которого является входом ПОДТВЕРЖДЕНИЕ канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный, а выход соединен со вторым входом первого элемента «ИЛИ» и со входом третьего формирователя импульса, выход которого соединен со входом второго элемента «НЕ», выход которого соединен с первым входом третьего элемента «И-НЕ», выход которого соединен со входом установки второго RS-триггера, выход которого соединен с первым входом первого элемента «ИЛИ» и входом данных восьмого буфера с третьим состоянием, выход которого является выходом ЗАПРОС канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный; девятого буфера с третьим состоянием, вход которого является входом РАЗРЕШЕНИЕ канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный, а выход соединен со входом данных пятого D-триггера, сигнал установки которого соединен с входом лог.«1» канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный, а неинвертированный выход - со входом четвертого формирователя импульса, выход которого соединен с первым входом пятого элемента «И», выход которого соединен со входом сброса второго RS-триггера; третьего элемента «НЕ», вход которого является входом НАПРАВЛЕНИЕ канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный, а выход соединен с управляющим входом одиннадцатого буфера с третьим состоянием и управляющими входами седьмого, восьмого, девятого и десятого буферов с третьим состоянием, вход данных десятого буфера с третьим состоянием соединен с выходом первого элемента «ИЛИ», а выход является выходом «ЗАНЯТ» канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный, при этом вход данных одиннадцатого буфера с третьим состоянием является входом данных канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный, а выход - выходом данных канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный, вторые входы седьмого и восьмого элементов «И» и вход сброса пятого D-триггера являются входом сброса канала передачи данных из синхронного параллельного интерфейса в четырехфазный самосинхронный.