Персональный компьютер

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано при изготовлении персональных компьютеров. Техническим результатом является снижение энергоемкости радиопередающего и приемного устройств, а также осуществление формирования изображения на экране монитора без строчной и кадровой разверток. Устройство содержит первое радиопередающее устройство, выполненное одноканальным, содержащее формирователь кодов, синтезатор частот, передатчик радиосигналов, распределители импульсов, три кодера, радиоприемное устройство, имеющее один канал приема радиосигналов, содержащее блок выбора канала передачи, канал приема радиосигналов, канал формирования управляющих сигналов, три канала видеосигнала R, G, В, содержащие приемный регистр, декодер, блок удвоения отсчетов, накопители кодов кадра, импульсные усилители. 18 ил., 1 табл.

Реферат

Изобретение относится к персональным компьютерам /ПК/ и выполняет его функции.

Прототипом принят "Персональный компьютер" [1], содержащий системный блок, цифровой монитор, первое радиопередающее устройство в корпусе системного блока и первое радиоприемное устройство в корпусе цифрового монитора, устройство ввода в составе второго радиопередающего устройства на корпусе клавиатуры, мыши и второго радиоприемного устройства на системном блоке ПК и содержащий устройства вывода /модем, принтер/. Недостатками прототипа являются передача видеоинформации по двум радиоканалам первым радиопередающим устройством и прием ее двумя каналами приема первым радиоприемным устройством, удвоение строк в кадре на приемной стороне усложняет каналы видеосигналов R, G, В, принятая строчная развертка и построчная развертка кадра снижают качество изображения на экране монитора.

Цель изобретения - снижение энергоемкости первого передающего и приемного устройств и исключение строчной и кадровой разверток при воспроизведении изображения на экране.

Техническими результатами являются снижение энергоемкости первого приемного и радиопередающего устройств передачей и приемом видеоинформации по одному радиоканалу и формирование изображения на экране без строчной и кадровой разверток за счет одновременного получения всех пикселов кадра на длительность кадра.

Сущность изобретения в том, что в первое радиопередающее устройство ПК вводятся три кодера и передатчик выполняется одноканальным, а в радиоприемном устройстве имеется один канал приема радиосигналов, и в каждый канал видеосигнала R, G, В вводятся декодер и накопитель кодов кадра, и излучающие один цвет ячейки элементов матриц экрана подключены параллельно к выходам своего блока импульсных усилителей, который включает импульсные усилители по числу излучающих ячеек в плоскопанельном экране. На передающей стороне применяется видеорежим 960строк × 640отсч × 30 Гц, где 960 - число кодируемых строк, как в прототипе, 640 - число кодируемых отсчетов в строке, как в прототипе, 30 Гц - частота кадров. В прототипе частота кадров 60 Гц, но формирование кадра выполняется разверткой каждой строки и построчной разверткой кадра. В предлагаемом плоскопанельном экране развертки строк и кадра нет, изображение на экране формируется сразу целиком синхронным и параллельным включением на излучение всех элементов матрицы по числу разрешения кадра на длительность всего периода кадра.

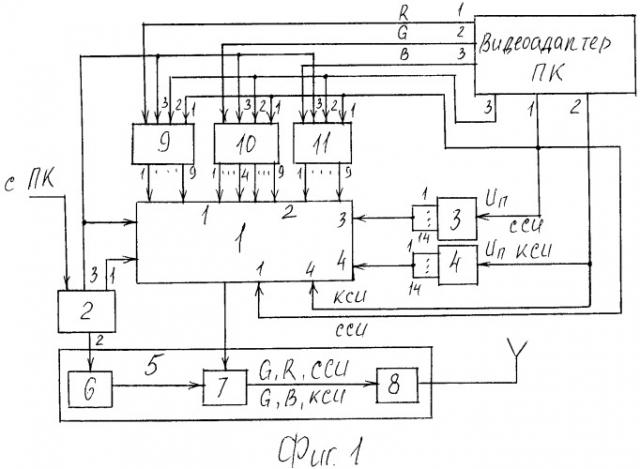

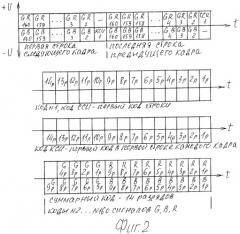

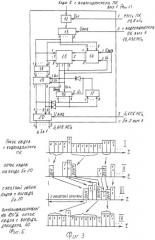

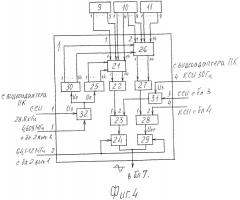

Структурная схема первого радиопередающего устройства показана на фиг.1, структура цифрового потока на фиг.2, кодер на фиг.3, формирователь кодов на фиг.4, спектр амплитудно-модулированного сигнала на фиг.5, первое радиоприемное устройство на фиг.6, двухполярный амплитудный детектор на фиг.7, декодер на фиг.8, блок удвоения отсчетов на фиг.9, накопитель кодов кадра на фиг.10, блок регистров на фиг.11, 12, блок выделения строчного /кадрового/синхроимпульса на фиг.13, временные диаграммы работы на фиг.14, общий вид элемента матрицы на фиг.15, элемент матрицы, вид сверху на фиг.16, схема верхней излучающей ячейки на фиг.17, расположение элементов матриц в экране на фиг.18.

Частота дискретизации видеосигналов в первом радиопередающем устройстве составляет fд=960 × 30 Гц × 640=18,432 МГц. Первое радиопередающее устройство /фиг.1/ расположено в системном блоке ПК и включает формирователь 1 кодов, синтезатор 2 частот, первый самоходный распределитель 3 импульсов [4 с.269, 274], второй самоходный распределитель 4 импульсов /СРИ/ и передатчик 5 радиосигналов из одного канала и включает последовательно соединенные усилитель 6 несущей частоты, амплитудный модулятор 7 и выходной усилитель 8 и включает вновь введенные первый 9, второй 10, третий 11 кодеры. Амплитудный модулятор 7 состоит из последовательно соединенных кольцевого модулятора и полосового фильтра [2 с. 234], отфильтровывающего одну из боковых частот в спектре амплитудно-модулированного сигнала /фиг.5/. При формировании цифрового изображения всегда будут последовательно идущие коды, равные по величине, и чем выше частота дискретизации /18,432 МГц/, тем равных кодов будет больше: цифровые потоки за счет равных по величине кодов можно сжать. Последовательность кодов, равных по величине, здесь представляется двумя кодами: первым является код первый в последовательности равных кодов, вторым кодом является код, значение которого означает число равных кодов в последовательности без первого. Сжатие потока кодов каждого цветового сигнала выполняется отдельно своим кодером 9, 10, 11. Наименьший общий коэффициент сжатия в каждом кодере принимается 4. При сжатии потока кодов в четыре раза частота дискретизации на выходе кодера составляет

Кодеры идентичны, каждый содержит /фиг.3/ последовательно соединенные ключ 12; первый восьмиразрядный регистр 13, второй восьмиразрядный регистр 14, схему сравнения /компаратор/ 15, счетчик 16 импульсов и дешифратор 17, последовательно соединенные блок 18 элементов задержек из восьми элементов, блок 19 ключей из восьми ключей и буферный накопитель 20 кодов кадра, объем которого 153600 девятиразрядных кодов

Информационным входом является сигнальный вход ключа 12, подключенный к соответствующему выходу /1-3/ кодов видеоинформации в видеоадаптере ПК /фиг.1/. Выходами кодера являются первый-девятый выходы буферного накопителя 20 кодов кадра. Управляющими входами являются: первым - управляющий вход /Uот/ ключа 12, подключенный к входу первого СРИ 3 /фиг.1/, вторым - управляющий вход /Uвыд/ первого регистра 13, подключенный к соответствующему управляющему выходу импульсов дискретизации кодов 18,432 МГц в видеоадаптере ПК /фиг.1/, третьим - управляющий вход /Uвыд/ буферного накопителя 20 кодов кадра, подключенный к выходу 3 блока 2 /фиг.1/. Формирователь 1 кодов /фиг.4/ включает два идентичных канала. Первый канал включает последовательно соединенные первый блок 21 элементов И, которых 14 штук, первый 22, второй 23 элементы ИЛИ и первый выходной ключ 24, и первый СРИ 25, второй канал включает второй блок 26 элементов И, которых 14 штук, первый 27, второй 28 элементы ИЛИ и второй выходной ключ 29, и второй СРИ 30 и включает первый ключ 31, второй ключ 32. Информационными входами блока 1 являются: первым - первые входы 14 элементов И блока 21, подключенные к первому-девятому выходам кодера 9 и к первому-четвертому выходам кодера 10, вторым - первые входы 14 элементов И блока 26, подключенные к пятому-девятому выходам кодера 10 и к первому-девятому выходам кодера 11, третьим - сигнальный вход первого ключа 31, подключенный к выходу СРИ 3, четвертым - второй вход элемента ИЛИ 28, подключенный к выходу СРИ 4. Выходом блока 1 являются объединенные выходы выходных ключей 24, 29. Управляющими входами являются: первым - управляющий вход /UЗ/ второго ключа 32, подключенный к входу СРИ 3 /фиг.1/ 28,8 кГц, вторым - объединенные сигнальные входы выходных ключей 24, 29, подключенные к первому выходу /64,512 МГц/ блока 2, третьим - сигнальный вход второго ключа 32, подключенный к третьему выходу 4,608 МГц блока 2, четвертым - управляющий вход UЗ первого ключа 31, подключенный к входу СРИ 4 /фиг.1/ 30 Гц. Вторые входы элементов И блока 21 подключены к соответствующим 1-14 выходам СРИ 25, вторые входы элементов И блока 26 подключены к соответствующим 1-14 выходам СРИ 30. Вход синтезатора 2 частот подключен к соответствующему выходу тактового генератора ПК. Выход первого ключа 31 подключен к второму входу второго элемента ИЛИ 23 /фиг.4/, и выход второго ключа 32 подключен параллельно к входам СРИ 25, 30. Первое радиоприемное устройство /фиг.6/ расположено в корпусе цифрового монитора 56 и включает блок 33 выбора канала передачи, один канал приема радиосигналов, канал видеосигнала R, канал видеосигнала G, канал видеосигнала В и канал формирования управляющих сигналов. Канал приема радиосигналов включает последовательно соединенные блок 34 приема радиосигналов, усилитель 35 радиочастоты и двухполярный амплитудный детектор 36. Канал видеосигнала R включает последовательно соединенные первый формирователь 37 импульсов, введенный вновь первый приемный регистр 39 из 14 разрядов, декодер 40, блок 41 удвоения отсчетов, накопитель 42 кодов R кадра и блок 43 импульсных усилителей. Канал видеосигнала G включает последовательно соединенные декодер 44, блок 45 удвоения отсчетов, накопитель 46 кодов G кадра и блок 47 импульсных усилителей. Канал видеосигнала В включает последовательно соединенные второй формирователь 38 импульсов, введенный вновь второй приемный регистр 48 из 14 разрядов, декодер 49, блок 50 удвоения отсчетов, накопитель 51 кодов В кадра и блок 52 импульсных усилителей. Канал формирования управляющих сигналов включает последовательно соединенные блок 53 выделения строчных синхроимпульсов /ССИ/ и синтезатор 55 частот и блок 54 выделения кадровых синхроимпульсов /КСИ/, Декодеры 40, 44, 49 идентичны, каждый включает /фиг.8/ последовательно соединенные первый девятиразрядный регистр 57, накопитель 58 кодов кадра емкостью 154600 девятиразрядных кодов /160отсч. × 960 строк/, второй девятиразрядный регистр 59, первый блок 60 ключей из восьми ключей и третий восьмиразрядный регистр 61, последовательно соединенные второй блок 62 ключей из восьми ключей, восьмиразрядный вычитающий счетчик 63 импульсов и дешифратор 64, первый 65, второй 66, третий 67 и четвертый 68 ключи.

Информационным входом декодера являются первый-девятый входы первого регистра 57, выходом являются первый-восьмой выходы третьего регистра 61. Управляющими входами являются: первым - объединенные управляющий вход регистра 57 и сигнальный вход /4,608 МГц/ третьего ключа 67, вторым - объединенные сигнальные входы /18,432 МГц/ ключей 65, 66, 68. Выход девятого разряда второго регистра 59 подключен параллельно к первому управляющему /Uот/ входу второго ключа 66, к вторым управляющим Uз входам ключей 65, 67, 68 и к первому управляющему входу второго блока ключей 62, и второму управляющему входу UЗ первого блока 60 ключей. Выход первого ключа 65 подключен к первому управляющему входу Uвыд 1 третьего регистра 61, второй управляющий вход которого Uвыд 2 подключен к выходу второго ключа 66, к которому подключен и счетный вход Uсч вычитающего счетчика 63 импульсов, выход дешифратора 64 подключен параллельно к первому управляющему входу Uот первого блока 60 ключей, к второму управляющему входу Uот второго блока ключей 62, к первым управляющим входам ключей 65, 67, 68 и к второму управляющему входу UЗ второго ключа 66. Выход третьего ключа 67 подключен к управляющему входу Uвыд накопителя 58 кодов кадра, выход ключа 68 подключен к управляющему входу Uвыд второго регистра 59. Блоки 41, 45, 50 удвоения отсчетов идентичны /фиг.9/, каждый включает триггер 69, первый 70, второй 71 блоки ключей /каждый из восьми ключей/, первый 72, второй 73, третий 74 и четвертый 75 регистры, первый 76 и второй 77 блоки элементов задержек по восемь элементов в каждом, сумматор 78 и 16 диодов.

Информационными входами блока 41 являются поразрядно объединенные входы блоков 70, 71 ключей, управляющим входом является вход триггера 69 и вход U0 сумматора 78, Выходом являются поразрядно объединенные 0-7 выходы сумматора 78 и 1-8 выходы блоков 76, 77 элементов задержек. Накопители 42, 46, 51 кодов кадра идентичны, каждый содержит /фиг.10/ блоки 791-960 регистров по числу строк в кадре. Информационными 1-8 входами накопителя кодов кадра являются поразрядно объединенные 1-8 входы всех 960 блоков 79 регистров. Выходами являются выходы всех блоков 79 регистров, которых всего 1280 × 8 × 960=9830400. Управляющими входами являются: первым - первый управляющий вход Uк /30 Гц/ первого блока 791 регистров /фиг.10/, вторым - объединенные вторые управляющие входы Uвыд /28,8 кГц/ блоков 79 регистров, третьим объединенные третьи управляющие входы Uд /36,864 МГц/ блоков 79 регистров. Управляющий выход каждого предыдущего блока регистров является первым управляющим входом для каждого последующего блока 79 регистров. Управляющий выход последнего /960/ блока 79 регистров подключен параллельно к четвертым управляющим входам всех блоков 79 регистров. Блоки 79 регистров идентичны, каждый включает /фиг.11, 12/ первый 80 и второй 81 ключи, распределитель 82 импульсов и восемь регистров 831-8, каждый из которых включает по 1280 разрядов, по числу отсчетов в строке после удвоения их.

Информационными входами блока регистров являются поразрядно объединенные с первого по восьмой третьи входы разрядов восьми регистров 83. Выходами являются параллельные выходы всех разрядов 1280 восьми регистров 83, всего выходов с блока 79 регистров 10240 /1280 × 8/. Выходы 960 блоков регистров являются выходами каждого накопителя 42, 46, 51 и составляют 9830400 /10240 × 960/. Управляющими входами блока 79 являются: первым - первый управляющий вход Uот первого ключа 80, вторым - сигнальный вход Uвыд /28,8 кГц/ второго ключа 81, третьим - сигнальный вход Uд /36,864 МГц/ первого ключа 80, четвертым - первый управляющий вход Uот второго ключа 81. Выход первого ключа 80 подключен к входу распределителя 82 импульсов, выходы которого последовательно, начиная с первого, подключены к первым /тактовым/ входам разрядов параллельно восьми регистрам 83. Последний выход /1280/ блока 82 подключен к второму управляющему входу UЗ ключа 80 и является управляющим выходом к входу первого ключа 80 в следующем в блоке 79 регистров. Выход второго ключа подключен параллельно к вторым входам разрядам восьми регистров 83 и к второму управляющему входу Uз своего ключа 81, прошедший один импульс Uвыд закрывает ключ 81. Выходы накопителей 42, 46, 51 кодов кадра подключены /фиг.6/ к информационным входам своих блоков 43, 47, 52 импульсных усилителей, каждый из которых содержит импульсные усилители по числу выходов с накопителя 42 /46, 51/ кодов кадра 9830400 /1280 × 8 × 960/. Выходы трех блоков 43, 47, 52 импульсных усилителей подключены 29491200 /9830400 × 3/ к стольким же входам плоскопанельного экрана в мониторе 56. Плоскопанельный экран представляет собой набор элементов матриц по числу разрешения кадра 1280 × 960 /1228800 пикселей/. Общий вид элемента матрицы показан на фиг.15. Элемент матрицы содержит /фиг.16/ микросветодиод 87 белого свечения и соответствующей формы /фиг.15/, непрозрачный корпус 88, в котором расположены три идентичные по составу излучающие ячейки: первая 89 излучает красный цвет R, вторая ячейка 90 излучает зеленый цвет G, третья ячейка 91 излучает синий цветов. Каждая излучающая ячейка /фиг.16, 17/ включает последовательно расположенные соответствующий цветной светофильтр 92 и первую микролинзу 93, последовательно расположенные друг за другом и по оптической оси микролинзы 93 с первого по восьмой нейтральные микросветофильтры 941-8, каждый микросветофильтр с соответствующим коэффициентом поглощения излучения в порядке принципа двоичного кода: первый 941 с коэффициентом поглощения излучения 0,5 /старший разряд кода/, второй 942 - 0,25, третий 943 - 0,125 …, восьмой 948 - 0,0039, включает с первого по восьмой микропьезоэлементы 951-8 и выходную микролинзу 96. Нейтральные микросветофильтры 94 каждый площадью ≈20×20 мкм имеют коэффициенты поглощения соответственно веса своего разряда и сведены в таблицу.

| Номер разряда кода | Вес разряда кода | Коэффициенты поглощения излучения |

| 1 старший | 27 /128/ | 0,5 /1/2/ |

| 2 | 26 /64/ | 0,25 /1/4/ |

| 3 | 25 /32/ | 0,125 /1/8/ |

| 4 | 24 /16/ | 0,0625 /1/16/ |

| 5 | 23 /8/ | 0,03125 /1/32/ |

| 6 | 22 /4/ | 0,015625 /1/64/ |

| 7 | 21 /2/ | 0,0078125 /1/128/ |

| 8 | 20 /1/ | 0,0039 /1/255/ |

Стенки корпуса 88 имеют светопоглощающее покрытие. Излучение мисветодиода 87 /фиг.16/ направляется на цветной светофильтр 92 трех излучающих ячеек, после которых излучение собирается своей микролинзой 93 и направляется на нейтральные микросветофильтры 94. Принцип работы ячеек основан на том, что каждый последовательно расположенный микросветофильтр ослабляет излучение соответственно своему коэффициенту поглощения, значения которых соответствуют принципу двоичного кода. В отсутствие управляющих сигналов на входах микропьезоэлементов 95 микросветофильтры перекрывают поток излучения до уровня ниже предела чуствительности зрения человека. Один торец каждого микропьезоэлемента 95 закреплен в стенке корпуса 88, вторые свободные их торцы соответствующим образом /фиг.17/ соединены с нейтральными микросветофильтрами 94. При поступлении на микропьезоэлемент управляющего сигнала /сигнал единицы кода/ с импульсного усилителя блока 43 /47, 52/ свободный торец его производит изгиб и поворачивает нейтральный микросветофильтр на угол 90°, поток излучения проходит без ослабления. В качестве микропьезоэлементов 951-8 применяются трубчатые пьезоэлементы [3, с. 27]. Пси изгибе свободный торец микропьезоэлемента 95 переводит свой нейтральный микросветофильтр 94 в открытое положение, не препятствующее проходу излучения на следующий микросветофильтр. На фиг.17 приведен момент преобразования кода 10110110 в яркость излучения ячейкой. Каждая излучающая ячейка выполняет преобразование "код - яркость излучения" с частотой поступления на управляющие входы микропьезоэлементов сигналов единиц кодов, которые поступают в параллельном виде. Исполняющий элемент - нейтральный микросветофильтр 94 выполняет свои функции не только при точном повороте на 90°, но и при погрешности поворота на ±10°, что обеспечивает четкую и длительную работу излучающих ячеек по точной цветопередаче на длительный срок эксплуатации. Предложенная форма корпуса /фиг.15/ элемента матрицы будет удобна при сборке всей матрицы экрана, каждый элемент может изготавливаться индивидуально, а экраны разных разрешений кадра просто набираются из готовых элементов матриц. Размеры элементов матриц с применением микротехнологии будут меньше размеров триад ЖК-ячеек в современных ЖК-экранах. Блок 53 выделения строчных синхроимпульсов /ССИ/ и блок 54 выделения кадровых синхроимпульсов /КСИ/ идентичны, каждый включает /фиг.13/ четырехразрядный счетчик 84 импульсов, дешифратор 85, элемент НЕ 86, первый Д1 и второй Д2 диоды. Информационным входом блока является счетный вход счетчика 84 импульсов, управляющим входом является вход первого диода Д1, выход которого подключен к управляющему входу U0 счетчика 84 импульсов. Выходом является выход дешифратора 85, который также через диод Д2 подключен к выходу элемента НЕ 86, а вместе они подключены к управляющему входу счетчика 84 импульсов после диода Д1. Код ССИ является 14-разрядным кодом из одних единиц и поступает с выхода блока 37 на счетный вход блока 53, управляющий вход блока 53 подключен к выходу второго формирователя 38 импульсов. Код КСИ также является 14-разрядным кодом из одних единиц и поступает с выхода формирователя 38 импульсов на счетный вход счетчика импульсов 84 блока 54, управляющий вход блока 54 подключен к выходу первого формирователя 37 импульсов.

Работа блоков 53, 54, фиг.13.

С поступлением кода ССИ на счетный вход счетчика 84 импульсов он ведет счет четырнадцати импульсов подряд, Формируется код 1110, на выходах 1, 2, 3 разрядов счетчика 84 появляются сигналы, которые дешифрируются дешифратором 85, и на выходе блока 53 появляется импульс ССИ. В момент поступления кода ССИ на вход счетчика 84 с выхода блока 38 /фиг.6/ импульсов другого кода нет, это обеспечивает ключ 31 в блоке 1 формирователя кодов /фиг.4/, ключ 31 в момент поступления кода ССИ закрыт. Начиная со второго кода строки, с блока 38 пойдут коды и на управляющий вход U0 счетчика 84 и с приходом каждой единицы кода счетчик 84 будет обнуляться.

Параллельно на счетный вход также, начиная со второго кода строки, пойдут коды с блока 37, в которых всегда есть и единицы и нули, а по каждому нулю элемент НЕ 86 выдает сигнал, который тоже обнуляет счетчик 84 импульсов. В добавление при выходе ССИ с выхода дешифратора 85 он через диод Д2 поступает и на управляющий вход счетчика 84 и тоже обнуляет его. Таким образом, схема блоков 53, 54 исключает появление на выходе ложного сигнала ССИ /КСИ/. При поступлении кода КСИ на счетный вход блока 54 на его управляющий вход с выхода блока 37 импульсы не идут, это обеспечивает ключ 32 в блоке 1 /фиг.4/, работа блока 54 аналогична работе блока 53. На передающей стороне кодируются 960 строк с 640 отсчетами в каждой. Частота строк fc=960×30 Гц=28,8 кГц. Частота следования разрядов в коде /тактовая частота/, как и в прототипе: fт=18,432 МГц × 8разр=147,456 МГц.

Разряды кодов видеосигналов R, G1, В с тактовой частотой раздельно поступают с 1-3 информационных выходов видеоадаптера ПК /фиг.1/ на информационные входы кодеров 9, 10, 11. С управляющих выходов 1 и 3 видеоадаптера ПК на первый и второй управляющие входы кодеров поступают синхроимпульсы строк /ССИ/ 28,8 кГц и частота дискретизации кодов 18,432 МГц. С соответствующих выходов видеоадаптера ПК/1 и 2 выходы на фиг.1 /в качестве сигналов запуска Uп на входы самоходных распределителей 3 и 4 импульсов [4, с.269, 274] поступают строчный ССИ и кадровый КСИ синхроимпульсы. СРИ 3 /фиг.1/ с приходом сигнала Uп выдает 14-разрядный последовательный код ССИ из одних единиц на третий информационный вход формирователя 1 кодов /фиг.1, 4/. СРИ 4 с приходом сигнала Uп выдает 14-разрядный последовательный код КСИ из одних единиц на четвертый информационный входа блока 1. Вход синтезатора 2 частот подключен к соответствующему выходу тактового генератора ПК и выдает с первого выхода синусоидальные колебания 64,512 МГц на второй вход блока 1, со второго выхода выдает несущую частоту 967,68 МГц в передатчик радиосигналов /фиг.1/, с третьего выхода частоту 4,608 МГц дискретизации кодов в сжатом потоке на третьи управляющие входы кодеров 9, 10, 11 и на третий управляющий вход блока 1 /фиг.1/ на сигнальный вход ключа 32 /фиг.4/.

Работа кодеров, фиг.3.

Восьмиразрядные последовательные коды цветового сигнала с тактовой частотой разрядов 147,456 МГц с выхода видеоадаптера ПК поступают на информационный вход кодера, а в нем на сигнальный вход ключа 12, открываемый на длительность строки синхроимпульсом ССИ с видеоадаптера ПК. Сигналы разрядов последовательного кода проходят ключ 12, заполняют первый восьмиразрядный регистр 13, где код принимает параллельный вид, в котором и используется кодером. С регистра 13 параллельный код выдается импульсом 18,432 МГц на первый-восьмой входы во второй регистр 14, на первые входы схемы сравнения 15 и 1-8 входы блока 18 элементов задержек. Исходное состояние ключей в блоке 19 открытое. Код в блоке 18 задерживается на время срабатывания 18 нc схемы сравнения и поступает через ключи блока 19 на первый-восьмой входы буферного накопителя 20 кодов кадра емкостью 153600 девятиразрядных кодов /160отсч×960/. Схема сравнения 15 выполняет сравнение по величине каждого предыдущего и последующего кодов для выявления равенства кодов или неравенства. При следовании неравных кодов они проходят через блок 18, открытые ключи блока 19 и поступают на 1-8 входы буферного накопителя 20 кодов. Выдача кодов из блока 20 выполняется сигналами

При коэффициенте сжатия выше 4 эта частота выдачи будет тем более удовлетворять. Схема 15 сравнения выполняет сравнение кодов по величине и представлена двумя микросхемами 530СП1 с временем сравнения /срабатывания/ 18 нc [5, с. 279]. При неравенстве кодов А>В появляется сигнал на выходе 2 блока 15 /в микросхеме выход 5 [с. 272, рис. 2,190], при равенстве кодов А=В появляется сигнал с выхода 1 /в микросхеме вых.7/. При равенстве кодов сигнал с выхода 1 блока 15 закрывает ключи в блоке 19, поступает счетным импульсом в счетчик 16 импульсов и как сигнал Uвыд на первый управляющий вход регистра 14. Счетчик 16 ведет счет импульсов с выхода 1 блока 15 пока идут коды, равные по величине. Счетчик 16 восьмиразрядный, максимальный код в нем 11111111 /255/, отсюда максимальный коэффициент сжатия может доходить до 255, диапазон сжатия потока кодов от 1 до 255. Счетчик из микросхем К531ИЕ160 с временем срабатывания 8 нс [5, с.428]. При появлении неравных кодов /А>В, А<В/ со схемы 15 следуют сигналы с выходов 2 или 3, которые объединены, сигнал с них используется для выдачи кода числа равных кодов из счетчика 16 через диоды на 1-8 входы блока 20 и для заполнения в блоке 20 девятого разряда, с которого этот сигнал используется для опознания по нему кода числа равных кодов при декодировании /на приемной стороне/. Этот же сигнал открывает ключи в блоке 19 и обнуляет регистр 14 вход 2 U0. Выданный перед этим с блока 20 код является первым кодом последовательности, на диаграмме 1 фиг.3 они помечены крестиками. Коды, равные по величине и подсчитанные счетчиком 16, исключаются из потока - диаграмма 3 фиг.3, за их счет и идет сжатие. Емкость буферного накопителя 20 кодов соответствует числу 9-разрядных кодов в кадре /160×960/ для обеспечения темпа следования с выхода кодера кодов с частотой 4,608 МГц. При следовании подряд кодов, равных по величине, более 255 штук, в работу вступает дешифратор 17. При коде 11111111 дешифратор 17 выдает сигнал, который одновременно открывает Uот ключи в блоке 19, обнуляет регистр 14, сигналом Uвыд выдает код из счетчика 16 /вход 1/ и обнуляет счетчик /вход 2/, а в девятый разряд блока 20 поступает сигнал для опознания кода числа равных кодов. Пропускная способность кодера определяется временем срабатывания схемы сравнения 15, которая обеспечивает до 40 Мбайт/с и удовлетворяет требуемому поступающему в кодер потоку 18,432 Мбайт/с. С выходов кодеров 9, 10, 11 коды в параллельном виде поступают на первый и второй информационные входы формирователя 1 кодов, который /фиг.4/ первым кодом в строке выдает код ССИ, из сжатого потока кодов формирует и выдает со второго по 160 коды сигналов основных цветов R, G. В /фиг.2/. Код КСИ является первым кодом только в первой строке каждого кадра, причем, когда идет код КСИ, не идет код ССИ. Код ССИ является в каждой строке первым, начиная со второй строки, при этом не идет код КСИ /фиг.2/. Сигналы 1-9 разрядов кода R и сигналы 1-4 разрядов кода G представляются на выходе блока 1 положительными полусинусоидами моночастоты 64,512 МГц, сигналы 1-9 разрядов в кодах В и сигналы в 5-9 разрядах кода G единицы представляется отрицательными полусинусоидами той же частоты 64,512 МГц.

Работа формирователя 1 кодов, фиг.4.

Временные диаграммы работы блока 1 проиллюстрированы на фиг.14. Блок 1 преобразует параллельные коды в последовательные и заменяет в них представление единиц с импульсов на положительные и отрицательные полусинусоиды. На первый информационный вход в блок 21 поступают сигналы 1-9 разрядов кода R и сигналы 1-4 разрядов кода G, на второй информационный вход в блок 26 поступают сигналы 5-9 разрядов кода G и сигналы 1-9 разрядов кода В, на третий информационный вход /сигнальный вход ключа 31/ поступают сигналы 1-14 разрядов сигнала ССИ, на четвертый информационный вход поступают сигналы 1-14 разрядов сигнала КСИ, при этом передний фронт сигнала КСИ с видеоадаптера ПК закрывает ключ 31, который не пропускает сигналы кода ССИ, а задний фронт КСИ открывает ключ 31, коды ССИ, начиная со второй строки, проходят через ключ 31. На вторые входы элементов И блоков 21, 26 поступают последовательно четырнадцать импульсов с выходов СРИ 25, 30, сигнал Uп на которые поступает с блока 2вых. /4,608 МГц/. Первые коды всех строк не проходят на вход выходного ключа 24, так как синхроимпульс строки ССИ передним фронтом закрывает ключ 32, и СРИ 25, 30 не запускаются. Открывается ключ 32 задним фронтом импульса ССИ. С выходов блоков 21, 26 импульсы кодов последовательно поступают через элементы ИЛИ 22, 23 и 27, 28 на управляющие входы выходных ключей 24, 29 соответственно и открывают их на время своей длительности Выходной ключ 24 в открытом состоянии пропускает одну положительную полусинусоиду моночастоты 64,512 МГц на выход, выходной ключ 29 в открытом состоянии пропускает на выход одну отрицательную полусинусоиду той же частоты. Выходы ключей объединены и являются выходом блока 1, выходной сигнал с него представляется полными или неполными синусоидами моночастоты 64,512 МГц со стабильностью 10-7, который является модулирующим сигналом для несущей частоты 967,68 МГц в амплитудном модуляторе 7 передатчика 5 радиосигналов. Сигналы разрядов кода ССИ представляются на выходе блока 1 четырнадцатью положительными полусинусоидами, сигналы разрядов кода КСИ представляются на выходе блока 1 четырнадцатью отрицательными полусинусоидами. Когда идет код ССИ, нет кода КСИ, и, наоборот, при коде КСИ нет кода ССИ. В амплитудном модуляторе 7 подавляется несущая частота 967,68 МГц /64,512×15/, в выходной усилитель 8 выдается верхняя боковая частота 1032,192 МГц /967,68+64,512/ с информацией кодов видеосигналов и занимает при стабильности несущей 10-7 в эфире полосу ±103 Гц или 206 Гц. Радиосигналы на приемной стороне /фиг.6/ принимаются блоком 34, являющимся селектором каналов с электронной настройкой. Блок 34 включает входную цепь, усилитель радиочастоты и смеситель. Радиочастотный сигнал через петлю связи поступает на смеситель, на второй вход которого с синтезатора 55 частот выход 5 подается на третий вход блока 34 частота, равная несущей частоте передатчика 5, необходимая для детектирования однополосного сигнала [6, с. 146]. Сигнал со смесителя, являющийся выходным сигналов блока 34, поступает на вход усилителя 35 радиочастоты, где усиливается до необходимой величины и поступает на вход двухполярного амплитудного детектора 36, выполненного по схеме на фиг.7. Диод Д1 выделяет положительную огибающую модулирующего сигнала /диаграмма 9, фиг.14/. Диод Д2 из модулирующей выделяет огибающие положительные полусинусоиды /диаграмма 10/ - символы единиц кодов R и 1-4 разрядов кодов G. Диод Д3 из модулирующей выделяет огибающие отрицательных полусинусоид /диаграмма 11/ - символы единиц кодов В и 5-9 разрядов кодов G. С первого выхода блока 36 продетектированные положительные полусинусоиды частоты 64,512 МГц поступают на вход формирователя 37 импульсов, со второго выхода блока 36 продетектированные отрицательные полусинусоиды 64,512 МГц поступают на вход второго формирователя 38 импульсов.

Формирователи 37, 38 импульсов выполнены по схеме несимметричного триггера с эмиттерной связью [7, с.209], формирующего прямоугольные импульсы из гармонически изменяющихся сигналов. Импульсы с формирователей импульсов имеют одну полярность и длительность, равную длительности импульсов в кодах на передающей стороне. Единицы в кодах опять представляются импульсами, нули - их отсутствием. Порядок работы радиоприемного устройства определяется сигналами управления с канала формирования управляющих сигналов. Задающая роль принадлежит блоку 53 выделения ССИ. По синхроимпульсам строки ССИ производится точная подстройка частоты в синтезаторе 55 частот. Синтезатор 55 частот выдает с первого выхода импульсы дискретизации 18,432 МГц кодов, со второго выхода тактовые импульсы 147,456 МГц, с третьего импульсы двойной частоты дискретизации 36,864 МГц, с четвертого импульсы 4,608 МГц дискретизации кодов в сжатых потоках, с пятого выхода - синусоидальные колебания несущей частоты на третий вход блока 34. Вторые входы блока 65 подключены к второй группе выходов блока 33, сигнал с которого определяет частоту, выдаваемую с блока 55 на третий вход блока 34. С формирователя 37 импульсов 14-разрядные суммарные коды поступают на информационный вход первого /G, R/ приемного регистра 39, со второго формирователя 38 импульсов 14-разрядные суммарные коды /G, В/ поступают на информационный вход второго приемного регистра 48. Приемный регистр 39 14-разрядный и принимает 1-9 разряды кода R, а в 10-13 разряды принимает 1-4 разряды кода G. Приемный регистр 48 также 14-разрядный и принимает в 1-9 разряды девятиразрядные коды В, а в 10-14 разряды принимает 5-9 разряды кода G. С приемных регистров 39, 48 девятиразрядные коды R, G, В выдаются сигналом Uвыд 4,608 МГц в декодеры 40, 44, 49 соответственно.

Работа декодеров, фиг.8.

Коды в параллельном виде поступают в первый регистр 57, с которого выдаются с частотой 4,608 МГц /с четвертого выхода блока 55/ в накопитель 58 кодов кадра, из которого коды выдаются сигналами с ключа 67. При закрытом состоянии ключа накопитель 58 кодов кадра накапливает коды кадра. Исходное состояние ключей в блоке 62 закрытое, в блоке 60 открытое, ключей 65, 67, 68 открытое, ключа 66 закрытое. В первые-восьмые разряды второго регистра 59 поступают информационные сигналы 1-8 разрядов кода, а при наличии в девятом разряде сигнала опознания кода числа равных кодов он поступает в девятый разряд регистра 59.

С регистра 59 код выдается сигналом с ключа 68 уже с частотой 18,432 МГц. Пока в регистр 59 поступают коды без сигнала опознания в девятом разряде они поступают через открытые ключи блока 60 в третий регистр 61, а с него выдаются сигналом Uвыд 1 с ключа 65 на выход декодера 40. Сигнал Uвыд 1 при выдаче кода и обнуляет разряды регистра 61. При поступлении в регистр 59 кода с сигналом опознания в девятом разряде сигнал с девятого разряда регистра 59 закрывает ключи в блоке 60, открывает ключи в блоке 62, закрывает ключи 65, 67, 68 и открывает ключ 66, выдача кодов с накопителя 58 и с регистра 59 прерывается, а накопитель 58 кодов кадра производит накопление кодов кадра, так как в него продолжают поступать коды. Код числа равных кодов через открытые ключи блока 62 поступает в вычитающий счетчик 63 импульсов, на счетный вход которого с ключа 66 поступают импульсы 18,432 МГц. Импульс с ключа 66 поступает сигналом Uвыд 2 на второй управляющий вход регистра 61 и выдает содержащийся в нем код, но при этом не обнуляет разряды регистра 61. Поэтому пока идет работа счетчика 63, на вычитание из регистра 61 выдается один и тот же код, эти коды были изъяты при сжатии потока в кодере на передающей стороне. С выхода регистра 61 идет восстановленный на 100% поток кодов, С регистра 61 идут только восьмиразрядные коды с дискретизацией 18,432 МГц в блок 41. По окончании вычитания в счетчике 63 в дешифратор 64 поступает код из нулей. С выхода дешифратора 64 сигнал параллельно закрывает ключи в блоке 62, открывает ключи в блоке 60 /вход 1/ и ключи 65, 67, 68. С накопителя 58 опять выдаются коды в регистр 59, с него через ключи блока 60 в регистр 61, процессы повторяются. Пропускная способность декодера определяется временем срабатывания 10,5 нс счетчика 63, который из микросхем 100ИЕ137 [5, с.428], плюс время срабатывания дешифратора 64 6 нс /микросхема 100ИД161 [5, с.433]/. Скорость восстановления потока кодов до 50 Мбайт/с. Восстановленный поток кодов с частотой 18,432 МГц и числом отсчетов в строке 640 /160×4/ поступает на вход блока 41 /45, 50/ удвоения отсчетов /640×2/. Удвоение отсчетов выполняется получением промежуточных /средних/ кодов между каждым прошедшим и следующим за ним кодов. Восстановленный поток кодов с частотой 18,432 МГц и числом отсчетов 640 в строке поступает на вход блока 41 удвоения отсчетов /фиг.9/. В блоках 41, 45, 50 выполняются сложение кодов и деление кода суммы на два, причем деление выполняется без временных затрат: отбрасыванием младшего разряда в коде /как при делении десятичного кода на десять/. Отбрасывание младшего разряда в коде суммы выполняется соответствующим подключением выходов сумматора 78 и выходов блоков 76, 77 элементов задержек /фиг.9/:

Разряд 0 означает перенос в старший разряд при сумме кодов в сумматоре 78. Удвоение отсчетов в строке сокращает период следования кодов в два раза, равный 27 нс , с выхода блока 41 коды идут с частотой 36,864 МГц. Время процесса сложение в сумматоре 78 принимается 27 нс, выполняется микросхемами К555ИМ6 [5, с.258]. После включения питания в регистрах 72-75 нули. С приходом первого импульса 18,432 МГц в триггер 69 /фиг.9/ с его первого выхода сигнал Uвыд 1 одновременно выдает "код 0" с регистра 73 на первые входы сумматора 78, из регистра 74 "код 0" в блок 77 и через диоды на вторые входы сумматора 78, сигналы выдачи и обнуляют регистры, открывает ключи в блоке 70 на время прохода кода через его ключи, регистры 72, 73 заполняются кодом "код 1". В сумматоре идет сложение "код 0+код 0", по окончании которого /27 нс/ код суммы из сумматора идет на выход, при этом делится на два

Блоки 76, 77 выполняют задержку кодов на 54 нс, причем первая половина времени задержки 27 нс приходится на процесс сложения, а че