Арифметическое устройство параллельногодействия

Иллюстрации

Показать всеРеферат

240335

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства ¹

Кл. 42ml, 7/38

Заявлено 10.1.1968 (№ 1208881/18-24) с присоединением заявки в

Приоритст

Опубликовано 21.111.1969. Бюллетень № 12

Дата опубликования описания 14Л И1.1969

МПК G 06f

1 ДК 681.325.5(088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Автор изобретения

Б. М. Власов

Заявитель

АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЪНОГО

ДЕЙСТВИЯ

Известны арифметические устройства, выIIIoJIíelííûå на логических элементах и тригге.рах, IB которых для,выполнения операций логического сложения, логического умножения, .выдачи кода на числовые шины используются отдельыые логические схемы «И». предложенное устройство отличается тем, НТо выход схехты «И», подключен ной ко входу уста но в ки «О» триггера каждого разряда нака пли вающего регистра, соеди не н с входом схемы «И», выход которой подключен ко вхо,ду схемы <.ИЛИ», а выход этой схемы «ИЛИ» соединен с числовой шиной.

Это позволяет сократить объем оборудования арифметического устройства и улучшить

его характеристики.

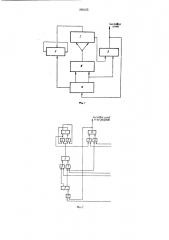

На фиг. 1 представлена блок-схема арифметического устройства параллельного действия, где: I — накапливающий регистр; !!— схема переноса; !!! — схема передачи кода;

I V — регисгр слагаемого; V — схема, выдачи кода на числовые шины; на фиг. 2 — функцио1налыная схема а-10 разряда арифметичеокото устройства, где: 1 — триггер накапливающего ,регистра I; 2 — триггер регистра слагаемого

IV; 8 — 8 — схемы «И»; 9, 10 — схемы «ИЛИ».

Рассмотрим работу и-го разряда арифметического устройства при вьиполне нии операции выдачи кода из накапли вающего регистра на числовые шины.

Для выполнения этой операции необходимо ,подать .на схем . «И» 5 потенциа I, разрешающий выдачу кода на числовые шины ЧШ, и (импульс выдачи кода из рег1гстра c,1BBßÛIÎÃÎ в сумматор на схему «И» 8. Так как в исходном положении триггер 2 приемного регистра слагаемого установлен в нулевое положение, то схема «И» 8 будет открыта. В том cëó÷àå, если приемный регистр не установлен в ну".å1О зое положение, то им пульсы подаются íà схемы «И» 7 и 8 одновременно. Импульсы с выходов схем «И» 7, 8 через схему «ИЛИ» 9 поступают на управляемый счетный вход триггера 1 (логические схемы «Иъ 8, 1). Если в

15 триггере 1 сохранился код «нуля >, то импульс, поступивший со схемы «ИЛИ» 9, пройдет через схехlу «И» 8 на единичный вход триггера 1 и запишет в него код «единиць!». Так как с выхода схемы «И» 4 на вход схемы «И» 5

20 пс поступало импульса, то и на Illcловую шину из рассматриваемого разря lа код не выда вался. В том случае, осли до прихода импульса со схемы «ИЛИ» 9 в I pllrl epc 1 «ранился код «единицы», то импульс со схемы

25 «ИЛИ» 9,поступит через схему «И.> 4 Ia нулевой вход этого триггера и на схему «И» 5 схемы выдачи кода на числовую шину. Другими cëo BàìII, код «един IIIBI», хранящийся в триггере 1, будет вы дан на числовую шину.

3Q Чтобы сохранить первоначальное 3 .1а 1свис

240335 кода |иакапли|зающего регистра, необходимо через схемы «И» 7 и 8 и схему «ИЛИ» 9 подать второй импульс, предварительно сняв со схемы «И» 5 потенциал, разрешающий выдачу кода .на число|вую IIIHIH), Аналогично |мосжет быть выдано mHBepcHoe значение кода нака пли вающето регистра. При этом разрешение на выдачу кода необходимо дать на в|ремя cëåäoвания второго такта или выпо I HHTb инвертирова ние perHicTpa заранее.

Для вы полонения операции логического умножения необходи|мо .подать импульс на схему

«И» 7 и разрешающий поте|нциал на схему

«И» 5 (считая, что исходные числа хранятся в Hака|пливающем регистре и регистре слагаемого в прямых кодах). Результат лотического ум ножения будет сразу же выда н на числовые ши ны. По второму. такту, по|ступающему в ту же цепь (|схема «И» 7, схема

«ИЛИ» 9) происходит второе инве ртиро ва|ние кода нака|пливающего регистра, тем самым сохраняется исходное значение кода слагаемого.

Операция логическото умножения кодов двух чисел выполняется следующи м образом. (10110001 первое число, хра нящееся в нака пли|вающем регистре

10001101 — второе число, хра нящееся в регистре слагаемого

00111100 — код числа в накапли вающем регистре

10000001 — результат логиче1 ского умножения

| 10110001 — код числа н а ка|пл ивающего регистра

00000000 — код |на число|вой ши|не

10001101 — |код числа в регист1 ре слагаемого

I такт !

I I та|кт

Предлагаемая схема, позволяет выполнить опе|рацию логического сложения, не вводя в состав устройства дополнительных логических элементов.

Операция логического сложения выполняется следующим образом.

Числа для логического сложения хранятся в нака|пли|вающем регистре и регистре слагаемого |в пря Iblx,кодах. На время cëåäoBB HHÿ и м|пульса перьвого такта раз решается выдача как из регистра слагаемого, так и из нака пли вающе|го регистра, т. е.,на схему «И» 5 подается разрешающий потенциал, а,на схему

«И» б — импульс, выдачи кода из регистра слагаемого. Для выдачи кода из накапли вающего регистра на схемы «И» 7 и 8 одновреhIeIHIHo подается импульс, который по цепи: схема «ИЛИ» 9, схема «И» 4 (в том случае, если в три пгере 1 хранится код «единицы»), схема «И» 5, схема «ИЛИ» 10 передается на числовую шину. По цепи: схема «И» б, схе|ма

«ИЛИ» 10 на числовую ши ну поступает в виде импулыса код «единицы» триггера 2. Та|ки|м образом,.на числовой шине будет получен результат логического сложения двух кодов.

Для восстановления исход|ного кода накапливающего регистра на схемы «И» 7 и 8 подает5 ся второй Hxllll гльс. ,Пример,выполя ния операции логического сло CHHII кодо ; 101100110 » 0001!0001.

101100110 —.первое слагаемое, х|ранящееся в на|ка|пли|вающем регистре

000110001 †:второе слагаемое, хранящееся в регистре слагаемого

010011001 — код числа в накапливающем регистре

10!100110 — код числа, выданкый на ЧШ из накапллваю щ е го регистра

1 такт

000110001 — код числа в регистре слагаемого

000110001 — код числа, выдан|ный из регистра слагаемого на чисЛОВЪ|Е ШИНЫ

101110111 — код числа, выда нный на числовые шины из двух регистро в — результат операции логического сложения

101100110 — код числа в нака пли вающем ipeгистре

000000000 — код числа, выдан|ный на числовую шину

000110001 — код числа реги стра слагаемого

30

II такт

40

Предмет изобретения

Арифметическое устройство параллельного действия, содерхкащее накапливающий регистр, репистр слагаемого, цепи, передачи кода из регистра слагаемого,в накапливающий ре55 гистр, схемы фо рмирова|ния;переносов и цепи выдачи кода, вы пол нен|ные на трипгерах с управляемым счетным входом и логических элементах «И» и «ИЛИ», отличающееся тем, что, с целью упрощения, выход схемы «И», 60 подключен|ной ко входу уста но в ки «0» триггера каждого разряда накапливающего региспра, соединен со входом схемы «И», выход которой подключен ко,входу схемы «ИЛИ», а выход этой схемы «ИЛИ» соединен с число65 вой шиной.

45 Та|ким об<разом, предлагаемое устрой ство на двух логических элементах поз воляет выполнить четыре операции. Каждая из ipaccxoTpeH,ных операций, выполняется за один такт.