Устройство для анализа сигналов в реальном масштабе времени

Иллюстрации

Показать всеИзобретение относится к области измерительной техники и может быть использовано в измерительных системах для измерения амплитуд и частот гармонических составляющих в исследуемых сигналах. В устройство дополнительно введены аналоговый сумматор, схема «И», а также вторая группа узлов, содержащих последовательно соединенные блок постоянной памяти, аналого-цифровой умножитель, аналоговый интегратор со сбросом, блок выделения абсолютной величины сигнала. При этом входы блока постоянной памяти подключены к выходам счетчика формирования адреса. Выходы блоков выделения абсолютной величины сигнала подключены к входам аналогового сумматора, а входы схемы «И» подключены к выходам счетчика циклов. Технический результат заключается в повышении быстродействия устройства. 1 ил.

Реферат

Предлагаемое устройство относится к области измерительной техники и может быть использовано для измерения величин амплитуд и частот гармонических составляющих в исследуемых сигналах и, в частности, может быть использовано для формирования спектров при распознавании речи, а также для формирования спектров акустических шумов при надводной и подводной навигациях.

Известны устройства для анализа гармонических составляющих в сигналах, одно из которых содержит блок управления, блок индикации, фильтры, АЦП, цифровые интеграторы, функциональные преобразователи, буферные регистры, вычислительные блоки, блоки разложения на гармоники, блок обратной связи [1], а второе содержит аналоговый фильтр нижних частот, АЦП, два цифровых фильтра, два блока изменения частот, блоки вычитания, сумматор, умножитель, блок усреднения, блок синхронизации [2]. Общей особенностью этих устройств является относительно низкое быстродействие.

Наиболее близким по техническому решению к предлагаемому устройству является устройство для анализа сигналов в реальном масштабе времени [3], содержащее генератор тактовых импульсов с регулируемой частотой, блок постоянной памяти, последовательно соединенные счетчик циклов, формирователь импульсов и элемент ИЛИ, шину установки начальных условий, входную и выходную шины, последовательно соединенные блок сдвига фазы, счетчик формирования адреса и инвертор, последовательно соединенные аналого-цифровой умножитель, аналоговый интегратор со сбросом, блок выделения абсолютной величины сигнала и амплитудный детектор, выход которого подключен к выходной шине, а второй вход - к шине установки начальных условий, соединенной с первым установочным входом блока сдвига фазы, с установочным входом счетчика формирования адреса, с установочным входом счетчика циклов, с установочным входом формирователя импульсов и вторым входом элемента ИЛИ, входная шина подключена к аналоговому входу аналого-цифрового умножителя, выход генератора тактовых импульсов с регулируемой частотой подключен к сигнальному входу блока сдвига фазы, выходы всех разрядов, кроме старшего, счетчика формирования адреса подключены к входу блока постоянной памяти, своим выходом соединенного с цифровыми входами аналого-цифрового умножителя, выход старшего разряда счетчика циклов подключен к второму установочному входу блока сдвига фазы, а выход элемента ИЛИ подключен к входу сброса аналогового интегратора.

Это устройство для анализа сигналов принято в качестве прототипа. Недостатком прототипа является относительно низкое быстродействие, которое обусловлено подбором начальной фазы сканирующего синусоидального сигнала, который (подбор начальной фазы) осуществляется с помощью блока сдвига фазы и предполагает формирование начальной фазы синусоидального сигнала с шагом Δφ в диапазоне 0-2π. При этом при каждом очередном значении начальной фазы производятся однотипные вычисления, максимальный результат которых и является величиной амплитудного спектра при текущей частоте ω.

Технический результат предлагаемого изобретения направлен на повышение быстродействия устройства за счет исключения подбора начальной фазы сканирующего синусоидального сигнала, что достигается тем, что в известное устройство для анализа сигналов в реальном масштабе времени, содержащее последовательно соединенные генератор тактовых импульсов с регулируемой частотой, счетчик формирования адреса, счетчик циклов, последовательно соединенные блок постоянной памяти, аналого-цифровой умножитель, аналоговый интегратор со сбросом, блок выделения абсолютной величины сигнала, входную шину, выходную шину, шину установки начальных условий, где входы блока постоянной памяти подключены к выходам счетчика формирования адреса, входная шина подключена к аналоговому входу аналого-цифрового умножителя, а шина установки начальных условий соединена с установочным входом счетчика формирования адреса, с установочным входом счетчика циклов, с входом сброса аналогового интегратора со сбросом, введена вторая группа узлов, содержащая последовательно соединенные блок постоянной памяти, аналого-цифровой умножитель, аналоговый интегратор со сбросом, блок выделения абсолютной величины сигнала, а также введены аналоговый сумматор, схема И и сигнальная шина завершения цикла вычислений, причем входы блока постоянной памяти подключены к выходам счетчика формирования адреса, аналоговый вход аналого-цифрового умножителя подключен к входной шине, а вход сброса аналогового интегратора со сбросом подключен к шине установки начальных условий, входы аналогового сумматора подключены к выходам блоков выделения абсолютной величины сигнала, а выход аналогового сумматора подключен к выходной шине, входы схемы И подключены к выходам счетчика циклов, а выход схемы И подключен к сигнальной шине завершения цикла вычислений при данной частоте. Это позволяет повысить быстродействие устройства за счет исключения из устройства блока сдвига фазы и, соответственно, подбора начальной фазы сканирующего синусоидального сигнала, выполняемого упомянутым блоком. При этом объем вычислений в устройстве при формировании величины спектра при текущей частоте ω сокращается, соответственно, в (2π):Δφ раз.

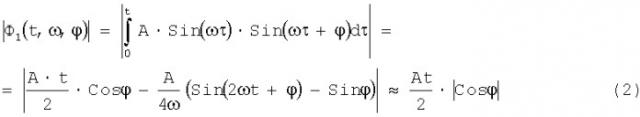

Вычисление амплитуд гармонических составляющих при текущей частоте ω без подбора начальной фазы, т.е. без использования блока сдвига фазы, осуществляется посредством двойного применения с известной формулы

В формуле (1) максимальное значение Ф(е,ω,φ) является амплитудным спектром, модуль величины которого пропорционален величинам амплитуд гармонических составляющих в исследуемом сигнале, f(τ) - исследуемый сигнал, Sin(ωτ+φ) - сканирующий синусоидальный сигнал с циклической частотой ω и начальной фазой φ, подлежащей подбору для обеспечения максимального значения величины Ф(t,ω,φ), τ - переменная интегрирования, t - текущее время. В рассматриваемом устройстве, в отличие от устройства-прототипа, вычисление максимальной величины (1) при заданных величинах t и ω осуществляется не методом подбора величины φ, а посредством двойного вычисления (1) при двух значениях начальной фазы φ в сканирующем синусоидальном сигнале, а именно, при некотором начальном значении φ и при φ+π/2, с последующим сложением модулей полученных результатов без подбора величины φ. Справедливость этого подхода имеет следующее обоснование. Так, если в исследуемом сигнале f(t) содержится синусоидальная составляющая А×Sin(ωt), где А - амплитуда этой составляющей, то справедливы следующие соотношения

Складывая эти результаты, мы имеем:

так как величина (|Cosφ|)+(|Sinφ|) при произвольных значениях φ находится в диапазоне 1 - 1.4. Таким образом, при выполнении упомянутых операций при фиксированных значениях t и ω мы получаем согласно (4) величину, пропорциональную искомой величине А, т.е. величине амплитуды А гармонической составляющей в исследуемом сигнале на частоте ω. При реализации изложенного метода величину t в (4) целесообразно полагать кратной целому количеству периодов синусоидального сигнала на частоте ω - целесообразность этого непосредственно следует из самого "внутреннего механизма" спектрального анализа, отражаемого формулой (1). При подобном выборе величин t достигается максимальное выделение в сигнале f(τ) гармоники на частоте ω и максимальное подавление гармоник в сигнале f(τ) на других частотах, включая шумы и помехи.

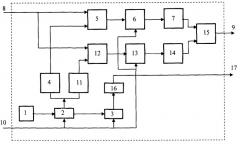

Структурная схема устройства изображена на чертеже.

Устройство для анализа сигналов в реальном масштабе времени содержит последовательно соединенные генератор тактовых импульсов 1 с регулируемой частотой, счетчик формирования адреса 2, счетчик циклов 3, последовательно соединенные блок постоянной памяти 4, аналого-цифровой умножитель 5, аналоговый интегратор со сбросом 6, блок выделения абсолютной величины сигнала 7, входную шину 8, шину установки начальных условий 10, где входы блока постоянной памяти 4 подключены к выходам счетчика формирования адреса 2, входная шина 8 подключена к аналоговому входу аналого-цифрового умножителя 5, а шина установки начальных условий 10 соединена с установочным входом счетчика формирования адреса 2, с установочным входом счетчика циклов 3, с входом сброса аналогового интегратора со сбросом 6, согласно изобретению введена вторая группа узлов, содержащая последовательно соединенные блок постоянной памяти 11, аналого-цифровой умножитель 12, аналоговый интегратор со сбросом 13, блок выделения абсолютной величины сигнала 14, а также введены аналоговый сумматор 15, схема И 16 и сигнальная шина 17 завершения вычислений при данной частоте, причем входы блока постоянной памяти 11 подключены к выходам счетчика формирования адреса 2, аналоговый вход аналого-цифрового умножителя 12 подключен к входной шине 8, а вход сброса аналогового интегратора со сбросом 13 подключен к шине установки начальных условий 10, входы аналогового сумматора 15 подключены к выходам блоков выделения абсолютной величины сигнала 7 и 14, а выход аналогового сумматора 15 подключен к выходной шине 9, входы схемы И 16 подключены к выходам счетчика циклов 3, а выход схемы И 16 подключен к сигнальной шине 17 завершения цикла вычислений при данной частоте.

Генератор тактовых импульсов 1 с регулируемой частотой - генератор прямоугольных импульсов любой известной конструкции с частотой F, регулируемой в заданном диапазоне частот F1≤F≤F2. Счетчики 2 и 3 - двоичные счетчики прямого счета, имеющие n1 и n2 двоичных разрядов соответственно. Счетчик 2 предназначен для формирования последовательностей двоичных адресов с разрядностью n1 в диапазоне значений от 00…0 до 11…1, а счетчик циклов 3 предназначен для подсчета количества сформированных последовательностей адресов в упомянутом диапазоне. Блоки постоянной памяти 4 и 11 предназначены для хранения в цифровом виде и, соответственно, последовательного функций y1(t)=Sin(ωt) и на периоде Т, где 0≤Т≤2π, - циклическая частота, t - текущее время. Эти блоки имеют по n1 входов, по m выходов, емкость по m - разрядных двоичных слоев и реализуются на основе микросхем БИС ПЗУ. Аналого-цифровые умножители 5 и 12 реализуются на основе множительных цифро-аналоговых преобразователей (ЦАП). Аналоговые интеграторы со сбросом 6 и 13, блоки выделения абсолютной величины сигнала 7 и 14 и сумматор 15 являются аналоговыми блоками и реализуются по одной из известных схем. Схема И 16 предназначена для фиксации момента завершения формирования требуемого количества к последовательностей двоичных адресов с разрядностью n1. При выработке требуемого количества последовательностей адресов (циклов) на счетчике циклов 3 формируется двоичный код, равный по величине требуемому количеству циклов. Единицы этого кода расположены в определенных и заранее известных разрядах, к которым изначально подключаются входы схемы И 16.

Работает устройство следующим образом. На генераторе тактовых импульсов 1 с регулируемой частотой вручную или с помощью микроЭВМ устанавливается частота F, обеспечивающая генерацию сигналов Sin(ωt) и на выходах блоков постоянной памяти 4 и 11 с заданной циклической частотой ω. Далее подается импульс на шину установки начальных условий 10, производящий сброс счетчика формирования адреса 2, счетчика циклов 3, аналоговых интеграторов со сбросом 6 и 13 и производится включение генератора тактовых импульсов 1. При включении генератора тактовых импульсов 1 на счетчике формирования адреса 2 последовательно во времени формируются n1-разрядные двоичные адреса в диапазоне от 00…0 до 11…1. Количество циклов формирования адресов в указанном диапазоне подсчитывается счетчиком циклов 3. По сформированным на счетчике формирования адреса 2 адресам из блоков постоянной памяти 4 и 11 выбираются хранящиеся в них значения синусоидальных сигналов Sin(ωt) и . На аналого-цифровых умножителях 5 и 12 формируются произведения f(t)·Sin(ωt) и . На аналоговых интеграторах со сбросом 6 и 13 формируются интегралы и . На блоках выделения абсолютной величины сигнала 7 и 14 формируются модули интегралов. На аналоговом сумматоре вычисляется сумма этих модулей, величина которой в виде напряжения поступает на выходную шину 9. При завершении генерации на блоках постоянной памяти 4 и 11 требуемого количества κ периодов синусоидальных сигналов, где величина κ, как отмечалось выше, вводится в устройство посредством соответствующего подключения входов схемы И 16 к выходам счетчика циклов 3, на сигнальную шину 17 завершения цикла вычислений при данной частоте ω с выхода схемы И 16 поступает сигнал. По этому сигналу производится считывание и, соответственно, запись величины выходного сигнала с шины 9 на соответствующее регистрирующее устройство. Величина считываемого выходного сигнала, согласно (4), пропорциональна величине амплитуды А синусоидальной составляющей при исходно установленной циклической частоте ω. При работе в автоматическом режиме, т.е. при управлении работой устройства с помощью микроЭВМ, сигнал с сигнальной шины 17 о завершении цикла вычислений используется также для установки счетчиков и интеграторов устройства в начальное состояние и в качестве сигнала для микроЭВМ о формировании очередной частоты ω.

Эффективность рассматриваемого устройства можно проиллюстрировать на следующем конкретном примере. Так, если даже в устройстве-прототипе подбор начальной фазы φ на интервале [0-2π] выполняется с достаточно крупным шагом , то за счет исключения подбора величины начальной фазы φ с указанным шагом быстродействие рассматриваемого устройства увеличивается в 10 раз, т.е. на порядок.

Список литературы

1. Патент РФ №2005610.

2. Патент РФ №2018144.

3. Авт. св. СССР №1812518.

Устройство для анализа сигналов в реальном масштабе времени, содержащее последовательно соединенные генератор тактовых импульсов с регулируемой частотой, счетчик формирования адреса, счетчик циклов, последовательно соединенные блок постоянной памяти, аналого-цифровой умножитель, аналоговый интегратор со сбросом, блок выделения абсолютной величины сигнала, входную шину, выходную шину, шину установки начальных условий, где входы блока постоянной памяти подключены к выходам счетчика формирования адреса, входная шина подключена к аналоговому входу аналого-цифрового умножителя, а шина установки начальных условий соединена с установочным входом счетчика формирования адреса, с установочным входом счетчика циклов, с входом сброса аналогового интегратора со сбросом, отличающееся тем, что в состав устройства введена вторая группа узлов, содержащая последовательно соединенные блок постоянной памяти, аналого-цифровой умножитель, аналоговый интегратор со сбросом, блок выделения абсолютной величины сигнала, а также введены аналоговый сумматор, схема И и сигнальная шина завершения цикла вычислений, причем входы блока постоянной памяти подключены к выходам счетчика формирования адреса, аналоговый вход аналого-цифрового умножителя подключен к входной шине, а вход сброса аналогового интегратора со сбросом подключен к шине установки начальных условий, входы аналогового сумматора подключены к выходам блоков выделения абсолютной величины сигнала, а выход аналогового сумматора подключен к выходной шине, входы схемы И подключены к выходам счетчика циклов, а выход схемы И подключен к сигнальной шине завершения цикла вычислений при данной частоте.