Коммутатор link-портов

Иллюстрации

Показать всеИзобретение относится к построению коммутируемых локальных сетей для обмена данными между вычислительными модулями параллельных вычислительных систем или распределенных вычислительных комплексов. Техническим результатом изобретения является коммутация данных, представленных в виде байтов, обеспечение множественности путей доставки сообщений, исключение зацикливания сообщений, исключение блокировки сообщений. Коммутатор LINK-портов, содержит N LINK-портов, N контроллеров LINK-портов, коммутационную матрицу, блок регистров, дешифратор протокола выдачи адреса, формирователь ответного сообщения, схема сравнения, константа, счетчик номера LINK-портов, формирователь RCP-2, в каждый LINK-порт дополнительно введены входной LINK-порт, входной буферный регистр, входной LINK-порт, счетчик выбора входного порта, счетчик тайм-аута выдачи, схема сравнения, константа, в каждый контроллер LINK-порта дополнительно введены узел модификации поля TL, два JK-триггера, три элемента ИЛИ, буферная память FIFO, управляющая машина состояний, регистр состояния, ОЗУ1 таблицы коммутации, мультиплексор, схема сравнения, константа, ОЗУ2, пять элементов И, узел контроля на нечет, счетчик слов, аккумулятор контрольной суммы, регистр первого заголовка, регистр третьего слова заголовка, узел проверки слов заголовка. 6 з.п. ф-лы 28 ил.

Реферат

Изобретение относится к построению коммутируемых локальных сетей для обмена данными между вычислительными модулями параллельных вычислительных систем или распределенных вычислительных комплексов.

Известен модульный масштабируемый коммутатор и способ распределения кадров в сети быстрого ETHERNET [1], выполненный в виде множества индивидуально программируемых однопортовых модулей связи для доступа к общей распределительной шине, при этом каждый однопортовый модуль связи содержит программируемый микроконтроллер, выполненный как блок управления доступом к передающей среде Ethernet (MAC), содержащий процессор с сокращенным набором команд (RISC CPU), и логическое устройство распределения кадров данных, предусматривающее обработку в реальном времени и передачу, на адресуемые порты назначения кадров данных Ethernet, поступающих на указанный однопортовый модуль связи, процесс передачи является последовательным и осуществляется в режиме «сохранить и переслать».

Недостатком данного модульного масштабируемого коммутатора является то, что он не может коммутировать данные, представленные в параллельном коде.

Локальные сети, являясь пакетными сетями, используют принцип временного мультиплексирования, то есть распределяют передающую среду во времени, поэтому кадры обрабатываются последовательно.

Известен организатор поля заголовка в сети системы обработки (Selective header field dispatch in a network processing system) [2], в типичных сетях которого используются коммутаторы для продвижения пакетизированных данных от одной точки соединения к другой, точки соединения сети типа коммутаторов используются в узлах организации сети, чтобы достичь наибольшей гибкости и больших функциональных возможностей, ячейка коммутатора, состоящая из входного порта, узла извлечения поля заголовка выходных данных, первой памяти данных, устройства потока входных данных, кадра преобразования входных данных, выходного интерфейса коммутатора, первого процессора сети, второго процессора сети, входного интерфейса коммутатора, узла извлечения поля заголовка входных данных, второй памяти данных, устройства потока выходных данных, кадра преобразования выходных данных, выходной порт, соединенный с первым выходом коммутатора, первый вход которого соединен со входом входного порта, выход которого соединен с первым входом устройства потока входных данных, первый выход которого соединен со входом первого процессора сети, выход которого соединен со вторым входом устройства потока входных данных, второй выход которого соединен со входом выходного интерфейса коммутатора, выход которого является вторым выходом ячейки коммутатора, второй вход которого соединен со входом входного интерфейса коммутатора, выход которого соединен со входом устройства потока выходных данных, выход которого соединен со входом выходного порта.

Недостатком данного организатора поля заголовка в сети системы обработки является то, что он не может коммутировать данные, представленные в параллельном коде. Локальные сети, являясь пакетными сетями, используют принцип временного мультиплексирования, то есть распределяют передающую среду во времени, поэтому кадры отрабатываются последовательно.

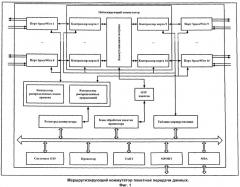

Известен маршрутизирующий коммутатор пакетной передачи данных (МСК-01) [3], состоящий из встроенного процессора, позволяющего организовать детальную обработку ошибочных ситуаций, динамический подбор скоростей передачи, мониторинг и администрирование работы, шестнадцати портов Space Wire, шестнадцати контроллеров портов, коммутационной матрицы, контроллера распределенных кодов времени, контроллера распределенных прерываний, ОЗУ пакетов, регистров коммутатора, блока обработки пакетов процессора, таблицы маршрутизации, системного ОЗУ, каналов прямого доступа М PORT контроллера, внешний 32-разрядный параллельный порт (МВА), предназначенный для подключения к МСК-01 внешнего процессора, соединенный с внутренней магистралью, соединенной с системным ОЗУ, с процессором, с каналами прямого доступа (М PORT), с регистрами коммутатора, с блоком обработки пакетов процессора, с таблицей маршрутизации, входы-выходы которой соединены с первыми входами-выходами шестнадцати контроллеров порта, вторые входы-выходы которых соединены с первыми входами-выходами шестнадцати портов Space Wire, группы выходов которых являются шестнадцатью группами выходов коммутатора, шестнадцать групп входов которого соединены с группами входов шестнадцати портов Space Wire, вторые входы-выходы которых соединены между собой и соединены с первыми входами-выходами контроллера распределенных кодов времени и контроллера распределенных прерываний, вторые входы-выходы контроллеров соединены с регистрами коммутатора, причем вход-выход блока обработки пакетов процессора соединен с первым входом-выходом ОЗУ пакетов, второй вход-выход которого соединен с первым входом-выходом коммутационной матрицы, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый, семнадцатый входы-выходы которой соединены с третьими входами-выходами шестнадцати контроллеров портов, причем группа входов-выходов канала прямого доступа (М PORT) является первой группой входов-выходов маршрутизирующего коммутатора, вторая группа входов-выходов которого соединена с внешним 32-х разрядным параллельным портом. Описанное устройство как наиболее близкое к предлагаемому принято за прототип и представлено на фиг.1.

Данный коммутатор не может коммутировать данные представленные в виде байтов.

Недостатком данного коммутатора является то, что он не может обеспечить множественность путей доставки сообщений при логическом способе адресации, для его работы необходимы внешние микросхемы ОЗУ и ПЗУ, у него нет механизма проверки времени жизни сообщений.

Задачей изобретения является коммутация данных, представленных в виде байтов, обеспечение множественности путей доставки сообщений, исключение зацикливания сообщений, введение механизма таймаутов для исключения блокировки сообщений.

Сущность заявляемого изобретения, возможность его осуществления и промышленного использования поясняются чертежами, представленными на фиг.2 - фиг.28, где:

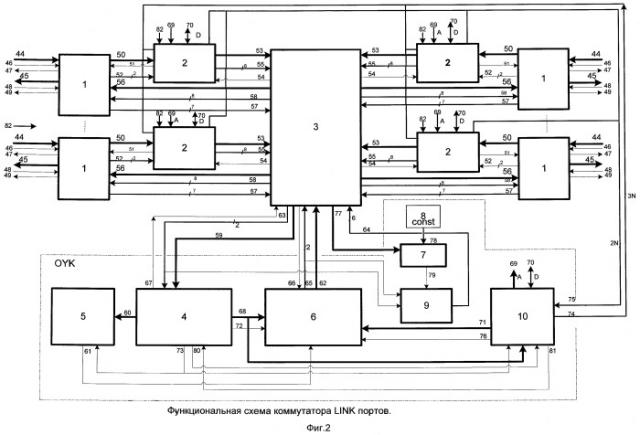

- на фиг.2 представлена функциональная схема коммутатора LINK-портов;

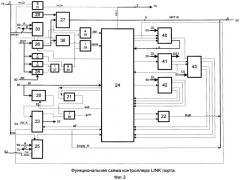

- на фиг.3 представлена функциональная схема контроллера LINK-порта;

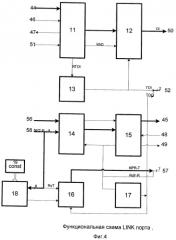

- на фиг.4 представлена функциональная схема LINK-порта;

- на фиг.5 представлена функциональная схема формирователя протокола RCP-2;

- на фиг.6 представлена функциональная схема формирователя ответного сообщения;

- на фиг.7 представлена функциональная схема счетчика слов и аккумулятора контрольной суммы;

- на фиг.8 представлена функциональная схема узла управления;

- на фиг.9 представлена коммутационная среда;

- на фиг.10 представлена структура LINK-интерфейса;

- на фиг.11 представлена таблица 1;

- на фиг.12 представлена временная диаграмма обмена данными;

- на фиг.13 представлен формат заголовка сообщения;

- на фиг.14 представлен формат запроса параметров;

- на фиг.15 представлен формат предоставления параметров;

- на фиг.16 представлен пример задания адресов;

- на фиг.17 представлен формат задания адреса ОУ;

- на фиг.18 представлен формат ответа ОУ при задании адреса;

- на фиг.19, 19а, 19б, 19в, 19г, 19д, 19е представлен алгоритм работы контроллера LINK-порта;

- на фиг.20, 20а, 206, 20в, 20г, 20д, 20е представлен алгоритм работы управляющей машины состояний (УМС);

- на фиг.21 представлен формат входных сообщений для таблиц коммутации;

- на фиг.22 представлен формат команд СМД;

- на фиг.23 представлен тип операции записи/модификации;

- на фиг.24 представлен формат выходных сообщений;

- на фиг.25 представлен формат ответного слова RPL;

- на фиг.26 представлено поле кода ошибки;

- на фиг.27 представлена временная диаграмма выполнения операции чтение - модификация - запись - чтение;

- на фиг.28 представлен алгоритм работы машины состояний узла управления.

Указанные преимущества заявляемого коммутатора LINK-портов перед прототипом достигаются за счет того, что в коммутатор LINK-портов, содержащий N LINK-портов 1, N контроллеров LINK-портов 2, коммутационную матрицу 3, блок регистров 4, дополнительно введены дешифратор протокола выдачи адреса 5, формирователь ответного сообщения 6, схема сравнения 7, константа 8, счетчик номера LINK-портов 9, формирователь 10 протокола RCP-2, в каждый LINK-порт 1 дополнительно введены входной LINK-порт 11, входной буферный регистр 12, счетчик тайм-аута приема 13, выходной буферный регистр 14, выходной LINK-порт 15, счетчик выбора входного порта 16, счетчик тайм-аута выдачи 17, схема сравнения 18, константа 19, в каждый контроллер LINK-порта 2 дополнительно введены узел модификации поля TL 20, первый JK-триггер 21, второй JK-триггер 22, буферная память FIFO 23, управляющая машина состояний 24, регистр состояния 25, ОЗУ1 таблицы коммутации 26, мультиплексор 27, схема сравнения 28, константа 29, ОЗУ2 30, первый 31 элемент И, второй 32 элемент И, третий 33 элемент И, четвертый 34 элемент И, пятый 35 элемент И, узел контроля на нечет 36, первый 37 элемент ИЛИ, второй 38 элемент ИЛИ, третий 39 элемент ИЛИ, счетчик слов и аккумулятор контрольной суммы 40, регистр первого слова заголовка 41, регистр третьего слова заголовка 42, узел проверки слов заголовка 43, причем N первые 44 группы входов коммутатора LINK-портов соединены с N первыми группами входов N LINK-портов 1, N первые группы выходов которых являются N группами выходов 45 коммутатора LINK-портов, N первые 46 входы которого соединены с N первыми входами N LINK-портов 1, N первые 47 выходы которых являются N первыми выходами коммутатора LINK-портов, N вторые 48 входы которого соединены с N вторыми входами N LINK-портов 1, N вторые выходы которых являются N вторыми 49 выходами коммутатора LINK-портов, причем N вторые 50 группы выходов N LINK-портов 1 соединены с N группами входов N контроллеров LINK-портов 2, выходы 51 которых соединены с третьими входами N LINK-портов 1, третья 52 группа выходов которых соединена со вторыми группами входов N контроллеров LINK-портов 2, первые 53 группы выходов которых соединены с N первыми группами входов коммутационной матрицы 3, N выходы 54 которой соединены с первыми входами N контроллеров LINK-портов 2, вторые 55 группы выходов которых соединены с N вторыми группами входов коммутационной матрицы 3, N первые 56 группы выходов которой соединены со вторыми группами входов N LINK-портов 1, четвертые 57 группы выходов которых соединены с N третьими группами входов коммутационной матрицы 3, N вторые 58 группы выходов которой соединены с третьими группами входов N LINK-портов 1, причем четвертая 59 группа выходов коммутационной матрицы 3 соединена с группой входов блока регистров 4, первая 60 группа выходов которого соединена с группой входов дешифратора протокола выдачи адреса 5, выход 61 которого соединен с первым входом формирователя ответного сообщения 6, первая 62 группа выходов которого соединена с четвертой группой входов коммутационной матрицы 3, пятая 63 группа выходов которой соединена со второй группой входов блока регистров 4 и первым входом счетчика номера LINK-портов 9, группа выходов 64 которого соединена с пятой группой входов коммутационной матрицы 3, шестая 65 группа входов которой соединена со вторым входом счетчика номера LINK-портов 9 и второй группой выходов формирователя ответного сообщения 6, второй 66 вход которого соединен с первым выходом коммутационной матрицы 3, первый 67 вход которой соединен с первым выходом блока регистров 4, вторая 68 группа выходов которого соединена с первыми группами входов формирователя ответного сообщения 6 и формирователя 10 протокола RCP-2, первая 69 группа выходов которого соединена с третьими группами входов N контроллеров LINK-портов 2, группы входов-выходов 70 которых соединены с группой входов-выходов формирователя протокола RCP-2 10, вторая 71 группа выходов которого соединена со второй группой входов формирователя ответного сообщения 6, третий 72 вход которого соединен с первым выходом блока регистров 4, второй 73 выход которого соединен с дешифратором протокола выдачи адреса 5 и с первым входом формирователя протокола RCP-2 10, третья 74 группа выходов которого соединена с четвертыми группами входов N контроллеров LINK-портов 2, третьи 75 группы выходов которых соединены со второй группой входов формирователя протокола RCP-2 10, первый 76 выход которого соединен с четвертым входом формирователя ответного сообщения 6, причем шестая 77 группа выходов коммутационной матрицы 3 соединена с первой группой входов схемы сравнения 7, вторая 78 группа входов которой соединена с константой 8, а выход 79 - с третьим входом счетчика номера LINK-портов 9, причем третий 80 выход блока регистров 4 соединен со вторым входом формирователя 10 протокола RCP-2, второй 81 выход которого соединен со входом блока регистров 4, N вторые 82 группы входов коммутатора LINK-портов соединены с пятыми группами входов N контроллеров LINK-портов 2.

Каждый LINK-порт 1 содержит входной LINK-порт 11, входной буферный регистр 12, счетчик тайм-аута приема 13, выходной буферный регистр 14, выходной LINK-порт 15, счетчик выбора входного порта 16, счетчик тайм-аута выдачи 17, схему сравнения 18, константу 19, группа выходов которой соединена с первой группой входов схемы сравнения 18, вторая группа входов которой соединена с первой группой входов выходного буферного регистра 14 и является третьей 58 группой входов LINK-порта, вторая 56 группа входов которого соединена со второй группой входов выходного буферного регистра 14, группа выходов которого соединена с группой входов выходного LINK-порта 15, группа выходов которого является первой 45 группой выходов LINK-порта, вторая 50 группа выходов которого является выходами входного буферного регистра 12, группа входов которого соединена с группой выходов входного LINK-порта 11, группа входов которого является первой 44 группой входов LINK-порта 1, первый вход которого является первым 46 входом входного LINK-порта 11, первый выход которого соединен со входом входного буферного регистра 12, второй вход которого соединен с выходом счетчика тайм-аута приема и является первым сигналом третьей 52 группы выходов LINK-порта 1, второй сигнал которой соединен с первым входом счетчика выбора входного порта 16 и выходом счетчика тайм-аута выдачи 17, вход счетчика тайм-аута приема 13 соединен со вторым выходом входного LINK-порта 11, третий выход которого является первым 47 выходом LINK-порта 1, второй 51 вход которого соединен со вторым входом входного LINK-порта 11, причем восьмой сигнал третьей 58 группы входов LINK-порта 1 соединен со вторым входом счетчика выбора входного порта 16, группа выходов которого является шестью сигналами четвертой 57 группы выходов LINK-порта 1, седьмой сигнал которой соединен со входами счетчика тайм-аута выдачи 17 и выходного буферного регистра 14 и первым выходом выходного LINK-порта 15, второй выход которого является вторым выходом 49 LINK-порта 1, третий вход которого соединен со вторым входом выходного LINK-порта 15, причем выход схемы сравнения 18 соединен с третьим входом счетчика выбора входного порта 16.

Каждый контроллер LINK-порта 2 содержит узел модификации поля TL 20, первый JK-триггер 21, второй JK-триггер 22, буферную память FIFO 23, управляющую машину состояний 24, регистр состояния 25, ОЗУ1 таблицы коммутации 26, ОЗУ2 30, мультиплексор 27, узел контроля на нечет 36, счетчик слов и аккумулятор контрольной суммы 40, регистр первого слова заголовка 41, регистр третьего слова заголовка 42, узел проверки слов заголовка 43, схему сравнения 28, константу 29, первый 31 элемент И, второй 32 элемент И, третий 33 элемент И, четвертый 34 элемент И, пятый 35 элемент И, первый 37 элемент ИЛИ, второй 38 элемент ИЛИ, третий 39 элемент ИЛИ, выход которого соединен с первым входом управляющей машины состояний 24, первый выход которой соединен со входом ОЗУ1 таблицы коммутации 26, группа выходов которого соединена с первыми группами входов мультиплексора 27 и узла контроля на нечет 36, выход которого соединен с первым входом третьего 39 элемента ИЛИ, второй вход которого соединен со входом мультиплексора 27, с инверсным входом пятого 35 элемента И, с выходом четвертого 34 элемента И, первый вход которого соединен с выходом второго 32 элемента И, группа входов DST которого соединена с группами входов DST ОЗУ1 таблицы коммутации 26, третьего 33 элемента И, схемы сравнения 28 и выходом регистра первого слова заголовка 41, группа входов DI которого соединена с группами входов DI управляющей машины состояний 24, узла модификации TL 20, счетчика слов и аккумулятора контрольной суммы 40, регистра третьего слова заголовка 42, узла проверки слов заголовка 43 и является первой 50 группой входов контроллера LINK-порта 2, первая 53 группа выходов которого является группой выходов буферной памяти FIFO 23, первый выход которой соединен с первым входом второго 38 элемента ИЛИ, выход которого является первым 51 выходом контроллера LINK-порта 2, вторая 55 группа выходов которого соединена с группой выходов NPT_R мультиплексора 27, со вторым выходом буферной памяти FIFO 23 и с выходом второго 22 JK-триггера, первый и второй входы которого соединены со вторым и третьим выходами управляющей машины состояний 24, четвертый и пятый выходы которой соединены с первым и вторым входами первого 21 JK-триггера, выход которого соединен со вторым входом второго 38 элемента ИЛИ, причем третья 75 группа выходов контроллера LINK-порта 2 состоит из первого сигнала с выхода первого 31 элемента И и второго сигнала с шестого выхода управляющей машины состояний 24, седьмой, восьмой и девятый выходы которой соединены с первым, вторым и третьим входами счетчика слов и аккумулятора контрольной суммы 40, первый выход которого соединен с первым входом узла проверки слов заголовка 43, первый, второй, третий, четвертый выходы которого соединены со вторым, третьим, четвертым, пятым входами управляющей машины состояний 24 соответственно, десятый выход которой соединен со входом узла модификации TL 20, группа выходов которого соединена с группой входов буферной памяти FIFO 23, второй выход которой соединен с шестым входом управляющей машины состояний 24, восьмой выход которой соединен с первым входом буферной памяти FIFO 23, второй вход которой является первым 54 входом контроллера LINK-порта 2, вторая 52 группа входов которого соединена с первым и вторым входами регистра состояния 25, группа входов-выходов которого соединена с группой входов-выходов ОЗУ2 30 и является группой входов-выходов 70 контроллера LINK-порта 2, третья 69 группа входов которого соединена с первыми группами входов ОЗУ2 30 и регистра состояния 25, выход которого соединен с седьмым входом управляющей машиной состояний 24, одиннадцатый выход которой соединен со входом регистра первого слова заголовка 41, первый выход которого соединен со вторым входом узла проверки слов заголовка 43, третий вход которого соединен со вторым выходом регистра первого слова заголовка 41 и с восьмым входом управляющей машины состояний 24, двенадцатый выход которого соединен с входом регистра третьего слова заголовка 42, первый, второй, третий, четвертый выходы которого соединены с девятым, десятым, одиннадцатым, двенадцатым входами управляющей машины состояний 24 соответственно, тринадцатый вход которой соединен с выходом пятого 35 элемента И, первый вход которого соединен с первым входом узла контроля на нечет 36 и первым выходом ОЗУ1 таблицы коммутации 26, второй выход которого соединен с первым входом первого 31 элемента И, второй вход которого является первым сигналом четвертой 74 группы входов, второй и третий сигналы которой соединены со второй группой входов ОЗУ2 30, а четвертый сигнал соединен с третьим входом регистра состояния, причем константа 29 соединена со второй группой входов мультиплексора 27, пятая 82. группа входов контроллера LINK-порта 2 соединена с группой входов схемы сравнения 28, выход которой соединен с первым входом первого 37 элемента ИЛИ, второй вход которого соединен с выходом третьего 33 элемента И, третий выход ОЗУ1 таблицы коммутации 26 соединен со вторым входом узла контроля на нечет 36, вторая группа входов управляющей машины состояний 24 соединена с группой выходов счетчика слов и аккумулятора контрольной суммы 40, причем тринадцатый выход управляющей машины состояний 24 соединен с третьим входом буферной памяти FIFO 23.

Формирователь 10 протокола RCP-2 содержит преобразователь данных 83, узел выполнения команд 84, узел управления 85, счетчик тайм-аута 86, формирователь ответного массива 87, группа выходов которого является второй 71 группой выходов формирователя 10 протокола RCP-2, первая 69 группа выходов которого соединена с первой группой выходов узла управления 85, вторая группа выходов которого соединена с первой группой входов счетчика тайм-аута 86 и является третьей 74 группой выходов формирователя 10 протокола RCP-2, группа входов-выходов 70 которого соединена с первой группой входов формирователя ответного массива 87 и группой входов-выходов узла выполнения команд 84, группа входов которого соединена с группой выходов преобразователя данных 83, группа входов которого соединена с группой входов узла управления 85 и является первой 68 группой входов формирователя 10 протокола RCP-2, вторая 75 группа входов которого соединена со вторыми группами входов узла управления 85 и счетчика тайм-аута 86, выход которого соединен с первым входом узла управления 85, первый выход которого соединен с первым входом узла выполнения команд 84, причем второй выход узла управления 85 соединен с первым входом формирователя ответного массива 87 и является первым 76 выходом формирователя 10 протокола RCP-2, первый 73 вход которого соединен со вторым входом узла управления 85, третий выход которого является вторым 81 выходом формирователя 10 протокола RCP-2, второй вход которого соединен со входом преобразователя данных 83 и третьим входом узла управления 85, причем два младших сигнала первой группы выходов узла управления 85 соединены со второй группой входов формирователя ответного массива.

Формирователь ответного сообщения 6 содержит мультиплексор 88, аккумулятор контрольной суммы (KΣ) 89, буферный регистр 90, ОЗУ 91, первая группа выходов которого является первой 62 группой выходов формирователя ответного сообщения 6, вторая 65 группа выходов которого является выходом буферного регистра 90 и выходом ОЗУ 91, группа входов которого соединена с группой выходов буферного регистра 90, группа входов которого соединена с группой входов аккумулятора KΣ 89 и группой выходов мультиплексора 88, первая группа входов которого является первой 68 группой входов формирователя ответного сообщения 6, вторая 71 группа входов которого соединена со второй группой входов мультиплексора 88, первый и второй входы которого являются первым 61 и четвертым 76 входами соответственно формирователя ответного сообщения 6, третья группа входов мультиплексора 88 соединена с группой выходов аккумулятора KΣ 89, первый вход которого является третьим 72 входом формирователя ответного сообщения 6, второй 66 вход которого соединен со входом ОЗУ 91.

Счетчик слов и аккумулятор KΣ 40 содержит сумматор 92 по mod 2, регистр 93, счетчик 94 и узел 95 анализа на «0», выход которого является первым выходом счетчика слов и аккумулятора KΣ 40, группа выходов которого соединена с группой выходов счетчика 94, первый вход которого является первым входом счетчика слов и аккумулятора KΣ 40, второй вход которого соединен с первым входом регистра 93, второй вход которого соединен со вторым входом счетчика 94 и является третьим входом счетчика слов и аккумулятора KΣ 40, группа входов 50 которого соединена с первой группой входов сумматора 92 по mod 2, вторая группа входов которого соединена с группой входов узла 95 анализа на «0» и группой выходов регистра 93, группа входов которого соединена с группой выходов сумматора 92 по mod 2.

Узел управления 85 содержит регистр 96, машину состояний 97, счетчик адреса 98, счетчик обмена 99, первый 100 элемент ИЛИ, второй 101 элемент ИЛИ, выход которого является третьим сигналом второй группы выходов 74 узла управления 85, первый сигнал которой соединен с выходом первого 100 элемента ИЛИ, первый вход которого соединен с первым выходом машины состояний 97, второй выход которой соединен со вторым входом первого 100 элемента ИЛИ и является вторым сигналом второй группы выходов 74 узла управления 85, четвертый сигнал которой соединен с третьим выходом машины состояний 97, четвертый выход которой соединен с первым входом второго 101 элемента ИЛИ и третьим входом первого 100 элемента ИЛИ, четвертый вход которого соединен с пятым выходом машины состояний 97, вторым входом второго 101 элемента ИЛИ и является первым выходом узла управления 85, первая 69 группа выходов которого соединена с группой выходов счетчика адреса 98, первый вход которого соединен с первым входом счетчика обмена 99 и является шестым выходом машины состояний 97, первый, второй, третий входы которой соединены с первым, вторым, третьим выходами регистра 96 соответственно, четвертый выход которого является вторым 76 выходом узла управления 85, третий 81 выход которого соединен с выходом счетчика обмена 99 и четвертым входом машины состояний 97, пятый и шестой входы которой являются первым и вторым сигналами второй 75 группы входов узла управления 85, первая 68 группа входов которого соединена с группой входов регистра 96, первая группа выходов которого соединена с группой входов счетчика обмена 99, второй вход которого соединен со вторым входом счетчика адреса 98, первым входом регистра 96 и является третьим 80 входом узла управления 85, второй 73 вход которого соединен со вторым входом регистра 96, вторая группа выходов которого соединена с группой входов счетчика адреса 98, причем первый вход узла управления 85 соединен с седьмым входом машины состояний 97.

Коммутатор LINK-портов работает следующим образом.

Коммутатор LINK-портов предназначен для создания коммутационной среды обмена пакетными сообщениями по LINK-интерфейсам в программно-аппаратных комплексах на основе процессоров ряда «Мультикор». [4]

Среда передачи информации состоит из набора оконечных устройств (ОУ), соединенных между собой через коммутаторы (К) LINK-портов. Коммутационная среда представлена на фиг.9.

Каждое оконечное устройство имеет свой уникальный адрес ОУ, по которому осуществляется его идентификация. В качестве ОУ могут выступать LINK-интерфейсы, входящие в состав процессоров, контроллеров памяти, контроллеров устройств ввода-вывода. Если какое-либо устройство имеет несколько LINK-интерфейсов (так процессор МС-24 [4] имеет 4 LINK-порта и, соответственно, 2 LINK-интерфейса), то каждый из интерфейсов является отдельным ОУ и имеет свой адрес. LINK-интерфейс состоит из двух LINK-портов, соответствующих описанию процессорного ряда «Мультикор».

В паре LINK-портов, составляющих интерфейс, один порт предназначен для выдачи информации (выходной порт 15), другой - для приема информации (входной порт 11). Направление работы порта жестко задается аппаратно или программно при инициализации системы и в процессоре работы не изменяется.

Информация через LINK-порты передается 32-х разрядными словами побайтно, начиная со старшего байта слова.

Структура интерфейса представлена на фиг.10. Состав интерфейсных сигналов и их назначение приведены в таблице 1, представленной на фиг.11. Временная диаграмма обмена данными приведена на фиг.12.

Данные передаются из выходного порта 15 во входной 32-х разрядными словами побайтно (по 4 байта начиная со старшего). Передача выходным портом 15 нового байта осуществляется по переднему фронту тактовой частоты LCLK 49. Задний фронт частоты LCLK 46 используется входным портом 11 для приема байта данных.

Входной порт 11 устанавливает сигнал LACK 47 при наличии готовности к приему следующего слова. Выходной порт 15 стробирует сигнал LACK 48 в момент выдачи нового слова. Если сигнал LACK 48 снят, то выходной порт 15 приостанавливает выдачу нового слова. Сигнал LCLK 49 при этом продолжает выдаваться высоким уровнем, а на линиях LDAT [7:0] 45 продолжается выдача старшего байта. По установке входным портом 11 сигнала LACK 47 выходной порт 15 вырабатывает спадающий фронт сигнала LCLK и продолжает выдачу слова.

В этом случае, если буфер выдачи выходного порта 15 пуст, то сигнал LCLK 49 после выдачи последнего слова остается снятым независимо от состояния сигнала LACK 48.

Адреса ОУ задаются любым образом, обеспечивающим однозначность и уникальность адреса в системе. Как вариант, ОУ могут получать свои адреса от коммутатора LINK-портов, к которому они подключены. В этом случае адрес ОУ состоит из адреса коммутатора LINK-порта и номера интерфейса коммутатора LINK-порта, к которому подключен ОУ.

Все ОУ в системе равноправны и могут по своей инициативе посылать сообщения другим ОУ. В то же время в системе могут присутствовать ОУ, которые посылают сообщения только в ответ на поступившее к ним сообщение - запрос. Как правило, это ОУ, входящее в состав контроллеров памяти и контроллеров ввода-вывода.

Коммутаторы LINK-портов предназначены для маршрутизации сообщений от ОУ - источника до ОУ - приемника сообщения. Для управления маршрутизацией в коммутаторах LINK-портов имеются таблицы маршрутизации. Каждому интерфейсу коммутатора LINK-портов соответствует своя таблица, в которой указывается, на какой выходной порт коммутатора LINK-порта выдавать сообщение для указанного в сообщении адреса ОУ получателя.

Сообщение - логически завершенная и неразрывная порция информации. Сообщение состоит из заголовка сообщения и необязательного тела сообщения. Заголовок сообщения содержит от 5 до 64-х слов. Тело сообщения содержит от 0 до 65536 слов. Заголовок полностью буферизуется в коммутаторе, проверяется на достоверность и допустимость, после чего все сообщение начинает передаваться на выходной порт.

Коммутатор LINK-портов должен проверять достоверность заголовка путем проверки полей, выделенных на фиг.13 серым фоном. Если хотя бы в одном из выделенных полей зафиксировано нарушение формата, то заголовок игнорируется и во входном потоке данных, идущем после слова, в котором зафиксировано нарушение формата, ищется новый заголовок. Если заголовок признан достоверным, то проверяются на допустимость поля, DST и TL. Если зафиксирована недопустимость одного из этих полей, то игнорируется сообщение целиком, т.е. и заголовок и тело сообщения, после чего во входном потоке данных, идущем после сообщения, ищется новый заголовок. Формат заголовка сообщения представлен на фиг.13.

Заголовок содержит:

Слово 0 - Признак начала заголовка

Должен содержать 0xАА55АА55, предназначен для первоначального выделения заголовка из поступающего на входной порт потока информации. Окончательное выделение заголовка из потока информации считается завершенным после проверки коммутатором достоверности заголовка путем проверки других полей заголовка.

Слово 1 - Описатель получателя сообщения

- байт 0: DST - адрес ОУ - получателя сообщения. Используется коммутаторами для определения номера выходного порта на который необходимо передать сообщение. Если указанный номер не содержится в таблице маршрутизации входного порта коммутатора, сообщение игнорируется;

- байт 1: зарезервирован, должен содержать 0x00, нарушение этого условия считается нарушением формата заголовка и приводит к его игнорированию;

- байт 2: PID - описатель вложенного протокола для ОУ - получателя сообщения (определяется соглашениями для конкретных ОУ);

- байт 3 имеет следующие поля:

- TL - текущее время жизни сообщения, определяет количество коммутаторов через которое может пройти сообщение. В каждом коммутаторе из содержимого данного поля вычитается единица. Если на коммутатор поступило сообщение с нулевым полем TL, то сообщение игнорируется.

Поле TL используется для ограничения распространения сообщений в тех случаях, когда из-за неправильной настройки таблиц коммутации в коммутационной среде образуются замкнутые петли, по которым сообщение могло бы передаваться бесконечно.

Поле TL это единственное поле заголовка, которое изменяется при прохождении через коммутатор. Для того, чтобы избежать пересчета контрольной суммы в коммутаторе (которая рассчитывается как поразрядное сложение по mod 2 всех слов заголовка) данное поле дублируется в слове 3 заголовка. При одновременном изменении двух идентичных полей контрольная сумма не изменяется.

- 00RQ - поле признаков, где

Q - reQuest - данный признак должен быть установлен, если на данное сообщение ОУ - приемником сообщения должно быть выдано ответное сообщение в адрес ОУ - источника сообщения;

R - Reply - признак ответного сообщения.

В поле признаков может быть установлен только один из признаков Q или R (или ни одного), старшие два разряда поля признаков должны быть нулевыми. Нарушение данного условия считается нарушением формата заголовка и приводит к его игнорированию.

Слово 2 - Описатель источника сообщения

- байт 0: SRC - адрес ОУ - источника сообщения, используется ОУ - получателем для формирования ответного сообщения;

- байт 1: зарезервирован, должен содержать 0х00, нарушение этого условия считается нарушением формата заголовка и приводит к его игнорированию;

- байт 2: PIS - описатель протокола для ОУ - источника сообщения. Как правило, указанный в данном поле протокол должен быть использован для выдачи ответного сообщения и совпадает с PID;

- байт 3 имеет следующие поля:

- TLI - исходное время жизни сообщения - как правило, определяет через какое количество коммутаторов может пройти ответное сообщение. Данное поле в коммутаторе не изменяется и используется ОУ - получателем для формирования ответного сообщения. ОУ - получатель в поле TL ответного сообщения записывает значение из поля TLI исходного сообщения, а в поле TLI ответного сообщения - значение из поля TL исходного сообщения;

- 00QR - поле признаков

Содержимое данного поля должно соответствовать признакам, установленным в описателе получателя сообщения. Нарушение данного условия считается нарушением формата заголовка и приводит к его игнорированию.

В целом формат описателя источника сообщения полностью соответствует формату описателя приемника сообщения, с тем чтобы использовать его в качестве такового при выдаче ОУ - получателем ответного сообщения, для чего достаточно поменять слова 1 и 2 местами.

Слово 3 - описатель сообщения

- байты 0 и 1: BL/Parameter 0 - Длина тела сообщения/Параметр.

Поле BL содержит длину тела сообщения в словах минус 1, если разряд В поля признаков установлен, и произвольный параметр, если разряд В сброшен. Максимальное количество слов в теле сообщения равно 65536 (BL=0×FFFF).

В качестве параметра при сброшенном разряде В рекомендуется использовать информацию о требуемой длине тела в ответном сообщении.

- байт 2: HL - длина заголовка

Поле HL содержит длину заголовка, начиная с признака начала заголовка и завершая контрольной суммой минус 1. Заголовки с количеством слов менее 5 (HL<0×04) или более 64 (HL>0×3F) коммутатором игнорируется.

- байт 3 содержит следующие поля:

- TL - копия соответствующего поля из описателя получателя сообщения. Несовпадение двух копий полей является нарушением формата заголовка и приводит к его игнорированию.

- ABCD - поле признаков,

А - Address. Признак должен быть установлен, если в заголовке присутствует необязательный параметр Mem_Address - адрес памяти в составе ОУ. Разряд А должен быть установлен именно в том случае, когда слово параметра используется ОУ в качестве адреса памяти, так как само наличие параметра/параметров определяется длиной заголовка через поле HL. Данный разряд введен для унифицированного обращения к адресам памяти в составе ОУ;

В - Body - признак наличия тела сообщения.

При установленном разряде В поле BL содержит длину тела сообщения, при сброшенном - произвольный параметр.

С - Custom - резервный признак.

D - Delete - признак удаления заголовка сообщения. При установке данного признака коммутатор передает на выходной порт только тело сообщения. Заголовок сообщения может быть также удален коммутатором независимо от признака D, если об этом есть указания в таблице маршрутизации коммутатора.

Слова 4-HL-1 - Параметры

Формат необязательных параметров и, в частности, адреса памяти ОУ Mem_Address должен определяться соглашениями для конкретных ОУ.

Слово HL - Контрольная сумма

Контрольная сумма CRC подсчитывается методом поразрядного сложения по модулю 2 (исключающего ИЛИ) всех