Демодулятор фазоманипулированных сигналов

Иллюстрации

Показать всеИзобретение относится к радиотехнике и может быть использовано в приемных устройствах для демодуляции фазоманипулированных сигналов, использующих классические способы формирования опорного напряжения. При этом устраняется существенный недостаток этих способов - явление обратной работы. Сущность изобретения заключается в использовании двух элементов задержки, двух фазовращателей, трех усилителей с прямым и инверсным выходами, трех коммутаторов и суммирующего усилителя-ограничителя для устранения инверсии фазы, а также трех дополнительных фазовых детекторов, трех пороговых устройств и трех счетных триггеров для индикации и управления поворотом фазы. 1 ил.

Реферат

Изобретение относится к радиотехнике и может быть использовано в приемных устройствах для демодуляции фазоманипулированных сигналов.

Известно устройство для демодуляции фазоманипулированных сигналов, описанное в книге «Пенин П.И. Системы передачи цифровой информации. Учебное пособие для вузов. М., Сов. Радио, 1976, с.152», содержащее объединенные по входу фазовый детектор, вход и выход которого являются входом и выходом устройства соответственно, и устройство формирования опорного напряжения, выход которого подключен к второму входу фазового детектора. Недостатком устройства является низкая помехоустойчивость, характеризующаяся тем, что под воздействием помех полярность выходного сигнала может меняться на инверсную, что приводит к ошибочному приему комбинации передаваемых символов.

Известно также устройство для демодуляции фазоманипулированных сигналов по авторскому свидетельству (АС) СССР №1483666, М. Кл4 H04L 27/22, содержащее последовательно соединенные формирователь меандра, вход которого является входом устройства, сумматор по модулю два и D-триггер, выход которого является выходом устройства, а D-вход соединен с выходом формирователя меандра, а также последовательно соединенные умножитель частоты на два, вход которого соединен с входом формирователя меандра, формирователь тактовых импульсов и регистр сдвига, выход которого соединен с вторым входом сумматора по модулю два, а второй вход соединен с выходом формирователя меандра. Недостатком устройства является низкая помехоустойчивость в моменты низкого уровня входного сигнала (моменты нахождения синусоиды вблизи нуля), в этом случае воздействие помехи на входе формирователя меандра приведет к появлению на D-входе триггера паразитных импульсов и к неправильному приему кодовой комбинации.

Наиболее близким аналогом является устройство, описанное в книге «Пенин П.И. Системы передачи цифровой информации. Учебное пособие для вузов. М., Сов. Радио, 1976, с.152», содержащее объединенные по входу фазовый детектор, вход и выход которого являются входом и выходом устройства соответственно, и устройство формирования опорного напряжения.

Для улучшения помехоустойчивости предложен демодулятор фазоманипулированных сигналов, содержащий объединенные по входу фазовый детектор, первый вход и выход которого являются входом и выходом устройства соответственно, и устройство формирования опорного напряжения, отличающийся тем, что в него введены последовательно соединенные первый усилитель, вход которого подключен к выходу устройства формирования опорного напряжения, первый коммутатор, суммирующий усилитель-ограничитель, выход которого подключен к второму входу фазового детектора, причем инверсный выход первого усилителя подключен к второму входу первого коммутатора, последовательно соединенные первый элемент задержки, вход которого подключен к выходу устройства формирования опорного напряжения, первый фазовращатель, второй усилитель и второй коммутатор, выход которого подключен к второму входу суммирующего усилителя-ограничителя, а инверсный выход второго усилителя подключен к второму входу второго коммутатора, последовательно соединенные второй элемент задержки, вход которого подключен к выходу первого элемента задержки, второй фазовращатель, третий усилитель, третий коммутатор, выход которого подключен к третьему входу суммирующего усилителя-ограничителя, а инверсный выход третьего усилителя подключен к второму входу третьего коммутатора, последовательно соединенные второй фазовый детектор, первый вход которого подключен к выходу суммирующего усилителя-ограничителя, а второй вход к выходу третьего коммутатора, первое пороговое устройство, первый счетный триггер, выход которого подключен к управляющему входу третьего коммутатора, последовательно соединенные третий фазовый детектор, первый вход которого подключен к выходу суммирующего усилителя-ограничителя, а второй вход - к выходу второго коммутатора, второе пороговое устройство, второй счетный триггер, выход которого подключен к управляющему входу второго коммутатора, последовательно соединенные четвертый фазовый детектор, первый вход которого подключен к выходу суммирующего усилителя-ограничителя, а второй вход - к выходу первого коммутатора, третье пороговое устройство, третий счетный триггер, выход которого подключен к управляющему входу первого коммутатора.

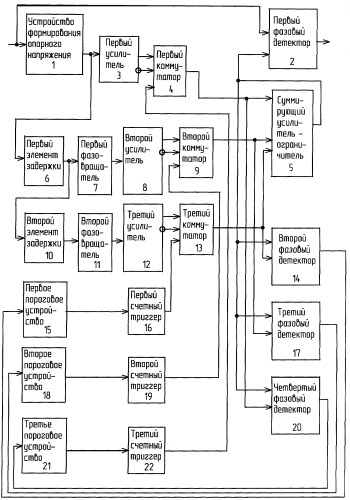

На чертеже приведена схема устройства. На ней изображены:

1 - устройство формирования опорного напряжения;

2, 14, 17, 20 - первый, второй, третий и четвертый фазовые детекторы соответственно;

4, 9, 13 - первый, второй и третий коммутаторы соответственно;

5 - суммирующий усилитель-ограничитель;

15, 18, 21 - первое, второе и третье пороговые устройства

соответственно;

6, 10 - первый и второй элементы задержки соответственно;

7, 11 - первый и второй фазовращатели соответственно;

16, 19, 22 - первый, второй и третий счетные триггеры соответственно.

Демодулятор содержит: устройство формирования опорного напряжения 1, первый фазовый детектор 2, первый усилитель 3, первый коммутатор 4, суммирующий усилитель-ограничитель 5, первый элемент задержки 6, первый фазовращатель 7, второй усилитель 8, второй коммутатор 9, второй элемент задержки 10, второй фазовращатель 11, третий усилитель 12, третий коммутатор 13, второй фазовый детектор 14, первое пороговое устройство 15, первый счетный триггер 16, третий фазовый детектор 17, второе пороговое устройство 18, второй счетный триггер 19, четвертый фазовый детектор 20, третье пороговое устройство 21, третий счетный триггер 22.

Устройство работает следующим образом. В исходном состоянии первый 16, второй 19 и третий 22 счетные триггеры установлены в нулевое состояние. Первый 4, второй 9, третий 13 коммутаторы установлены таким образом, что передают на выход сигналы с прямых выходов первого 3, второго 8 и третьего 12 усилителей. На входах второго 14, третьего 17 и четвертого 20 фазовых детекторов присутствуют синфазные сигналы и на их выходах установлен низкий уровень сигнала. С помощью фазовращателей 7 и 11 устанавливается такая фаза сигналов на входах суммирующего усилителя ограничителя 5, чтобы сигнал на его выходе был максимальным (без режима ограничения). Порог у первого 15, второго 18 и третьего 21 пороговых устройств установлен таким образом, чтобы сигнал, близкий к минимальному уровню сигнала с выходов второго 14, третьего 17 и четвертого 20 фазовых детекторов соответствовал логическому нулю. При превышении этого уровня фиксируется логическая единица.

Сигнал с устройства формирования опорного напряжения 1 поступает одновременно на первый усилитель 3 и первый элемент задержки 6. С прямого выхода первого усилителя 3 сигнал через первый коммутатор 4 поступает на первый вход суммирующего усилителя-ограничителя. После первого элемента задержки 6 задержанный сигнал поступает одновременно на второй элемент задержки 10 и на первый фазовращатель 7. С выхода фазовращателя 7 сигнал поступает на второй усилитель 8, с прямого выхода которого через второй коммутатор 9 поступает на второй вход суммирующего усилителя-ограничителя 5. После второго элемента задержки 10 сигнал приобретает задержку (относительно устройства формирования опорного напряжения 1), равную суммарному времени задержки первого 6 и второго 10 элементов задержки, и поступает на второй фазовращатель 11, затем на прямой выход третьего усилителя 12, потом через третий коммутатор 13 на третий вход суммирующего усилителя-ограничителя 5.

На входах второго 14, третьего 17 и четвертого 20 фазовых детекторов присутствуют синфазные сигналы, поэтому на их выходах будет сигнал минимального уровня. На выходах первого 15, второго 18 и третьего 21 пороговых устройств будет сигнал нулевого уровня. Первый 16, второй 19 и третий 22 счетные триггеры остаются в нулевом состоянии. Первый 4, второй 9 и третий 13 коммутаторы остаются в исходном состоянии. На входах суммирующего усилителя-ограничителя 5 присутствуют синфазные сигналы. После сложения, усиления и ограничения в суммирующем усилителе-ограничителе 5 сигнал поступает на второй (опорный) вход первого фазового детектора 2.

После инверсии сигнала с выхода устройства формирования опорного напряжения 1 сигнал проходит через первый коммутатор 4 и поступает на вход суммирующего усилителя-ограничителя 5 с противоположной фазой. При этом за счет задержек в элементах задержки 6 и 10 фазы сигналов на выходах второго 9 и третьего 13 коммутаторов останутся неизменными. Амплитуды двух сигналов на суммирующем усилителе-ограничителе 5 сложатся и один вычтется. Так как коэффициент усиления суммирующего усилителя-ограничителя 5 подобран таким образом, чтобы сигнал с таким уровнем на входе был бы максимальным на выходе, но не приводил к ограничению, то на выходе суммирующего усилителя-ограничителя 5 останется сигнал такого же уровня, как и был, и с той же фазой, что и до момента инверсии.

При этом на входах четвертого фазового детектора 20 появятся противоположные по фазе сигналы и сигнал на его выходе изменит свой уровень на высокий. На выходе третьего порогового устройства 21 сигнал с нулевого уровня сменится на единичный, по переднему фронту третий счетный триггер 22 перейдет в единичное состояние. Первый коммутатор 4 переключится на инверсный выход первого усилителя 3, фаза сигнала на выходе первого коммутатора 4 изменится на первоначальную. На входах суммирующего усилителя-ограничителя 5 опять будут присутствовать синфазные сигналы, он перейдет в режим ограничения, но фаза сигнала на опорном входе фазового детектора 2 не изменится. При этом на входах четвертого фазового детектора опять будут синфазные сигналы и сигнал на его выходе сменится на низкий. Импульс на входе третьего счетного триггера 22 закончится, оставив его в единичном состоянии.

Затем сигнал с инверсной фазой появится на выходе первого 6 элемента задержки, фаза сигнала на прямом выходе второго усилителя 8 и на выходе второго коммутатора 9 сменится на инверсную относительно начальной. На входах суммирующего усилителя-ограничителя 5 будут присутствовать два сигнала с основной фазой и один с инверсной. При этом опять амплитуды двух сигналов в суммирующем усилителе-ограничителе 5 сложатся и один вычтется, усилитель выйдет из режима ограничения с тем же уровнем выходного сигнала, но фаза выходного сигнала останется неизменной.

В это время на входах третьего фазового детектора 17 появятся противофазные сигналы и сигнал на его выходе изменит свой уровень на высокий. На выходе второго порогового устройства 18 сигнал с нулевого уровня сменится на единичный, по переднему фронту счетный триггер 19 перейдет в единичное состояние и второй коммутатор 9 переключится с прямого на инверсный выход второго усилителя 8. При этом на входах суммирующего усилителя-ограничителя 5 будут присутствовать три синфазных сигнала и он перейдет в режим ограничения. При этом фаза на его выходе и на опорном входе фазового детектора 2 останется неизменной.

Аналогичным образом, когда сигнал с инверсной фазой появится на выходе второго элемента задержки 10, фаза сигнала на прямом выходе третьего усилителя 12 и третьего коммутатора 13 сменится на инверсную, на входах суммирующего усилителя-ограничителя 5 будут присутствовать два сигнала с основной фазой и один с инверсной и он выйдет из режима ограничения. При этом на выходе суммирующего усилителя-ограничителя 5 сигнал останется с прежней фазой.

В это время на входах второго фазового детектора 14 появятся противофазные сигналы и сигнал на его выходе изменит свой уровень на высокий. На выходе первого порогового устройства 15 сигнал с нулевого уровня сменится на единичный, первый счетный триггер 16 перейдет в единичное состояние. Третий коммутатор 13 переключится на инверсный выход третьего усилителя 12. В результате, на входах суммирующего усилителя-ограничителя 5 опять будут присутствовать синфазные сигналы и он перейдет в режим ограничения, но фаза сигнала с его выхода не изменится.

На входах второго фазового детектора 14 появятся синфазные сигналы, а на выходе низкий уровень. На входе первого счетного триггера 16 закончится импульс, оставив его в единичном состоянии.

По окончании указанных событий первый 4, второй 9, третий 13 коммутаторы передают на выход сигналы с инверсных выходов первого 3, второго 8 и третьего 12 усилителей, первый 16, второй 19 и третий 22 счетные триггеры находятся в единичном состоянии, а состояние остальных устройств не отличается от исходного.

Если фаза сигнала вновь поменяется на противоположную, суммирующий усилитель-ограничитель 5 выйдет из режима ограничения, сохранив фазу сигнала на выходе неизменной, а на выходе четвертого фазового детектора 20 появится высокий уровень. На выходе третьего порогового устройства 21 ноль сменится единицей, третий счетный триггер 22 установится с единичного на нулевой уровень, а первый коммутатор 4 переключится на передачу сигнала с прямого выхода первого усилителя 3. Суммирующий усилитель-ограничитель 5 войдет в режим ограничения, сохранив фазу сигнала на выходе неизменной. Это приведет к возврату уровней сигнала с выходов четвертого фазового детектора 20 и третьего порогового устройства 21 в исходное состояние.

Затем процесс повторится в цепочке: третий фазовый детектор 17, второе пороговое устройство 18, второй счетный триггер 19. Второй коммутатор 9 переключится с инверсного выхода на прямой. Третий фазовый детектор 17 и второе пороговое устройство 18 вернутся в исходное состояние, а состояние второго счетного триггера 19 останется неизменным.

Аналогичный процесс пройдет по цепочке: второй фазовый детектор 14, первое пороговое устройство 15, первый счетный триггер 16. Третий коммутатор 13 переключится с инверсного выхода на прямой. Второй фазовый детектор 14 и первое пороговое устройство вернутся в исходное состояние, а состояние первого счетного триггера 16 не изменится.

Во всех случаях на выходе суммирующего усилителя-ограничителя 5 амплитуда и фаза выходного сигнала останутся неизменными.

Таким образом, в схеме, реализующей синхронный прием фазоманипулированного сигнала, при инверсии фазы с выхода устройства формирования опорного напряжения 1 фаза на опорном входе первого фазового детектора 2 остается неизменной. Следовательно, у заявленного устройства помехоустойчивость выше, чем у аналогов.

В заявленном устройстве суммирующий усилитель-ограничитель может быть реализован на быстродействующем операционном усилителе. Если считать уровни сигналов на его входах одинаковыми, то коэффициент его усиления подбирается таким образом, что при уровне входного сигнала таком, как на одном из входов, он выдает сигнал максимального уровня без ограничения. При превышении этого уровня он должен входить в режим ограничения. К элементам задержки предъявляется следующее требование

где tЭ3 - время задержки каждого из элементов задержки;

tФД - время задержки второго 14, третьего 17 и четвертого 20 фазовых детекторов;

tПУ - время задержки каждого из пороговых устройств;

tСЧТ - время задержки каждого из счетных триггеров;

tК - время задержки каждого из коммутаторов, что в сумме составит не более пятидесяти микросекунд.

Этому требованию с избытком удовлетворяет устройство задержки на кварцевом (или ПАВ) резонаторе. Время задержки такого устройства составит 2Q/F0~0,04 секунды (для кварцевого резонатора) и ~0,005 С (для ПАВ резонатора), где Q=105 - добротность кварцевого, и Q=104 - ПАВ резонаторов, F0=50 МГц - частота опорного сигнала.

Остальные элементы устройства могут быть выполнены на стандартной элементной базе и не имеют каких-либо особенностей.

Демодулятор фазоманипулированных сигналов, содержащий объединенные по входу фазовый детектор, первый вход и выход которого являются входом и выходом устройства соответственно, и устройство формирования опорного напряжения, отличающийся тем, что в него введены последовательно соединенные первый усилитель, вход которого подключен к выходу устройства формирования опорного напряжения, первый коммутатор, суммирующий усилитель-ограничитель, выход которого подключен к второму входу фазового детектора, причем инверсный выход первого усилителя подключен к второму входу первого коммутатора, последовательно соединенные первый элемент задержки, вход которого подключен к выходу устройства формирования опорного напряжения, первый фазовращатель, второй усилитель и второй коммутатор, выход которого подключен к второму входу суммирующего усилителя-ограничителя, а инверсный выход второго усилителя подключен к второму входу второго коммутатора, последовательно соединенные второй элемент задержки, вход которого подключен к выходу первого элемента задержки, второй фазовращатель, третий усилитель, третий коммутатор, выход которого подключен к третьему входу суммирующего усилителя-ограничителя, а инверсный выход третьего усилителя подключен к второму входу третьего коммутатора, последовательно соединенные второй фазовый детектор, первый вход которого подключен к выходу суммирующего усилителя-ограничителя, а второй вход к выходу третьего коммутатора, первое пороговое устройство, первый счетный триггер, выход которого подключен к управляющему входу третьего коммутатора, последовательно соединенные третий фазовый детектор, первый вход которого подключен к выходу суммирующего усилителя-ограничителя, а второй вход к выходу второго коммутатора, второе пороговое устройство, второй счетный триггер, выход которого подключен к управляющему входу второго коммутатора, последовательно соединенные четвертый фазовый детектор, первый вход которого подключен к выходу суммирующего усилителя-ограничителя, а второй вход к выходу первого коммутатора, третье пороговое устройство, третий счетный триггер, выход которого подключен к управляющему входу первого коммутатора.