Цифровой процессор кущенко в.а.

Иллюстрации

Показать всеИзобретение относится к области цифровых вычислительных машин. Техническим результатом является повышение скорости вычислений и удобств при работе. Заявленный процессор содержит команды-операторы, позволяющие пользователю непосредственно составлять программы, работая со всеми необходимыми устройствами. Формат команды, независимый от шин адреса и данных, позволяет гибко вводить новые блоки и соответственно новые команды без изменения структуры уже наработанного аппаратного и программного обеспечения. Формат данных позволяет обеспечивать заданную точность. Процессор аппаратно реализует алгоритмы десятичного сложения, вычитания, умножения, деления, позволяя результат произведенной операции сохранять, а затем воспроизводить без нового вычисления. Введение аппаратно реализуемой индексации регистров позволяет в процессоре организовать данные в виде констант, переменных и массивов. Введение аппаратно реализуемого механизма управления функциями позволяет вводить их в любом заданном количестве. Введение аппаратно реализуемого механизма распознавания меток позволяет создавать ссылки и подпрограммы. Введение аппаратно реализуемого механизма прерываний позволяет осуществлять обработку задач в связи с заданными приоритетами. Введение аппаратно реализуемого календаря позволяет существовать системе в реальном масштабе времени. Наличие аппаратных средств изменения содержимого блока памяти команд позволяет осуществлять изменения в самом блоке памяти команд при самопрограммировании. 51 ил.

Реферат

Изобретение относится к области цифровых вычислительных машин (ЭЦВМ-компьютеров).

Известны вычислительные машины Б.Паскаля, Г.Лейбница, О.Однера, Ч. Бэбиджа, П.Чебышева, А.Крылова (Электронные вычислительные машины, Михайлов А.В. и др. Статистика, М., 1971 г.).

Недостатками этих устройств являются ручной набор (коммутация) данных, малая скорость счета, низкая надежность, большие массогабаритные показатели.

Известна машина Дж.Неймана (К.Вейцман, Распределенные системы мини- и микро ЭВМ, М.: Финансы и статистика, 1983 г.). Реализуемые на этом принципе процессоры (например: Система IBM/360, М, Статистика, 1974 г.) (прототип) основаны на: последовательном процессе обработки данных, на двоичной системе счисления, на правилах двоичной алгебры, на методе реализации умножения через сложение, деления через вычитание. На принципе возрастания сложности программного обеспечения: код, мнемокод, ассемблер, компилятор, транслятор, операционная система, оболочка, приложения. На принципе полной замены предыдущего оборудования новым, без врастания старого в новое.

Программное обеспечение большого объема требует повышенной тактовой частоты процессора, что приводит к технологическому пределу, без достижения необходимых результатов в областях, например распознавании изображений и моделировании мышления.

Неразвитость отечественного процессоростроения ведет к потере безопасности во всех сферах. Концентрация знаний в иностранных центрах и постоянно меняемая архитектура средств вычислительной техники не позволяет отечественным фирмам использовать наработанные результаты.

Есть только один путь - поддерживать свои структуры, постоянно их развивать и адаптировать к известным и создаваемым вновь средствам программного обеспечения. Монополизация же разработок программного обеспечения в небольшом количестве коллективов делают (при потере доступа к дистрибьютивным файлам) уязвимой и цивилизацию в целом.

Технический результат изобретения заключается в повышении скорости вычислений и удобств при работе в многопроцессорных комплексах.

Технический результат достигается тем, что в цифровой процессор, содержащий генератор, сумматор, шину адреса, шину данных, шину команд, разъемы, счетчик команд, блок управления, блок памяти, блок питания, блок клавиатуры, блок индикации, согласно изобретению введены: блок памяти команд, блок памяти данных, блоки набора команд, арифметический блок, логический блок, блок пересылок, блок регистров, блок безусловного перехода, блоки распознавания меток, блок функций, блок «сбоев», блок «есть», блок внешних регистров, блок пересылки команд, блок прямого доступа, причем арифметический блок, логический блок, блок пересылки, блок регистров, блок безусловного перехода, блок распознавания меток, блок функций, блок внешних регистров, блок «есть», блок «сбоев» подключены к шине команд, шине данных, шине адреса своими соответствующими входами-выходами, причем блок управления состоит из блока клавиатуры, подключенного к блоку индикации клавиатуры, подключенного к блоку индикации, блоку индикации команд, блоку индикации адреса, блоку индикации данных, причем блок индикации клавиатуры, блок индикации счетчика команд, блок индикации команд, блок индикации адреса, блок индикации данных подключены к соответствующим индикаторам и соответствующим индикаторам порядка, блок индикации команд подключен к шине команд, блок индикации адреса подключен к шине адреса, блока памяти данных, блок индикации данных подключен к шине данных, блок управления также содержит блок ввода команд, блок сброса, блок режима программирования, блок режима работы, блок шага команд вверх, блок шага команд вниз, блок очистки команд одной позиции, блок очистки команд ста позиций, блок очистки данных одной позиции, блок очистки данных ста позиций, блок шага команды вниз, блок шага команды вверх, блок шага данных вверх, блок шага данных вниз, блок шага регистра адреса, блок шага адреса, блок стоп, блок пуск с адреса, блок пуск с начала, блок пуск продолжения, блок пуск по шагам, соединенные соответствующим образом, причем блок набора команд состоит из блоков, распознающих каждый свою команду, каждый из этих блоков подключается к шине управления, причем арифметический блок состоит из блока вычислений первого (сумматор), блока вычислений второго (вычитатель), блока вычислений третьего (умножитель), блока вычислений четвертого (делитель), блока изменения знака на плюс, блока изменения знака на минус, причем формат числа представляет собой следующие позиции: знак основы числа, пространство переполнения, пространство цифр основы, знак раздела, знак порядка цифр, второе пространство переполнения, пространство порядка, причем блок вычислений первый состоит из схемы распознавания команды, схемы распознавания первой, схемы распознавания второй, схемы распознавания третьей, блока выравнивания порядка, общего табличного сумматора чисел, сумматора простых чисел, общего табличного вычислителя, вычитателя чисел и из элементов, обеспечивающих взаимодействие перечисленных блоков, причем схема распознавания команд, схема распознавания первая, вторая и третья подключаются к шине адреса, шине данных, шине команд, к соответствующему входу счетчика команд (через промежуточные элементы), к входам считывания и записи блока памяти данных (через промежуточные элементы), схема распознавания первая и вторая подключаются к блоку выравнивания порядка (через промежуточные элементы), который подключается к дешифратору определяющего порядка вычисления, к общему табличному сумматору чисел, к сумматору чисел и к коммутатору чисел, который подключается к общему табличному сумматору чисел, и к вычитателю чисел, который подключен к шине данных (через промежуточные элементы) и к схеме распознавания третьей, причем блок выравнивания порядка состоит из блока первого случая, блока второго случая первого варианта, блока второго случая второго варианта, блока анализа первого, блока третьего случая первого варианта, блока третьего случая второго варианта, блока анализа второго, блока четвертого случая первого варианта, блока четвертого случая второго варианта, блока анализа третьего, подключенных соответствующим образом для обеспечения выравнивания порядка чисел, причем табличный сумматор числа представляет собой регистр первого числа, подключаемый к верхним дешифраторам, регистр второго числа, подключаемый к боковым дешифраторам, на пересечении выходов верхних и боковых дешифраторов находится разрешающий ключ, выход которого подключается к соответствующему регистру результата, содержащему результат суммирования, входы которых подключены к регистру результата, содержащий основу числа и признак переполнения, причем сумматор простого числа состоит из сумматоров одной цифры, первый из которых подключается к соответствующим входам итогового блока регистров, а остальные подключены к соответствующим счетчикам, которые подключены (через промежуточные элементы) к элементам задержки, подключены к счетчикам, подключенным к соответствующим дешифраторам, подключаемым к соответствующим счетчикам (через промежуточные элементы), причем общий табличный вычитатель аналогичен по структуре общему табличному сумматору чисел, имеющих аналогичную структуру, что и табличный вычислитель чисел, но в регистре результата находится разность двух цифр, причем вычитатель числа имеет аналогичную структуру, что и сумматор простых чисел, но содержит вычитатели одной цифры вместо сумматоров одной цифры, а выходы вычитаний одной цифры через соответствующий ключ подключены к (-1)-входам соответствующих счетчиков и входам итогового блока регистров, причем блок вычитателя второй содержит блок распознавания команд, подключенный к шине адреса, шине данных, шине команд и соответствующему входу счетчика команд (через промежуточные элементы), к блоку «есть», к блоку «сбой» (аналогично блоку вычитания первому), соответствующим выходам блока распознавания команд, подключенного к соответствующим входам блока выравнивания порядка (через промежуточные элементы), выходы которого подключены к общему табличному сумматору чисел, к сумматору простых чисел, к коммутатору чисел, подключенному соответствующими входами к общему табличному вычитателю чисел, блок выравнивания порядков также подключен к дешифратору, определяющему порядок вычисления работающего согласно таблице выбора, подключенного к коммутатору чисел и к другим необходимым элементам, для выполнения своих функций, выходы сумматора простых чисел, подключаемые к входам общего табличного сумматора чисел, который подключается к общей шине (шина данных, шина адреса, шина команд, шина функций), вычитатель чисел подключен к общему табличному вычислителю, который подключается к общей шине, общему табличному сумматору чисел, сумматору простых чисел, общему табличному вычитателю чисел, вычитателю чисел, причем блок вычисления третий состоит из блока распознавания команд, подключенного к общей шине, также подключенного к блоку суммирования (через промежуточные элементы), к табличному сумматору чисел и дешифратору знака результата, к блоку умножения простых чисел последовательно (или блоку умножения простых чисел параллельно), который подключен к табличному умножителю чисел, который подключается к общей шине, соответствующие выходы табличного сумматора чисел, блок умножения простых чисел последовательно (или блок умножения простых чисел параллельно) подключены посредством промежуточных элементов к соответствующим входам-выходам блока распознавания команд, причем табличный умножитель числа имеет структуру, аналогичную умножителю одной цифры, табличному сумматору чисел двух цифр, он имеет регистр первого числа, подключенный к верхним дешифраторам, регистр второго числа подключается к боковым дешифраторам, на пересечении выходов дешифраторов находится ключ, выход которого подключен к разрешающему входу блока памяти регистра результата, который содержит результат умножения двух чисел, блок умножения простых чисел последовательно состоит из блока регистров первого числа, блока сдвиговых регистров второго числа, подключенных к соответствующим входам умножителей одной цифры, причем первая группа выходов первого умножителя одной цифры подключается к соответствующим входам блока регистров, а выход следующих подключен к соответствующим входам соответствующих табличных сумматоров чисел двух цифр, которые последовательно соединяются друг с другом (через промежуточные элементы) и подключены к соответствующим входам блока регистров, подключенного к шифратору, который подключен к сумматору простых чисел, подключенных к блоку регистров (через промежуточные элементы), причем блок умножения простых чисел параллельно состоит из блока регистров первого числа, подключенного к соответствующим блокам умножения на одно число со сдвигом, подключенным к соответствующему постоянному запоминающему устройству и к соответствующим выходам блока регистров второго числа, выходами подключенными к обратной пирамиде сумматоров простых чисел (через промежуточные элементы), последний из которых подключен к регистру, причем блок вычитания четвертый состоит из блока распознавания команд, подключаемого к входам-выходам общей шины, подключенного также (через промежуточные элементы) к блоку вычитания чисел, к табличному делителю чисел, к дешифратору определения знака результата, к блоку добавления нулей, подключаемого к блоку деления простых чисел, подключаемого к сумматору, подключен к табличному делителю чисел и к соответствующим регистрам, подключен к соответствующим входам блока распознавания команд и к блоку вычитателя числа, причем входы табличного делителя чисел подключаются к входам-выходам данных блока распознавания команд и к общей шине, причем блок добавления нулей состоит из блоков сдвиговых регистров и логических схем, подключенных соответствующим образом, на выходе объединены в результирующем регистре разницы добавляемых нулей, на которых находятся коды новых значений чисел с добавляемыми нулями справа, причем блок деления простых чисел содержит первый блок ключей, подключенный к регистру, подключенный к блоку вычитания чисел, подключенный к второму блоку ключей, подключаемый к регистру, подключенный к счетчику результата, подключенного к блоку сдвига регистров, является выходами блока деления простых чисел, выход знака результата блока вычитателей из соответствующие им элементы подключенных счетчиков сдвигов, подключены к компаратору подключений к регистру числа добавления нулей, подключенного к сумматору числа добавленных нулей делителя и разности добавленных нулей делимого и делителя, причем табличный делитель числа состоит из блока регистров делителя, подключенного к входам верхних дешифраторов, блока регистров делителя, подключенного к входам боковых дешифраторов, на пересечениях боковых и верхних дешифраторов находятся ключи, которые выходами подключаются к блокам памяти, содержащим основной порядок со знаком, и результата деления, подключенных к выходам блоков регистров, ключи также подключены к выходам элементов ИЛИ, определяющих "ДА" и "НЕТ" выходы табличного делителя чисел, причем блок изменения знака на плюс или минус имеет одинаковую структуру и состоит из схемы распознавания команды, схемы распознавания первой, подключенных соответствующим образом к общей шине и регистру, подключенные к постоянному запоминающему устройству (посредством элементов), причем логический блок состоит из блоков условного перехода: больше, больше или равно, меньше, меньше или равно, равно, неравно, подключенных к общей шине и имеющих одинаковую структуру, содержащих схему распознавания команд, набор ключей и шлюзов и схему распознавания первую, подключенную к соответствующему регистру, причем блок безусловного перехода состоит из схемы распознавания команды, схемы распознавания, подключенного к регистру адреса перехода и набора ключей шлюзов, соединенных соответствующим образом, соответствующий регистр блока пересылки первого, подключенному к входам-выходам и шине данных (через шлюз), разрешающим входом подключенный к выходу схемы распознавания первой (через промежуточные элементы), причем блок пересылки второй содержит схему распознавания команд, подключенных к входам соответствующих ключей и шлюзов, подключенных к общей шине и к схеме распознавания первой, подключенной к соответствующему регистру, подключенному через блок ключей к шине данных (через соответствующий шлюз), подключенный и к схеме распознавания второй подключенной к соответствующему регистру, подключенному к шине адреса (через соответствующий шлюз), причем блок пересылки третий состоит из блока пересылки первого и подключенного к схеме ожидания, причем блок пересылки четвертый состоит из блока пересылки второго, подключенного к схеме ожидания, выходу через шлюз, причем блок пересылки пятый состоит из блока пересылки первого, без соответствующих перемычек, подключенного к соответствующей схеме описания, блок распознавания меток программы, блок распознавания меток начала программы, блок распознавания меток конца программы одинаковы и содержат схему распознавания команды, подключенной к схеме распознавания первой, подключенной к шине команд, и соответствующему входу счетчика команд, к соответствующему входу блоков "СБОЙ", "ЕСТЬ", соответствующие постоянные запоминающие устройства схемы распознавания команд имеют соответствующий код распознавания меток, метки начала и метки конца программы, причем пересылочный блок содержит пять блоков пересылки, выполняет каждый свою функцию пересылки данных: блок пересылки первый пересылает содержимое внутреннего регистра во внутренний регистр, блок пересылки второй - пересылает данные из программы во внутренний регистр, блок пересылки третий пересылает содержимое внутреннего регистра во внешний, блок пересылки четвертый - пересылает данные из программы во внешний регистр, блок пересылки пятый - пересылает содержимое внешнего регистра во внутренний, причем регистров блок содержит блок сдвига и блок записи в регистр бита, причем блок сдвига содержит схему распознавания команд, подключенную к соответствующим шлюзам и ключам (подключенным к общей шине), подключенной к схеме распознавания первой подключенной к соответствующему регистру и схеме распознавания второй, подключенный к второму соответствующему регистру подключенному посредством логических элементов к сдвиговому регистру, подключенного к шине данных (через соответствующий шлюз), причем блок записи в регистр бита содержит схему распознавания команд, подключаемый к соответствующим ключам и шлюзам (подключенных к общей шине), подключенной к схеме распознавания первой, подключенной к соответствующему регистру и к схеме распознавания второй, подключенных к соответствующему регистру и к соответствующей схеме распознавания четвертой, подключенной к соответствующему регистру, который подключается к соответствующему дешифратору, который подключается к соответствующим входам блоков ключей, подключенным к соответствующему дешифратору, а выходами к соответствующему регистру, который через соответствующий блок ключей подключается к шине данных (через соответствующий шлюз), причем блок внешних регистров содержит разъемы для подключения внешних устройств к внешним регистрам записи и внешним регистрам считывания, каждый внешний регистр записи подключается к своей схеме ожидания, подключенный к тактирующему входу блока, и к соответствующему регистру, подключенного к логической схеме выбора регистра, внешний регистр записи также подключен к соответствующему триггеру, который подключен к соответствующему к входам элемента - ИЛИ, подключенного к соответствующей схеме определения адреса обрабатывающей программы, причем блок функций состоит из блока распознавания функций, подключенному к блоку переменных величин и блоку записи сигналов времени, подключенных к общей шине, к входам-выходам блока управления, имеющим разъем для наращивания новых функций, причем блок распознавания функций состоит из блоков ключей, триггеров и соответствующих ПЗУ, компараторов, подключенных соответствующим образом для распознавания команды определения функции, причем блок переменной величины состоит из схемы распознавания первой, подключенной к разрешающим входам соответствующих шлюзов и ключей, к соответствующему первому регистру и к схеме распознавания второй, подключенной к входящему регистру, подключенным к логическим схемам и третьему регистру, который подключен к шине данных (через соответствующий шлюз), выходы первого и второго регистров подключены к шине адреса (через соответствующий шлюз), причем блок записи считывания времени состоит из шести схем распознавания, подключенных каждая к своему регистру, подключенных через соответствующие ключи и шины к общей шине и к соответствующим регистрам блока временных сигналов, причем блок временных сигналов состоит из схемы набора времени, подключенной к блоку регистров, соответствующие выходы которого подключены к счетчику секунд, счетчику минут, счетчику часов, счетчику дней, счетчику месяцев, счетчику лет (посредством логических элементов), к которым также подключается генератор импульсов (посредством логической схемы), причем схема набора времени подключается к блоку управления и состоит из дешифратора команд, подключенного к регистру, подключенного к соответствующему блоку ключей, подключенные к регистру, подключенному к другому блоку ключей, другой вход которого подключен к триггеру, блок «сбой» представляет собой блок, аналогичный блоку внешних регистров без внешних регистров считывания, причем блок пересылки команд содержит блок распознавания команды пересылки команд, подключенный к общей шине и к первому блоку ключей, подключенный к первому, второму и третьему регистрам, который также подключен к второму блоку ключей, подключенного к триггеру, подключенного к дешифратору команд, подключаемого к блоку управления выходы первого регистра подключены к входам первого счетчика, выходы-входы регистра подключены к первым входам компаратора, выходы-входы которого подключены к выходам второго счетчика, подключены к выходам третьего регистра, выходы первого и второго счетчика через блок ключей подключены к соответствующим выходам блока пересылки команд, выход компаратора посредством элемента задержки подключен к соответствующим входам блока пересылки команд, причем блок распознавания команд состоит из схемы распознавания команд и четырех схем распознавания, подключаемых каждая к своему регистру, причем блок прямого доступа представляет собой регистр управления, регистр адреса и регистр данных, подключенных к блоку команды данных (посредством логических элементов).

С целью повышения быстродействия шины адреса, шины данных, шины команд и шины управления расширены до возможности параллельной загрузки команд программы с соответствующими изменениями необходимых блоков.

Предлагаемый процессор обладает простой, модульной архитектурой, состоящей из независимых функциональных блоков. Содержит небольшое, но достаточное количество команд-операторов, позволяющих пользователю непосредственно составлять программы, работая со всеми необходимыми устройствами. Формат команды, независимый от шин адреса и данных, позволяет гибко вводить новые блоки и соответственно новые команды без изменения структуры уже наработанного аппаратного и программного обеспечения. Формат данных позволяет обеспечивать заданную точность. Процессор аппаратно реализует специальные алгоритмы десятичного сложения, вычитания, умножения, деления, позволяя результат произведенной операции сохранять, а затем воспроизводить без нового вычисления. Это ведет к существенному повышению скорости вычислений.

Введение аппаратно реализуемой индексации регистров позволяет в процессоре организовать данные в виде констант, переменных и массивов. Введение аппаратно реализуемого механизма управления функциями позволяет вводить их в любом заданном количестве через внутреннюю шину. Введение аппаратно реализуемого механизма распознавания меток позволяет создавать ссылки и подпрограммы. Введение аппаратно реализуемого механизма прерываний позволяет осуществлять обработку задач в связи с заданными приоритетами. Введение аппаратно реализуемого календаря позволяет существовать системе в реальном масштабе времени.

Наличие аппаратных средств изменения содержимого блока памяти команд позволяет осуществлять изменения в самом блоке памяти команд при самопрограммировании. Наличие многих вариантов доступов к блоку памяти команд (через общую шину, через блок памяти данных, через шину встроенной клавиатуры, через блок внешних регистров) делает предлагаемый процессор удобным при работе в многопроцессорных комплексах.

Наличие табличных вычислителей многократно повышает скорость вычислений.

Предлагаемый процессор обладает прозрачной, легко микро и нано-реализуемой, открытой структурой, способной к многоядерному объединению, что обеспечивает лучшие параметры функционирования, чем известные процессоры.

Само по себе компактное описание ВК-Ц процессора имеет методологическое значение в процессе обучения.

Изобретение поясняется чертежами (фиг.1-51).

На фиг.1 изображена структура (формат) записи числа в ВК-Ц процессоре. Число А представлено:

- знаком числа, - основой, - знаком порядка и - порядком.

Здесь:

1. - 1 бит, который определяет знак числа 0 - это «-» ; 1 это «+»;.

2. 4 бита - пространство заполнено нулями. Если записанное число в процессе работы ВК-Ц процессора заполнит это пространство, то это число не входит в размер, отводимый для записи числа. (Запись может быть: сокращенной по 4 бита, расширенной - по 8 бит, или смешанной на знак цифры (фиг.1).)

3. Далее по 4 бита записывается основа числа . Таких цифр (в двоичном коде и в заданной системе счисления ), например, может быть 100.

4. 4 бита знак «/» - раздела основы числа от порядка .

5. 1 бит - знак порядка 0 - это «-»; 1 - это «+».

6. 4 бита - пространство заполнено нулями. Если в процессе работы это пространство будет заполнено, то значит, произошло переполнение.

7. По 4 бита, например, 3 десятичных числа для написания порядка результата (при трех числах 999 - максимальный порядок).

Количество цифр в основе и порядке - регулируемый параметр. Точка (если представлять число не целым, в алгебраическом смысле) поставлена справа.

На фиг.2 изображена схема ВК-Сумматора (электронная таблица суммирования).

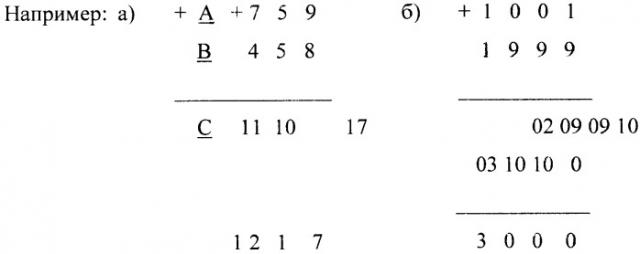

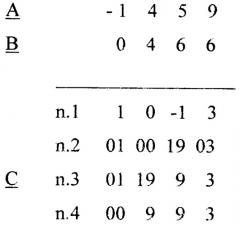

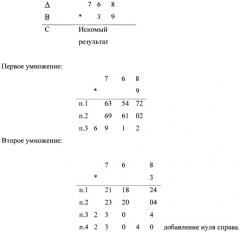

ВК-Сумматор состоит из разъема А (РА) - 1, разъема В (РВ) - 2, разъема С (РС) - 3. (PC) - 3 содержит выделенный разряд переноса (П) 1 - есть, 0 - нет. В (РА) - 1 записывается первое слагаемое, в РВ - 2 - второе, PC - 3 - полученный результат с признаком или отсутствием признака переноса разряда. РА - 1 подключен к верхней линейке дешифраторов ДШВ от 0 до 9: ДШВ 4 - ДШВ 13. Разъем РВ подключен к боковым дешифраторам ДШБ, также от 0 до 9. ДШБ 14 - ДШБ 23, выход каждого ДШВ подключен к первым соответствующим входам вертикального ряда ключей 24, выход каждого ДШБ подключен ко вторым входам соответствующего горизонтального ряда ключей 24 (фиг.2). Каждому ДШВ и каждому ДШБ соответствует своя цифра (показано на фиг.2 в десятичной и двоичной формах), на которую он реагирует. Каждый К - 24 подключен к соответствующему блоку памяти БП - 25. Этот блок памяти представляет собой ПЗУ и блок ключей соответствующих этому ПЗУ. В ПЗУ записан двоичный код соответствующей цифры. Блок ключей блока памяти 25 входами подключен к соответствующему ПЗУ, а выходами соответственно по разрядам объединен с такими же блоками (всего сто (10×10) таких блоков) и подключен к PC - 3, в котором разряд переноса (П) выделен. Описанные выше блоки образуют также сумматор одной цифры С1Ц - 26, который суммирует только положительные целые цифры (основы). На фиг.2 сверху блоков памяти 25 написаны цифры в десятичной системе, а внутри в двоичной с выделением знака переноса. Например: (выделены кружками) 9+8=17; 9 ((10) - десятичная система) = 1001 ((2) - двоичная система); 8 (10) = 1000 (2), результат 17 (10) = 1 0111 (2), то есть 1 знак переноса и 7 (10) = 0111 (2).

Сумматоры одной цифры (С1Ц) - 26 объединены в сумматор простых чисел (СПЧ) - 27 (фиг.3), который состоит из элемента задержки ЭЗ - 28, вход которого подключен к разрешающему входу блока регистров А (БРА) -29, блока регистров В (БРВ) - 30 и является разрешающим (р) - входом СПЧ - 27. Ключ (К) - 31 входом подключен к выходу элемента задержки (ЭЗ) - 32, вход которого тоже подключен к р-входу СПЧ - 27. Выход К - 31 подключен к (+1) - входу СЧ - 33.2, р-вход которого подключен к соответствующим р-входам СЧ - 33.3 - СЧ - 33.n и к выходу ЭЗ - 28. Элемент ИЛИ (1) - 34.2 подключен к (+1) входу каждого СЧ - 33.3 (и т.д.). Соответствующие выходы каждого СЧ - 33.2 - СЧ - 33.n подключены к соответствующим входам соответствующих им дешифраторов ДШ - 35.2 - ДШ - 35.n.

П-выходы каждого С1Ц2 - С1Цn подключены к первым входам ключей К - 36.2 - К - 36.n соответственно (К - 36.1 нет), выходы которых подключены к первым входам соответствующих им ИЛИ - 34.2 - ИЛИ - 34.n, вторые входы которых подключены к выходам соответствующих ключей К -37.2 - К - 37.n. Вторые входы К - 36.2 - К - 36.n подключены к выходам соответствующих им элементам задержки ЭЗ - 38.2 - ЭЗ - 38.n и входам элементов задержки ЭЗ - 39.2 - ЭЗ - З9.n (которые последовательно соединены) и выходы которых подключены к входам соответствующих К - 37.2 - К - 37.n. П - выход С1Ц1 подключен к первому входу К - 31. Выход ЭЗ - 39.n также подключен к входу элемента задержки (ЭЗ) - 40, который подключен к р-входу итогового блока регистров (ИБР) - 41, соответствующие входы которого подключены к выходам соответствующих СЧ - 33.2 - СЧ - 33.n и И-выходам С1Ц1 - 26. Выход ИБР - 41 является С - выходом с СПЧ - 27. Выход ЭЗ - 40 также подключен к входу ЭЗ - 42, выход которого является выходом «Готово» (Г) СПЧ - 27. Выход ИЛИ - 34.n является выходом прерывания («Сбой» - «ПР») СПЧ - 27, также подключенного к «0» - входу ЭЗ - 40.

ВК - вычитатель (электронная таблица вычитания) состоит из (фиг.4) разъема В (РВ) - 43, разъема А (РА) - 44, разъема С (PC) - 45. РВ - 43 подключен к верхним дешифраторам ДШВ 46 - ДШВ 55. PA - 44 подключен к дешифраторам боковым ДШБ - 56 - ДШБ - 65. Каждый из ДШБ подключен к первым входам горизонтальной линии ключей К - 66. Каждый из ДШВ подключен ко вторым входам вертикального столбца этих же ключей К - 66. Соответствующие выходы К - 66 подключены к разрешающим входам блоков памяти БП - 67, представляющих собой ПЗУ с блоком ключей на выходе (аналогично описанному блоку в блоке суммирования). В ПЗУ записан результат вычитания простых цифр от 0 до 9 между собой. Если вычитатель больше вычитаемого, то соответствующие ПЗУ записывают цифры обратного кода и в соответствующем заимствованию разряде находится «1». Например: 0(10)-9(10)=-9(10), в ПЗУ записано не - 9, а 10-9=1, т.е. 1 1 (10).

Если 4-7=-3, то 10-3=7, записано 1 7 (10) и т.д. Все БП - 67 объединены соответствующими выходами и подключены к входам PC - 45. Перечисленные блоки образуют также вычитатель одной цифры В1Ц - 68 (фиг.4). Значение переноса (П) выделено в PC - 45 в отдельный разряд.

В1Ц - 68 объединены в вычитатель числа ВЧ - 69 (фиг.5). Он состоит из элемента задержки ЭЗ - 70, вход которого является р-входом ВЧ - 69, блока регистров А (БРА) - 71, входы которого являются входами А ВЧ - 69. Входы блока регистров В (БРВ) - 72 являются входами вычитателя ВЧ - 69. БРА - 71 подключен соответствующими выходами к соответствующим входам каждого В1Ц1 - В1Цn - 68. БРВ подключен своими выходами к соответствующим входам каждого из блоков В1Ц1 - В1Цn - 68. П - выход В1Ц1 - 68 подключен к первому входу ключа К - 73. Разрешающий вход ВЧ - 69 также подключен к входу элемента задержки (ЭЗ) - 74, выход которого подключен к второму входу К - 73, выход которого подключен к (-1) - входу СЧ - 75.2, -1 вход каждого из СЧ 75.3 - СЧ 75.n подключены к соответствующим выходам элементов ИЛИ - 76.2 - 76.n соответственно (элемента ИЛИ - 76.1 нет). Соответствующие выходы каждого СЧ - 75.2 - СЧ - 75.n подключены к соответствующим входам ДШ - 77.2 - ДШ - 77.n, выход которого подключен к соответствующим ключам К 78.2 - 78.n. Соответствующие П - выходы В1Ц2 - В1Цn подключены к первым входам ключей К 79.2-79.n соответственно (К - 79.1 нет), выходы которых подключены к вторым входам соответствующих ИЛИ 76.2 - ИЛИ 76.n. Выход ЭЗ - 74 подключен к входу ЭЗ - 80.2, вход которого подключен к первому входу К - 79.2 и входу элемента задержки ЭЗ - 81.2, выход которого подключен к вторым входам К - 78.2 и т.д. до ЭЗ - 81.n, выход которого подключен к второму входу К - 78.n и ко входу элемента задержки ЭЗ - 82, «0» - вход которого подключен к выходу ИЛИ - 76.n и является Пр-выходом (сбой, прерывание) ВЧ - 69. Выход ЭЗ - 82 подключен к р-входу итогового блока регистров ИБР - 83 и входу элемента задержки ЭЗ - 84, выход которого является Г-выходом (готов) ВЧ - 69. В1Ц1 подключен к соответствующим входам ИБР - 83, соответствующие входы которого подключены к соответствующим выходам СЧ - 75.2 - СЧ - 75.n, а выходы являются выходами ВЧ - 69.

На фиг.6 изображена схема табличных блоков вычислений. Это общая схема для табличного сумматора чисел (ОТСЧ), табличного вычитателя чисел (ОТВЧ), табличного умножителя чисел (ОТУЧ), табличного делителя чисел (ОТДЧ). Табличный сумматор простых чисел ТСЧ показан на фиг.2, ТВЧ на фиг.4 (ТУЧ и ТДЧ показаны далее). Изменения в соответствующих блоках показаны пунктиром. Для ТСЧ выходы каждого ключа К - 24 подключены к ИЛИ - 85, «не» - выход которого подключен к ключу К - 86, а прямой выход подключен к входу ключа К - 87, вторые выходы К - 86 и К - 87 подключены к разрешающему р-входу блока ТСЧ - 88 (фиг.2). Для ТВЧ блока. Все выходы К - 66 подключены к входам элемента ИЛИ - 89, инвертный выход которого подключен к ключу К - 90, а прямой выход к ключу К - 91. В1Ц - 68 и перечисленные блоки образуют ТВЧ - 92. Соответствующие блоки ТВЧ, ТСЧ, ТУЧ, ТДЧ объединяются в большие блоки при росте количества хранимых в них чисел. Общие блоки ОТСЧ (и т.д.) (фиг.6) содержат разъем А (РА) - 93, разъем В (РВ) - 94, разъема (PC) - 95. PA - 93 подключен к А входам ТСЧ (и т.д.) - 88. РВ - 94 к В входам, PC - 95 и к С - выходам. Выходы «да» объединены ИЛИ - 96, выходы «нет» объединены ИЛИ - 97, разрешающий вход подключен к р-входам ТСЧ (и т.д.) - 88, запись (З) вход, информационный (И) входы, входы общей шины также подключены соответствующим блоком - 88. Перечисленные блоки образуют ОТСЧ (ОТВЧ) - 98 (99).

Блок выравнивания порядка (БВП) (нулями справа) (фиг.7) состоит из элемента задержки 100, регистра (триггера) (З) знака - 101, регистра (Р) - 102, регистра (З) знака - 103, регистра (Р) - 104, регистра (З) знака В - 105, регистра (Р) - 106, регистра (З) знака - 107, регистра (Р) - 108. Выход ЭЗ - 100 подключен к р-входу КМП - 109, и-входы которого подключены к выходу Р - 103 и выходу Р - 107, выход «да» подключен к р-входу КМП - 110, выход «нет» подключен к ИЛИ - 111. Входы и КМП - 110 подключены к Р - 103 и Р - 108, соответственно выход «да» подключен к входу формирующих сигналов (ФС) - 112, выход которого подключен к р-входам Р - 113, Р - 114, Р - 115, Р - 116. Выход «нет» КМП - 110 подключен к второму входу ИЛИ - 111, выход которого подключен к р-входу КМП - 117. Соответствующие выходы Р - 113, Р - 114, Р - 115, Р - 116 подключены к соответствующим разъемам Р - 119, Р - 120, Р - 121, Р - 122, выходы которых являются выходами блока выравнивания порядка (БВП). Выход ФС - 112 (Г1) также подключен к ИЛИ - 123, выход которого является выходом «готово» (Г) БВП. Блоки 109-116 образуют блок первого случая (Б1C - 116.1). Соответственно входы КМП - 117 подключены к выходам ПЗУ (+) - 124, которые также подключены к КМП - 125, р-вход которого подключен к выходу «да» КМП - 117, вторые входы которого подключены к выходу Р - 107, выход «нет» подключен к ИЛИ - 126, второй вход которого подключен к выходу «нет» КМП - 125, вторые входы которого подключены к выходам Р - 103, а выход «да» подключен к р-входу КМП > - 127, соответственно входы которого подключены к выходам Р - 104 и Р - 108, а выход подключен к входу ФС - 128, выход которого подключен к входам БК - 129, 130, 131, ЭЗ - 132, 133. Выход ЭЗ - 132 подключен к р-входу СЧ - 134, регистру (Р) - 135, блоку сдвиговых регистров (БСР) - 136. Выходы БК - 131 подключены к и-входам СЧ - 134, выходы которого подключены к соответствующим входам КМП - 137 и соответствующим входам регистра (Р) - 138. Выходы БК - 130 подключены к и-входам Р - 135, выходы которого подключены к вторым входам КМП - 137, выход < подключен к ФС - 139, выход которого является выходом «готово» Г (Г1) и подключен к р-входам регистров (Р) - 140, 141, 142. Выход ≥ КМП - 137 подключен к входу ИЛИ - 143 и к тактирующему (Т) входу БСР - 136, первые и-входы которого подключены к выходам БК - 129, вторые и-входы подключены к выходам ПЗУ (0) - 144, а выходы подключены к соответствующим входам Р - 140. Выход ИЛИ - 143 подключен к (-1) входу СЧ - 134 и входу ЭЗ - 145, выход которого подключен к р-входу КМП - 137. Пр - выход БСР - 136 является выходом «сбой» и подключен к ИЛИ - 146, выход которого подключен к ИЛИ -147. Далее ИЛИ 147.1 Выход Г1 (ФС) - 139 подключен к ИЛИ - 123, выход которого является Г выходом БВП. Вход (3) Р - 141 подключен к выходу Р - 105, соответственно вход Р - 141 подключен к выходам Р - 106,