Устройство для решения задач оптимизации

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано для решения задач определения количества резервируемых элементов, обеспечивающих заданный уровень надежности системы при заданных габаритах и ограничении затрат на ее изготовление. Техническим результатом изобретения является разработка устройства решения задач оптимизации, позволяющего определять количество резервируемых элементов, обеспечивающих заданный уровень надежности системы при заданных габаритах и ограничении затрат на ее изготовление. Устройство для решения задач оптимизации состоит из входной наборной панели 1, управляющего устройства 2, блоков 31, 32, …, 3N вычисления вероятности отказа, блоков 41, 42, ..., 4N вычисления стоимости, первой 51, 52, …, 5N-1, второй 81, 82, …, 8N-1 и третьей 121, 122, …, 12N-1 группы сумматоров, первой 61, 62, …, 6N-1 и второй 101, 102, …, 10N-1 группы компараторов, первой 71, 72, …, 7N-1 второй 111, 112, …, 11N-1 и третьей 141, 142, …, 14N-1 группы оперативных запоминающих устройств, первой 91, 92, …, 9N-1 и второй 131, 132, …, 13N-1 группы элементов «И», блоков 151, 152, …, 15N вычисления габаритов и блока отображения 16. 4 ил., 3 табл.

Реферат

Изобретение относится к вычислительной технике и может быть использовано для решения задач определения количества резервируемых элементов, обеспечивающих заданный уровень надежности системы при ограничении затрат на ее изготовление.

Известно устройство для решения задач оптимизации [1], содержащее входную наборную панель, управляющее устройство, блоки вычисления вероятности отказа, блоки вычисления стоимости, первую группу сумматоров, компараторы, первую группу оперативных запоминающих устройств, вторую группу сумматоров, элементы «И», вторую группу оперативных запоминающих устройств, блок отображения, при этом первые входы всех-блоков вычисления вероятности отказов и блоков вычисления стоимости подключены соответственно к первым и вторым выходам входной наборной панели, вход которой соединен с первым выходом устройства управления, второй выход которого подключен ко второму входу блоков вычисления вероятности отказов, а пятый выход соединен с вторым входом блоков вычисления стоимости, выходы первого и второго из которых соединены соответственно с первым и вторым входом первого сумматора второй группы сумматоров, выход которого подключен к первому входу первого элемента «И», выход которого соединен с первым входом первого оперативно-запоминающего устройства второй группы оперативно-запоминающих устройств, выход которого соединен с первым входом j-го (j=2, …, N-2, где N - количество блоков вычисления вероятности отказа, количество блоков вычисления стоимости) сумматора второй группы сумматоров, второй вход которого подключен к выходу m-го (m=3, …, N-1) блока вычисления стоимости, а выход через первый вход j-го (j=2, …, N-2) элемента «И» - к первому входу j-го (j=2, …, N-2) оперативно-запоминающего устройства второй группы оперативно-запоминающих устройств, выход которого соединен с первым входом j+1-го сумматора второй группы сумматоров, второй вход которого подключен к выходу m+1-го блока вычисления стоимости, а выход через j+1-й элемент «И» к первому входу j+1-го оперативно-запоминающего устройства второй группы оперативно-запоминающих устройств, выход которого соединен с выходами всех оперативно-запоминающих устройств второй группы оперативно-запоминающих устройств и с вторым входом блока отображения, первый вход которого соединен с выходами всех оперативно-запоминающих устройств первой группы оперативно-запоминающих устройств, второй вход j+1-го (j=2, …, N-2) оперативно-запоминающего устройства первой группы оперативно-запоминающих устройств соединен с вторыми входами всех оперативно-запоминающих устройств и с четвертым выходом устройства управления, а первый вход с вторым входом j+1-го элемента «И» и с выходом j+1-го (j=2, …, N-2) компаратора, второй вход которого соединен со вторым входом всех компараторов и с третьим выходом устройства управления, а первый вход подключен к выходу j+1-го (j=2, …, N-2) сумматора первой группы сумматоров, второй вход которого соединен с выходом m+1-го (m=3, …, N-1) блока вычисления вероятности отказов, а первый вход с выходом j-го (j=2, …, N-2) оперативно-запоминающего устройства первой группы оперативно-запоминающих устройств, первый вход которого соединен с вторым входом j-го элемента «И» и с выходом j-го компаратора, первый вход которого подключен к выходу j-го (j=2, …, N-2) сумматора первой группы сумматоров, второй вход которого соединен с выходом m-го (m=3, …, N-1) блока вычисления вероятности отказов, а первый - с выходом первого оперативно-запоминающего устройства первой группы оперативно-запоминающих устройств, первый вход которого соединен вторым входом первого элемента «И» и с выходом первого компаратора, первый вход которого подключен к выходу первого сумматора первой группы сумматоров, первый и второй входы которого соединены соответственно с выходами первого и второго блоков вычисления вероятности отказов [1].

Данное устройство-прототип позволяет определять количество резервируемых элементов, обеспечивающих заданный уровень надежности системы при ограничении затрат на ее изготовление. Однако данное устройство обладает узкими функциональными возможностями.

Технической задачей, решаемой данным изобретением, является разработка устройства для решения задач оптимизации, позволяющего определять количество резервируемых элементов, обеспечивающих заданный уровень надежности системы при ограничении затрат на ее изготовление и минимальные габариты.

Поставленная цель достигается тем, что в устройство для решения задач оптимизации, содержащее входную наборную панель, управляющее устройство, блоки вычисления вероятности отказа, блоки вычисления стоимости, первую группу сумматоров, компараторы, первую группу оперативных запоминающих устройств, вторую группу сумматоров, элементы «И», вторую группу оперативных запоминающих устройств, блок отображения, отличающееся тем, что дополнительно введены третья группа сумматоров, вторая группа элементов «И», вторая группа компараторов, третья группа оперативно запоминающих устройств, группа блоков вычисления габаритов, при этом первые входы всех блоков вычисления вероятности отказов, блоков вычисления стоимости и блоков вычисления габаритов подключены соответственно к первому, второму и третьему выходам входной наборной панели, вход которой соединен с первым входом устройства управления, второй выход которого подключен ко вторым входам блоков вычисления вероятности отказов, третий выход подключен ко вторым входам компараторов первой группы, четвертый выход подключен параллельно ко вторым входам оперативно-запоминающих устройств первой, второй и третьей групп, пятый выход соединен со вторыми входами компараторов второй группы, шестой выход соединен со вторыми входами блоков вычисления стоимости, а седьмой выход устройства управления соединен со вторыми входами блоков вычисления габаритов, выходы первого и второго из которых соединены соответственно с первым и вторым входами первого сумматора третьей группы, выход которого подключен к первому входу первого элемента «И» второй группы элементов «И», выход которого соединен с первым входом первого оперативно-запоминающего устройства третьей группы оперативно-запоминающих устройств, выход которого соединен с первым входом j-го (j=2, …, N-2, где N - количество блоков вычисления вероятности отказа, количество блоков вычисления стоимости, количество блоков вычисления габаритов) сумматора третьей группы сумматоров, второй вход которого подключен к выходу m-го (m=3, …, N-1) блока вычисления габаритов, а выход через первый вход j-го (j=2, …, N-2) элемента «И» второй группы элементов «И» - к первому входу j-го (j=2, …, N-2) оперативно-запоминающего устройства третьей группы оперативно-запоминающих устройств, выход которого соединен с первым входом N-1-го сумматора третьей группы сумматоров, второй вход которого подключен к выходу N-го блока вычисления габаритов, а выход через N-1-й элемент «И» второй группы элементов «И» к первому входу N-1-го оперативно-запоминающего устройства третьей группы оперативно-запоминающих устройств, выход которого соединен с выходами всех оперативно-запоминающих устройств третьей группы оперативно-запоминающих устройств и с третьим входом блока отображения, выходы первого и второго блоков вычисления стоимости соединены соответственно с первым и вторым входом первого сумматора второй группы сумматоров, выход которого подключен к первому входу первого элемента «И» первой группы элементов «И», выход которого соединен с первым входом первого компаратора второй группы, выход которого соединен со вторым входом первого элемента «И» второй группы элементов «И» и с первым входом первого оперативно-запоминающего устройства второй группы оперативно-запоминающих устройств, выход которого соединен с первым входом j-го сумматора второй группы сумматоров, второй вход которого подключен к выходу m-го (m=3, …, N-1) блока вычисления стоимости, а выход через первый вход j-го (j=2, …, N-2) элемента «И» второй группы элементов «И» - к первому входу j-го компаратора второй группы компараторов, выход которого подключен ко второму входу j-го элемента «И» второй группы элементов «И» и к первому входу j-го (j=2, …, N-2) оперативно-запоминающего устройства второй группы оперативно-запоминающих устройств, выход которого соединен с первым входом N-1-го сумматора второй группы сумматоров, второй вход которого подключен к выходу N-го блока вычисления стоимости, а выход через N-1-й элемент «И» первой группы элементов «И» к первому входу N-1-го компаратора второй группы компараторов, выход которого подключен ко второму входу N-1-го элемента «И» второй группы элементов «И» и к первому входу N-1-го оперативно-запоминающего устройства второй группы оперативно-запоминающих устройств, выход которого соединен с выходами всех оперативно-запоминающих устройств второй группы оперативно-запоминающих устройств и с вторым входом блока отображения, первый вход которого соединен с выходами всех оперативно-запоминающих устройств первой группы оперативно-запоминающих устройств, первый вход N-1-го оперативно-запоминающего устройства первой группы соединен со вторым входом N-1-го элемента «И» первой группы элементов «И» и с выходом N-1-го компаратора первой группы компараторов, первый вход которого подключен к выходу N-1-го сумматора первой группы сумматоров, второй вход которого соединен с выходом N-го блока вычисления вероятности отказов, а первый вход с выходом j-го (j=2, …, N-2) оперативно-запоминающего устройства первой группы оперативно-запоминающих устройств, первый вход которого соединен со вторым входом j-го элемента «И» первой группы элементов «И» и с выходом j-го компаратора первой группы компараторов, первый вход которого подключен к выходу j-го (j=2, …, N-2) сумматора первой группы сумматоров, первый вход которого соединен с выходом первого оперативно-запоминающего устройства первой группы оперативно-запоминающих устройств, первый вход которого соединен со вторым входом первого элемента «И» первой группы элементов «И» и с выходом первого компаратора первой группы компараторов, первый вход которого подключен к выходу первого сумматора первой группы сумматоров, первый и второй входы которого соединены соответственно с выходами первого и второго блоков вычисления вероятности отказов.

Проведенный заявителем анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностями признаков, тождественным всем признакам заявленного устройства для решения задач оптимизации, отсутствуют, поэтому изобретение соответствует условию патентоспособности "Новизна".

Результаты поиска известных решений в данной и смежной областях техники с целью выявления признаков, совпадающих с отличительными от прототипов признаками заявляемого изобретения, показали, что они не следуют явным образом из уровня техники. Из определенного заявителем уровня техники не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "Изобретательский уровень".

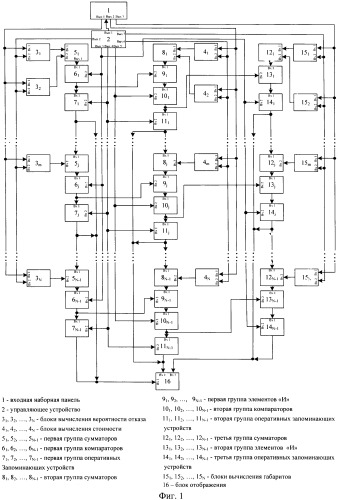

Заявленный объект изобретения поясняется чертежами, на которых показаны: на фиг.1 - структурная схема устройства для решения задач оптимизации, на фиг.2 - структурная схема блока вычисления вероятности отказа, на фиг.3 - структурная схема блока вычисления стоимости, на фиг.4 - структурная схема блока вычисления габаритов.

Устройство для решения задач оптимизации предназначено для определения количества резервируемых элементов, обеспечивающих заданный уровень надежности системы при ограничении затрат на ее изготовление и минимальные габариты. Его структурная схема может быть представлена в нескольких вариантах. В частности, устройство для решения задач оптимизации состоит из входной наборной панели 1, управляющего устройства 2, блоков 31, 32, …, 3N вычисления вероятности отказа, блоков 41, 42, …, 4N вычисления стоимости, первой 51, 52, …, 5N-1, второй 81, 82, …, 8N-1 и третьей 121, 122, …, 12N-1 группы сумматоров, первой 61, 62, …, 6N-1 и второй 101, 102, …, 10N-1 группы компараторов, первой 71, 72, …, 7N-1, второй 111, 112, …, 11N-1 и третьей 141, 142, …, 14N-1 группы оперативных запоминающих устройств, первой 91, 92, …, 9N-1 и второй 131, 132, …, 13N-1 группы элементов «И», блоков 151, 152, …, 15N вычисления габаритов, блока отображения 16.

Первые входы всех блоков 31, 32, …, 3N вычисления вероятности отказов, блоков 41, 42, …, 4N вычисления стоимости и блоков 151, 152, …, 15N вычисления габаритов подключены соответственно к первому, второму и третьему выходам входной наборной панели 1, вход которой соединен с первым выходом устройства управления 2, второй выход которого подключен ко вторым входам блоков 31, 32, …, 3N вычисления вероятности отказов, третий выход подключен ко вторым входам компараторов 61, 62, …, 6N-1, четвертый выход подключен параллельно ко вторым входам оперативно-запоминающих устройств 71, 72, …, 7N-1, 111, 112, …, 11N-1, и 141, 142, …, 14N-1, пятый выход соединен со вторыми входами компараторов 101, 102, …, 10N-1, шестой выход соединен со вторыми входами блоков 41, 42, …, 4N вычисления стоимости, а седьмой выход устройства управления 2 соединен со вторыми входами блоков 151, 152, …, 15N вычисления габаритов, выходы первого и второго из которых соединены соответственно с первым и вторым входами сумматора 121, выход которого подключен к первому входу элемента «И» 131, выход которого соединен с первым входом оперативно-запоминающего устройства 141, выход которого соединен с первым входом сумматора 12j, второй вход которого подключен к выходу блока вычисления габаритов 15m, а выход через первый вход элемента «И» 13j подключен к первому входу оперативно-запоминающего устройства 14j, выход которого соединен с первым входом сумматора 12N-1, второй вход которого подключен к выходу блока вычисления габаритов 15N, а выход через элемент «И» 13N-1 подключен к первому входу оперативно-запоминающего устройства 14N-1, выход которого соединен с выходами оперативно-запоминающих устройств 141, 142, …, 14N-2 и с третьим входом блока отображения 16, выходы блоков вычисления стоимости 41, 42 соединены соответственно с первым и вторым входом сумматора 81, выход которого подключен к первому входу элемента «И» 91, выход которого соединен с первым входом компаратора 101, выход которого соединен со вторым входом элемента «И» 131 и с первым входом оперативно-запоминающего устройства 111, выход которого соединен с первым входом сумматора 8j, второй вход которого подключен к выходу блока вычисления стоимости 4m, а выход через первый вход элемента «И» 9j подключен к первому входу компаратора 10j, выход которого подключен ко второму входу элемента «И» 13j и к первому входу оперативно-запоминающего устройства 11j, выход которого соединен с первым входом сумматора 8N-1, второй вход которого подключен к выходу блока 4N вычисления стоимости, а выход через элемент «И» 9N-1 подключен к первому входу компаратора 10N-1, выход которого подключен ко второму входу элемента «И» 13N-1 и к первому входу оперативно-запоминающего устройства 11N-1, выход которого соединен с выходами оперативно-запоминающих устройств 111, 112, …, 11N-2 и со вторым входом блока отображения 16, первый вход которого соединен с выходами оперативно-запоминающих устройств 71, 72, …, 7N-1, первый вход оперативно-запоминающего устройства 7N-1 соединен со вторым входом элемента «И» 9N-1 и с выходом компаратора 6N-1, первый вход которого подключен к выходу сумматора 5N-1, второй вход которого соединен с выходом блока 3N вычисления вероятности отказов, а первый вход с выходом оперативно-запоминающего устройства 7j, первый вход которого соединен со вторым входом элемента «И» 9j и с выходом компаратора 6j, первый вход которого подключен к выходу сумматора 5j, второй вход которого соединен с выходом блока 3m вычисления вероятности отказов, а первый вход соединен с выходом оперативно-запоминающего устройства 71, первый вход которого соединен со вторым входом элемента «И» 91 и с выходом компаратора 61, первый вход которого подключен к выходу сумматора 51, первый и второй входы которого соединены соответственно с выходами блоков вычисления вероятности отказов 31 и 32.

Входная наборная панель 1 предназначена для ввода информации, представленной в десятичной системе счисления.

Управляющее устройство 2 предназначено для выработки управляющих сигналов с целью реализации требуемого алгоритма преобразования сигнала и может быть реализовано на микропроцессоре TMS 32010 [2]. Обычно управляющее устройство представляет собой последовательностные логические схемы и может быть синтезировано по известным правилам [3].

Блоки вычисления вероятности отказов 31…3N предназначены для формирования значений вероятности отказов элементов соответственно 1,…, N типов оптимизируемого объекта при использовании rk (где k=1…N) резервных элементов k-го типа. Блоки вычисления вероятности отказов 31, …, 3N идентичны, и их структурная схема может быть представлена в нескольких вариантах [1].

В частности, блок вычисления вероятности отказов, показанный на фиг.2, состоит из шифратора 17, первого-третьего элементов «И» 18, 21, 22, первого и второго умножителей 19, 20 и мультиплексора 23. Первый вход блоков вычисления вероятности отказов 31, …, 3N соединен с первым выходом входной наборной панели и является входом шифратора 17, выход которого подключен параллельно к первому входу первого элемента «И» 18, к первому и второму входу первого умножителя 19, ко второму входу второго умножителя 20, первый вход которого соединен с выходом первого умножителя 19 и с первым входом второго элемента «И» 21. Второй вход блоков вычисления вероятности отказов 31, …, 3N соединен со вторым выходом управляющего устройства 2 и является вторым входом первого элемента «И» 18, второго элемента «И» 21 и третьего элемента «И» 22, первый вход которого соединен с выходом второго умножителя 20, а выход подключен к третьему входу мультиплексора 23, первый и второй входы которого соединены соответственно с выходами первого и второго элементов «И» 18 и 21, а выход мультиплексора 23 является выходом блока вычисления вероятности отказов.

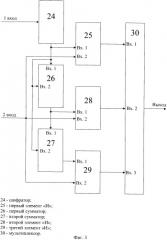

Блоки вычисления стоимости 41, …, 4N предназначены для формирования значений стоимости элементов соответственно 1, …, N типов оптимизируемого объекта при использовании rk (где k=1, …, N) резервных элементов k-го типа. Блоки вычисления стоимости 41, …, 4N идентичны, и их структурная схема может быть представлена в нескольких вариантах. В частности, блок вычисления стоимости, показанный на фиг.3, состоит из шифратора 24, первого-третьего элементов «И» 25, 28, 29 соответственно, первого и второго сумматоров 26, 27 и мультиплексора 30. Первый вход блоков вычисления стоимости 41, …, 4N соединен со вторым выходом входной наборной панели и является входом шифратора 24, выход которого подключен параллельно к первому входу первого элемента «И» 25, к первому и второму входу первого сумматора 26 и ко второму входу второго сумматора 27, первый вход которого соединен с выходом первого сумматора 26 и с первым входом второго элемента «И» 28. Второй вход блоков вычисления стоимости 41, …, 4N соединен с шестым выходом управляющего устройства 2 и является вторым входом первого элемента «И» 25, второго элемента «И» 28, третьего элемента «И» 29, первый вход которого соединен с выходом второго сумматора 27, а выход подключен к третьему входу мультиплексора 30, первый и второй входы которого соединены соответственно с выходами первого и второго элементов «И» 25 и 28, а выход мультиплексора 30 является выходом блока вычисления стоимости.

Сумматоры 51, …, 5N-1, 81, …, 8N-1, 121, …, 12N-1, а также сумматоры 26, 27, 33, 34 предназначены для выполнения операций сложения чисел, представленных в двоичном коде.

Схема сумматора известна [3] и может быть реализована на микросхеме К155ИП4 [4].

Первая 61, …, 6N-1 и вторая 101, 102, …, 10N-1 группы компараторов предназначены для сравнения значений чисел, представленных в двоичном коде, поступающих с сумматоров 51, …, 5N-1 соответственно, и с третьего выхода управляющего устройства 2 на компараторы 61, …, 6N-1, и с сумматоров 81, …, 8N-1 через элементы «И» 91, …, 9N-1 соответственно, и с пятого выхода управляющего устройства 2 на компараторы 101, 102, …, 10N-1. Схема компараторов известна [3] и может быть реализована, например, на микросхеме К555СП1 [5].

Первая 71, 72, …, 7N-1, вторая 111, 112, …, 11N-1 и третья 141, 142, …, 14N-1 группы оперативных запоминающих устройств предназначены для хранения результатов вычислений.

Элементы «И» 91, …, 9N-1 предназначены для подачи значений стоимости, поступающих на первый вход с выходов сумматоров 81, …, 8N-1 соответственно, при наличии сигнала на втором входе.

Элементы «И» 131, …, 13N-1 предназначены для подачи значения габаритов, поступающих на первый вход с выходов сумматоров 121, …, 12N-1 соответственно, при наличии сигнала на втором входе. Схема элемента «И» известна [3] и может быть реализована на микросхеме КР1561 ЛИ2 [5].

Блоки вычисления габаритов 151, …, 15N предназначены для формирования значений габаритных размеров элементов соответственно 1, …, N типов оптимизируемого объекта при использовании rk (где k=1, …, N) резервных элементов k-го типа. Блоки вычисления габаритов 151, …, 15N идентичны, и их структурная схема может быть представлена в нескольких вариантах [1]. В частности, блок вычисления стоимости, показанный на фиг.4, состоит из шифратора 31, первого-третьего элементов «И» 32, 35, 36 соответственно, первого и второго сумматоров 33, 34 и мультиплексора 37. Первый вход блоков вычисления габаритов 151, …, 15N соединен с третьим выходом входной наборной панели и является входом шифратора 31, выход которого подключен параллельно к первому входу первого элемента «И» 32, к первому и второму входу первого сумматора 33, ко второму входу второго сумматора 34, первый вход которого соединен с выходом первого сумматора 33 и с первым входом второго элемента «И» 35. Второй вход блоков вычисления габаритов 151, …, 15N соединен с седьмым выходом управляющего устройства 2 и является вторым входом первого элемента «И» 32, второго элемента «И» 35, третьего элемента «И» 36, первый вход которого соединен с выходом второго сумматора 34, а выход подключен к третьему входу мультиплексора 37, первый и второй входы которого соединены соответственно с выходами первого и второго элементов «И» 32 и 35, а выход мультиплексора 37 является выходом блока вычисления стоимости.

Блок отображения 16 предназначен для индикации оптимальных значений вероятности безотказной работы, стоимости, габаритов и количества используемых резервных элементов каждого типа. Схема устройства известна [6] и может быть реализована, например, на микросхеме К514ИД2 и семисегментном индикаторе АЛ 305А.

Шифраторы 17, 24, 31 предназначены для перевода десятичных чисел в двоичные. Схемы шифраторов известны [3] и могут быть реализованы на микросхемах КР 1564 ИВ3 [5].

Первый 18, 25 и 32, второй 21, 28 и 35 и третий 22, 29 и 36 элементы «И» предназначены для подачи соответственно на первый-третий входы мультиплексоров 23, 30 и 37 значений вероятности отказов, значений стоимости и значений габаритов при наличии на первом входе управляющего сигнала. Схемы элементов «И» известны [3] и могут быть реализованы на микросхемах КР1561 ЛИ2 [5].

Первый и второй умножители 19 и 20 предназначены для выполнения операций умножения чисел, представленных в двоичном коде. Схемы умножителей известны [3] и могут быть реализованы на микросхемах К155ИП4 [5].

Мультиплексоры 23, 30 и 37 предназначены для поочередной коммутации выходов первого 18, 25 и 32, второго 21, 28 и 35 и третьего 22, 29 и 36 элементов «И» соответственно. Схема мультиплексоров известна [3] и может быть реализована, например, на микросхеме К531КП2 [5].

Работу устройства поясним на примере [7]. В данном примере оптимизируемый объект включает три типа составных элементов и несколько резервных элементов каждого типа (число которых r1, r2, и r3 соответственно). Требуется определить количество резервных элементов каждого типа, обеспечивающих заданный уровень надежности объекта, а именно: для вероятности отказа q должно выполняться условие q≤0,025, суммарная стоимость должна отвечать требованию C≤35, при этом габариты резервируемого объекта V должны быть минимальными.

Показатели надежности в виде вероятностей отказа элементов каждого типа, стоимость и их габариты, приходящиеся на один элемент, приведены в таблице 1.

| Таблица 1. | |||

| Показатели надежности, стоимости и габаритов резервных элементов разных типов | |||

| Элемент | Вероятность отказа элемента, qi | Стоимость элемента, Ci, усл. ед. | Габариты, Vi, усл. ед. |

| 1 | 0,2 | 5 | 15 |

| 2 | 0,1 | 4 | 20 |

| 3 | 0,15 | 3 | 10 |

Из условия примера видно, что в качестве целевой функции F рассматриваются габариты резервируемого устройства, т.е. F=V. Оптимальному решению будет соответствовать условие минимума F. Технико-экономическими показателями, не вошедшим в целевую функцию F, являются уровень надежности резервируемого устройства и его стоимость. Причем по вероятности отказа устройства должно выполняться условие q≤0,025, по стоимости ≤35 усл. единиц.

При реализации устройством метода динамического программирования на первом шаге в анализ включаем элементы первого и второго типов. Далее рассматривают варианты решений, построенных из элементов первого и второго типов, и строят таблицу 2.

| Таблица 2. | |||

| Варианты решений на первом шаге (с учетом элементов первого и второго типов) | |||

| Характеристики для элемента первого типа | Характеристики для элемента второго типа | ||

| r2=0 | r2=1 | r2=2 | |

| 0,1/4/20 | 0,01/8/40 | 0,001/12/65 | |

| r1=0; 0,2/5/15 | 0,3/9/35 | 0,21/13/55 | 0,201/17/80 |

| r1=1; 0,04/10/30 | 0,14/14/50 | 0,05/18/70 | 0,041/22/95 |

| r1=2; 0,008/15/45 | 0,108/19/65 | 0,018/23/85* | 0,009/27/110* |

В ячейках таблицы 2 информация, записанная в виде: q1,2/C1,2/V1,2.

Значения q1,2, C1,2 и V1,2 подсчитаны по формулам:

;

C1,2=C1(1+r1)+C2(1+r2);

V1,2=V1(1+r1)+V2(1+r2),

где r1, r2 - количество резервных элементов соответственно первого и второго типов.

Из таблицы 2 видно, что в анализ на втором шаге следует включить ячейки (ситуации), помеченные знаками «*». Каждая из этих ситуаций на втором шаге будет рассматриваться как одна компонента.

На втором шаге в анализ включаем элемент третьего типа и снова рассматриваем компоненты, а именно: совместное решение по элементам первого и второго типов и элемент третьего типа. Затем строим таблицу с учетом отмеченных двух компонент (таблица 3):

| Таблица 3. | ||

| Варианты решений на втором шаге (с учетом элементов первого, второго и третьего типов) | ||

| Характеристики для элемента третьего типа | Варианты из таблицы 2 | |

| r1=2 r2=1 | r1=2 r2=2 | |

| 0,018/23/85 | 0,009/27/110 | |

| r3=0; 0,15/3/10 | 0,168/26/95 | 0,159/30/120 |

| r3=1; 0,023/6/20 | 0,041/29/105 | 0,032/33/130 |

| r3=2; 0,003/9/30 | 0,021/32/115* | 0,012/36/140 |

Информация, представленная в таблице 3, получена с использованием формул:

;

C1,2,3=C1,2+C3(1+r3);

V1,2,3=V1,2+V3(1+r3).

Из таблицы 3 видно, что оптимальному решению для данного примера отвечает ситуация r1=2, r2=1, r3=2. При этом вероятность отказа q=0,021, суммарная стоимость резервируемого устройства составляет 32 усл. единицы, а габаритные размеры составляют 115 усл. единиц.

На первом этапе работы устройства для решения задач оптимизации одновременно со второго, шестого и седьмого выходов управляющего устройства 2 управляющие сигналы поступают соответственно на вторые входы блоков вычисления вероятности отказа 31, 32, блоков вычисления стоимости 41, 42 и блоки вычисления габаритов 151, 152. Причем значение частоты управляющего сигнала, поступающего на вход блока вычисления вероятности отказа 32, блока вычисления стоимости 42 и блока вычисления габаритов 152 выше в три раза, чем на входы блока вычисления вероятности отказа 31, блока вычисления стоимости 41 и блока вычисления габаритов 151.

С поступлением управляющих сигналов со второго выхода управляющего устройства 2 на вторые входы блоков вычисления вероятности отказа 31 и 32 и значений вероятности отказов q1 элемента первого типа и q2 элемента второго типа с первого выхода входной наборной панели 1 на первые входы соответственно блоков вычисления вероятности отказа 31 и 32, в данных блоках происходит вычисление значений вероятности отказа оптимизируемого объекта при резерве элементов первого и второго типов r=0, r=1 и r=2.

Работа блоков вычисления вероятности отказа 31, 32, …, 3m, …, 3N идентична, поэтому рассмотрим их работу на примере блока вычисления вероятности отказа 31, показанного на фиг.2. Значение вероятности отказа q1 элемента первого типа в десятичном счислении поступает с первого входа блока вычисления вероятности отказа 31 на вход шифратора 17, с выхода которого значение вероятности отказа q1 в двоичном коде поступает на первые входы элемента «И» 18, первого умножителя 19 и на вторые входы первого и второго умножителей 19 и 20. С выхода первого умножителя 19 значение вероятности отказа поступает на первые входы второго элемента «И» 21 и второго умножителя 20, с выхода которого значение вероятности отказа поступает на первый вход третьего элемента «И» 22. На вторые входы элементов «И» 18, 21 и 22 поступает управляющий сигнал со второго входа блока вычисления вероятности отказа 31, и при наличии двух сигналов на входах элементов «И» 18, 21 и 22 значения вероятности отказов q1, , поступают соответственно на первый, второй и третий входы мультиплексора 23, который коммутирует поочередно значения вероятности отказа q1, , при r1=0, r1=1, r1=2 соответственно на свой выход.

С поступлением управляющих сигналов с шестого выхода управляющего устройства 2 на вторые входы блоков вычисления стоимости 41 и 42 и значений стоимости элементов первого и второго типов C1 и C2 с второго выхода входной наборной панели 1 на первые входы блоков вычисления стоимости 41 и 42 соответственно, в данных блоках происходит вычисление значений стоимости оптимизируемого объекта при резерве элементов первого и второго типов r=0, r=1 и r=2.

Работа блоков вычисления стоимости 41, 42, …, 4m, …, 4N идентична, поэтому рассмотрим их работу на примере блока вычисления стоимости 41, показанного на фиг.3. Значение стоимости элемента первого типа C1 в десятичном счислении поступает с первого входа блока вычисления стоимости 41 на вход шифратора 24, с выхода которого значение стоимости C1 в двоичном коде поступает на первые входы элемента «И» 25, первого сумматора 26 и на вторые входы первого и второго сумматоров 26 и 27. С выхода первого сумматора 26 значение стоимости 2C1 поступает на первые входы элемента «И» 28 и второго сумматора 27, с выхода которого значение стоимости 3C1 поступает на первый вход элемента «И» 29. На вторые входы элементов «И» 25, 28 и 29 поступает управляющий сигнал со второго входа блока вычисления стоимости 41 и при наличии двух сигналов на входах элементов «И» 25, 28 и 29 значения стоимости C1, 2C1, 3C1 с их выходов соответственно поступают на первый, второй и третий входы мультиплексора 30, который коммутирует поочередно значения стоимости одного, двух и трех элементов первого типа C1, 2C1, 3C1 соответственно на свой выход.

С поступлением управляющих сигналов с седьмого выхода управляющего устройства 2 на вторые входы блоков вычисления габаритов 151 и 152 и значений габаритов элементов первого и второго типов V1 и V2 с третьего выхода входной наборной панели 1 на первые входы блоков вычисления габаритов 151 и 152 соответственно, в данных блоках происходит вычисление значений габаритов оптимизируемого объекта при резерве элементов первого и второго типов r=0, r=1 и r=2.

Работа блоков вычисления габаритов 151, 152, …, 15m, …, 15N идентична, поэтому рассмотрим их работу на примере блока вычисления габаритов 151, показанного на фиг.4. Значение габаритов элемента первого типа V1 в десятичном счислении поступает с первого входа блока вычисления габаритов 151 на вход шифратора 31, с выхода которого значение габаритов V1 в двоичном коде поступает на первые входы первого элемента «И» 32, первого сумматора 33 и на вторые входы первого и второго сумматоров 33 и 34. С выхода первого сумматора 33 значение габаритов 2V1 поступает на первые входы второго элемента «И» 35 и второго сумматора 34, с выхода которого значение габаритов 3V1 поступает на первый вход третьего элемента «И» 36. На вторые входы элементов «И» 32, 35 и 36 поступает управляющий сигнал со второго входа блока вычисления габаритов 151 и при наличии двух сигналов на входах элементов «И» 32, 35 и 36 значения габаритов V1, 2V1, 3V1 с их выходов соответственно поступают на первый, второй и третий входы мультиплексора 37, который коммутирует поочередно значения габаритов одного, двух и трех элементов первого типа V1, 2V1, 3V1 соответственно на свой выход.

Значения вероятности отказов q1, с выхода блока вычисления вероятности отказа 31 последовательно поступают на первый вход сумматора 51, на второй вход которого поступают последовательно значения вероятности отказов q2, с выхода блока вычисления вероятности отказа 32, с выхода сумматора 51 поступают последовательно значения q1, q1+q2, , , , , , , , на первый вход компаратора 61, на второй вход которого поступает заданное значение вероятности отказа (согласно примеру qзад=0,025) с третьего выхода управляющего устройства 2. Компаратор 61 пропускае