Пиковый детектор

Иллюстрации

Показать всеИзобретение относится к области электрорадиотехники и может быть использовано в качестве многофункционального пикового детектора. Заявленное устройство содержит: шину питания; (k-1) входных шин; выходную шину; (k-1) первых компараторов напряжения с открытым коллектором (КНОК); k вторых КНОК; пороговый элемент; аналоговый ключ; повторитель напряжения; первый и второй конденсаторы; первый и второй диоды; первый, второй, третий и четвертый резисторы; n-p-n-транзистор; триггер Шмита; k третьих и k четвертых диодов; k пятых, k шестых, k седьмых, k восьмых, k девятых резисторов; k третьих конденсаторов. Техническим результатом изобретения является расширение функциональных возможностей пикового детектора. 2 ил.

Реферат

Изобретение относится к области электрорадиотехники и может быть использовано в качестве многофункционального пикового детектора.

Известен пиковый детектор импульсов положительных сигналов (см. Коломбет Е.А. «Микроэлектронные средства обработки аналоговых сигналов», М., Радио и связь, 1991 г., стр.236, рис.8.10), содержащий операционный усилитель, неинвертирующий вход которого через первый резистор подключен к источнику входного сигнала и через первый диод к выходу повторителя напряжения, выход которого через второй резистор подключен к аноду второго диода и инвертирующему входу операционного усилителя, выход которого подключен к катоду второго диода и базе npn-транзистора, коллектор которого через третий резистор подключен к шине источника питания, эмиттер npn-транзистора подключен к точке объединения входа повторителя напряжения и первой обкладке запоминающего конденсатора, вторая обкладка которого подключена к общей шине.

Недостатками пикового детектора импульсов положительных сигналов являются:

- ограниченные функциональные возможности, т.к. он не выполняет функцию выделения и запоминания максимального значения амплитуды двуполярного сигнала из k-входных сигналов из-за особенностей структуры схемы;

- необходимость двуполярного питания из-за использования операционного усилителя с диодной цепью ограничения насыщения в первом каскаде;

- нестабильное напряжение смещения нуля из-за отсутствия цепей коррекции устойчивости неинвертирующего пикового детектора, охваченного общей обратной связью.

Наиболее близким по технической сущности к предлагаемому изобретению является преобразователь амплитуды прямоугольных импульсов в постоянное напряжение (см. А.С. №1265630 МПК G01R 19/04 «Преобразователь амплитуды прямоугольных импульсов в постоянное напряжение» авторов В.В.Немирова, А.И.Иванова, опубликовано 23.10.86 г. БИ №39), содержащий резистивный делитель напряжения, компаратор напряжения, разрядный ключ, а также последовательно соединенные дифференциальный операционный усилитель, диодно-емкостную зарядную ячейку и повторитель напряжения, выход которого подключен к выходной шине, инвертирующему входу дифференциального операционного усилителя, и через резистивный делитель напряжения - к первому входу компаратора, второй вход которого соединен с входной шиной и неинвертирующим входом дифференциального операционного усилителя, причем выход разрядного ключа подключен к входу повторителя напряжения, элемент И и пороговый элемент, вход которого соединен с входной шиной, причем входы элемента И соединены с выходами компаратора и порогового элемента соответственно, а его выход - с управляющим входом разрядного ключа. Аналоговый разрядный ключ выполнен с инвертирующим управляющим входом по схеме с общим эмиттером на n-p-n-транзисторе.

Недостатками преобразователя амплитуды прямоугольных импульсов в постоянное напряжение являются:

- не выполняет функцию выделения и запоминания максимального значения двуполярной амплитуды из k-входных сигналов из-за особенностей структуры схемы;

- не обеспечивает нормированное время хранения для считывания расширенного выходного импульса внешними считывающими устройствами и последующее быстрое обнуление выходного импульса за счет отсутствия времязадающих цепей;

- необходимость двуполярного питания из-за использования дифференциального операционного усилителя;

- отсутствие защиты выхода дифференциального операционного усилителя и диода диодно-емкостной зарядной ячейки от токовой перегрузки в момент разряда конденсатора диодно-емкостной зарядной ячейки разрядным ключом.

Технический результат, на достижение которого направлено изобретение, заключается в расширении функциональных возможностей.

Для достижения данного технического результата в пиковом детекторе, содержащем входную шину и шину питания, первый компаратор напряжения с открытым коллектором (КНОК), пороговый элемент, аналоговый ключ, первый выход которого соединен с общей шиной, а второй выход соединен с первым выводом первого конденсатора и входом повторителя напряжения, выход которого соединен с выходной шиной и инвертирующим входом первого КНОК, первый диод, новым является то, что дополнительно введены вторые диод и конденсатор, первый, второй, третий и четвертый резисторы, n-p-n-транзистор, триггер Шмитта, (k-1) входных шин, (k-1) первых КНОК, k вторых КНОК, k третьих и k четвертых диодов, k пятых, k шестых, k седьмых, k восьмых и k девятых резисторов, k третьих конденсаторов, где k=1, 2, …, общая шина через первый резистор соединена со вторым выводом первого конденсатора, первый вывод которого соединен с эмиттером n-p-n-транзистора, база которого соединена через второй резистор с выходной шиной и с анодом первого диода, катод которого соединен с управляющим входом аналогового ключа и выходом триггера Шмитта, вход которого соединен через второй конденсатор с общей шиной и через третий резистор с анодом второго диода и первым выводом четвертого резистора, второй вывод которого соединен с катодом второго диода и выходом порогового элемента, вход которого соединен с первыми выводами пятых резисторов, инвертирующими входами дополнительных первых КНОК и выходной шиной, шина питания соединена с первыми выводами шестых и седьмых резисторов и коллектором n-p-n-транзистора, база которого соединена с точкой объединения катодов третьих и четвертых диодов, анод каждого третьего диода соединен со вторым выводом соответствующего шестого резистора и выходом соответствующего второго КНОК, неинвертирующий вход каждого второго КНОК соединен с общей шиной, а инвертирующий вход соединен со вторым выводом соответствующего пятого резистора и через соответствующий восьмой резистор с соответствующей входной шиной, каждая входная шина через соответствующий девятый резистор соединена с неинвертирующим входом соответствующего первого КНОК, выход которого соединен со вторым выводом соответствующего седьмого резистора, анодом соответствующего четвертого диода и через соответствующий третий конденсатор с общей шиной.

Аналоговый ключ выполнен на последовательно соединенных логическом элементе НЕ, вход которого является управляющим неинвертирующим входом аналогового ключа, и разрядном ключе с общим эмиттером на n-p-n-транзисторе.

Триггер Шмитта выполнен на логическом элементе с ограничительным резистором на входе.

Расширенные функциональные возможности обеспечиваются:

- выделением максимального значения двуполярной амплитуды аналогового сигнала по входным шинам за счет одновременной работы аналого-цифровых компараторов напряжения с открытым коллектором на суммирующий n-p-n-транзистор, защищенный от перегрузки первым диодом, и заменой аналоговой схемы операционного усилителя ближайшего аналога на аналого-цифровую схему компараторов напряжения с открытым коллектором и девятыми ограничительными резисторами. Благодаря этому количество входных шин и обрабатываемых сигналов легко наращивается параллельным подключением выходов дополнительных компараторов напряжения через соответствующие диоды в одну суммирующую точку на базу n-p-n-транзистора, ускоряющего заряд первого (запоминающего) конденсатора;

- нормированным временем хранения для считывания очередного расширенного выходного импульса внешними считывающими устройствами и последующим быстрым обнулением выходного импульса за счет введения времязадающей цепи (на пороговом элементе, резисторах, втором конденсаторе и триггере Шмитта) с медленным зарядом и быстрым разрядом второго конденсатора, подключенной к управляющему входу аналогового ключа и катоду первого диода;

- однополярным питанием без снижения быстродействия за счет введения компараторов напряжения с открытым коллектором вместо операционного усилителя ближайшего аналога;

- введением защиты n-p-n-транзистора от токовой перегрузки в момент разряда аналоговым ключом запоминающего первого конденсатора с помощью защитного первого диода, удерживающего близкое к нулевому (0,3 В) напряжение на базе n-p-n-транзистора.

Кроме того, в режиме хранения уменьшена погрешность вследствие меньшего изменения напряжения на запоминающем первом конденсаторе за счет выравнивания потенциалов на базе и эмиттере n-p-n-транзистора вторым резистором, подключенным к выходу повторителя напряжения и базе n-p-n-транзистора.

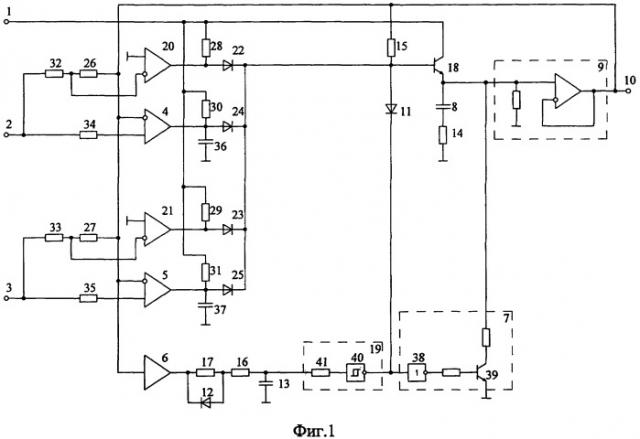

На фиг.1 представлен пример реализации функциональной схемы пикового детектора при k=2. На фиг.2 приведены временные диаграммы работы пикового детектора.

Пиковый детектор (фиг.1) содержит шину 1 питания, входные шины 2 и 3, первые компараторы напряжения с открытым коллектором 4 и 5 (КНОК), пороговый элемент 6, аналоговый ключ 7, первый конденсатор 8, повторитель напряжения 9, выходную шину 10, первый диод 11, второй диод 12, второй конденсатор 13, первый, второй, третий и четвертый резисторы 14, 15, 16 и 17 соответственно, n-p-n- транзистор 18, триггер Шмитта 19, вторые КНОК 20 и 21, третьи диоды 22 и 23, четвертые диоды 24 и 25, пятые 26 и 27, шестые 28 и 29, седьмые 30 и 31, восьмые 32 и 33 и девятые 34 и 35 резисторы, третьи конденсаторы 36 и 37.

Первый выход аналогового ключа 7 соединен с общей шиной, а второй выход соединен с входом повторителя напряжения 9, эмиттером n-p-n-транзистора 18 и через последовательно соединенные первые конденсатор 8 и резистор 14 с общей шиной. Выход повторителя напряжения 7 соединен с выходной шиной 10, входом порогового элемента 6, инвертирующими входами первых КНОК 4 и 5, первыми выводами пятых резисторов 26 и 27 и через второй резистор 15 с базой n-p-n-транзистора 18. База n-p-n-транзистора 18 соединена с анодом первого диода 11 и точкой объединения катодов третьих 22, 23 и четвертых 24, 25 диодов. Катод первого диода 11 соединен с управляющим входом аналогового ключа 7 и выходом триггера Шмитта 19. Вход триггера Шмитта 19 соединен через второй конденсатор 13 с общей шиной и через третий резистор 16 с анодом второго диода 12 и первым выводом четвертого резистора 17. Второй вывод четвертого резистора 17 соединен с катодом второго диода 12 и выходом порогового элемента 6. Шина 1 питания соединена с коллектором n-p-n-транзистора 18 и с первыми выводами шестых 28, 29 и седьмых 30, 31 резисторов. Аноды третьих диодов 22, 23 соединены со вторыми выводами шестых резисторов 28, 29 соответственно и выходами соответствующих вторых КНОК 20, 21. Неинвертирующие входы вторых КНОК 20, 21 соединены с общей шиной, а инвертирующие входы соединены со вторыми выводами соответствующих пятых резисторов 26, 27 и через соответствующие восьмые резисторы 32, 33 с соответствующими входными шинами 2, 3. Входные шины 2 и 3 через соответствующие девятые резисторы 34, 35 соединены с неинвертирующими входами соответствующих первых КНОК 4, 5, выходы которых соединены со вторыми выводами соответствующих седьмых резисторов 30, 31, анодами соответствующих четвертых диодов 24, 25 и через соответствующие третьи конденсаторы 36, 37 с общей шиной.

Аналоговый ключ 7 выполнен на последовательно соединенных логическом элементе НЕ 38, вход которого является управляющим неинвертирующим входом, и разрядном ключе с общим эмиттером на n-p-n-транзисторе 39.

Триггер Шмитта 19 выполнен на логическом элементе 40 с ограничительным резистором 41 на входе.

Положительные выводы питания КНОК 4, 5 и 20, 21 и повторителя напряжения 9 подключены к шине 1 питания, а отрицательные их выводы питания - к общей шине (на фиг.1 не показано).

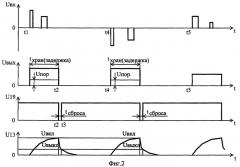

На фигуре 2 представлены временные диаграммы работы пикового детектора (фиг.2), где:

Uвх - разнополярные импульсы напряжений произвольной амплитуды и длительности на входных шинах 2 и 3, начиная с момента t1 и далее;

Uвых - выходные импульсы, равные максимальным амплитудам импульсов с входных шин 2 и 3, расширенные по длительности до заданной временем записи запоминающего устройства (на фиг.1 не показано) tХРАН;

U13 - экспоненциальные импульсы (после момента t1) напряжения заряда и разряда конденсатора 13 напряжением логической единицы и логического нуля соответственно с выхода порогового элемента 6;

Uвкл - верхний пороговый уровень триггера Шмитта 19;

Uвыкл - нижний пороговый уровень триггера Шмитта 19;

U19 - временная диаграмма напряжения на выходе триггера Шмитта 19.

Пиковый детектор работает следующим образом.

В исходном статическом состоянии до момента t1 на фиг.2 напряжение на входных шинах 2, 3 равно нулю. КНОК 4, 5 и 20, 21 находятся в состоянии логического нуля по выходу за счет небольшого (несколько милливольт) напряжения смещения на их инвертирующих входах, образуемого входными вытекающими токами смещения КНОК, протекающими по большим сопротивлениям резисторов 32, 33 и 26, 27.

Сопротивление резисторов 34, 35 много меньше сопротивления каждого из резисторов 32, 33 и 26, 27, что не влияет на устойчивое статическое состояние КНОК 4, 5 и 20, 21.

На объединенных катодах диодов 22, 23 и 24, 25, входе и выходе повторителя напряжения 9 (неинвертирующего) также присутствует «нулевое» (несколько милливольт) напряжение. «Нулевое» напряжение с выхода повторителя напряжения 9 ниже величины (0,2 В) порогового напряжения Uпор (см. Uвых на фиг.2) порогового элемента 6 (неинвертирующего), то есть на выходе его и конденсаторе 13 также «нулевое» напряжение, а значит на инверсном выходе триггера Шмитта 19 напряжение логической единицы, которым заперт диод 11, и через логический элемент НЕ 38 логическим нулем заперт n-p-n-транзистор 39 аналогового ключа 7.

Резисторы 34, 35 ограничительные для КНОК 4, 5 при отрицательной полярности входного сигнала на входных шинах 2, 3. Пороговый элемент 6 - компаратор напряжения, подобный элементам 4, 5 и 20, 21 или подобный аналоговому ключу 7 с общим эмиттером на n-p-n-транзисторе 39. Корректирующие резистор 14 и конденсаторы 36, 37 обеспечивают устойчивую работу пикового детектора в широком диапазоне входных сигналов и температур окружающей среды. КНОК 4, 5 выполняют функцию сравнения напряжений, а КНОК 20, 21 с резисторами 26, 27 и 32, 33 выполняют функцию сравнения токов.

При поступлении на входные шины 2, 3 и неинвертирующие входы КНОК 4, 5 положительных импульсов (см. t1 на Uвх на фиг.2) КНОК 4, 5 переключаются в состояние логической единицы по выходу и через диоды 24, 25 и n-p-n-транзистор 18 заряжают конденсатор 8. Через повторитель напряжения 9 это напряжение в виде сигнала отрицательной обратной связи подается на инвертирующие входы КНОК 4, 5, возвращая их в состояние логического нуля при выравнивании амплитуд импульсов напряжений входных шин 2, 3 и сигнала обратной связи на дифференциальных входах КНОК 4, 5.

В течение положительных входных импульсов, поступающих на инвертирующий вход КНОК 20, 21, которые, находятся в состоянии логического нуля, диоды 22, 23 заперты и не участвуют в работе.

Напряжение на конденсаторе 8 существует в течение времени хранения tхран, длительность которого определяется постоянной времени заряда конденсатора 13 через резисторы 16, 17 напряжением логической единицы с выхода неинвертирующего порогового элемента 6, т.к. превышен пороговый уровень Uпор на его входе. При достижении напряжением U13 конденсатора 13 величины Uвкл триггер Шмитта 19 переключается в состояние логического нуля по выходу и через элемент НЕ 38 открывает разрядный ключ на n-p-n-транзисторе 39, разряжая конденсатор 8 за короткое время t2-t3. При этом диод 11 открыт, а значит, напряжение на базе n-p-n-транзистора 18 равно 0,3 В, что недостаточно для его отпирания, и следовательно, n-p-n-транзистор 18 защищен от токовой перегрузки даже в случае длинных входных положительных импульсов на входных шинах 2, 3 (на фиг.2 не показаны).

При поступлении на входные шины 2, 3 и инвертирующие входы КНОК 20, 21 отрицательных импульсов (см. t4 на Uвх на фиг.2) КНОК 20, 21 переключаются в состояние логической единицы по выходу и через открытые диоды 22, 23 и n-p-n-транзистор 18 заряжается конденсатор 8. Через повторитель напряжения 9 это напряжение в виде сигнала отрицательной обратной связи подается на резисторы 32, 33 и 26, 27 и инвертирующие входы КНОК 20, 21, возвращая их в состояние логического нуля при выравнивании амплитуд импульсов токов на инвертирующих входах в резисторах 32, 33 и 26, 27.

В течение отрицательных входных импульсов, поступающих на неинвертирующие входы КНОК 4, 5, которые находятся в состоянии логического нуля, диоды 24, 25 закрыты и не участвуют в работе.

Положительное напряжение на конденсаторе 8 существует в течение времени хранения tхран, длительность которого определяется постоянной времени заряда конденсатора 13 через резисторы 16, 17 напряжением логической единицы с выхода порогового элемента 6, т.к. превышен пороговый уровень Uпор на его входе. При достижении напряжением U13 конденсатора 13 величины Uвкл триггер Шмитта 19 переключается в состояние логического нуля по выходу и через элемент НЕ 38 открывает разрядный ключ на n-p-n-транзисторе 39, разряжая конденсатор 8 за короткое время tсброса. При этом диод 11 открыт, а значит, напряжение на базе n-p-n-транзистора 18 равно 0,3 В, что недостаточно для его отпирания, и следовательно, n-p-n-транзистор 18 защищен от токовой перегрузки даже в случае длинных входных отрицательных импульсов на входных шинах 2, 3 (на фиг.2 не показаны).

Величина tХРАН на порядок меньше, чем постоянная времени разряда запоминающего конденсатора 8 на высоком входном сопротивлении повторителя напряжения, что обеспечивает стабильность запомненной амплитуды. Импульсы стабилизированы по амплитуде и длительности выбранной величиной tхран задержки сброса напряжения запоминающего конденсатора 8 (tсброса) при заряде вспомогательного конденсатора 13 (см. U13 на фиг.2) через резисторы 17, 16 с нижнего до верхнего порогового уровня триггера Шмитта 19. Эти же импульсы присутствуют на входе и выходе повторителя напряжения 9, начиная с момента t1 и далее. Длительность этих импульсов определяет время хранения tХРАН (время задержки сброса) и должна быть достаточна для переноса во внешнее запоминающее устройство максимальной амплитуды очередных запомненных импульсов.

Короткие импульсы tСБРОСА образуются в результате быстрого разряда конденсатора 13 через резистор 16 и диод 12 с верхнего до нижнего порогового уровня триггера Шмитта 19. Длительность этих импульсов (см. на фиг.2) определяет время открытого состояния аналогового ключа 7 и должна быть достаточна для полного разряда (сброса напряжения) конденсатора 8.

При поступлении в момент t5 на входные шины 2, 3 импульсов с амплитудой, меньшей амплитуды предыдущих импульсов, в схеме происходит процесс, аналогичный вышеописанному, но, в отличие от ближайшего аналога, обеспечивается гарантированное время хранения tхран для переноса в запоминающее устройство предыдущего импульса большей амплитуды.

В предлагаемом пиковом детекторе расширены функциональные возможности:

- обеспечена функция выделения максимальной по абсолютному значению и разнополярной амплитуды благодаря одновременной работе КНОК 20, 21 и 4, 5, диодов 22, 23 и 24, 25 на суммирующий транзистор 18;

- обеспечивается слежение за амплитудой входных сигналов и надежный перенос хранимых значений во внешнее запоминающее устройство благодаря нормализации по длительности времени хранения;

- обеспечивается защита от токовой перегрузки путем запирания n-p-n-транзистора 18 при разряде конденсатора 8 аналоговым ключом 7, защитным диодом 11.

Испытания макета пикового детектора подтвердили его работоспособность и заявленные преимущества в диапазоне рабочих температур от -40° до +50°С.

Пиковый детектор, содержащий шину питания, входную шину и первый компаратор напряжения с открытым коллектором (КНОК), пороговый элемент, аналоговый ключ, первый выход которого соединен с общей шиной, а второй выход соединен с первым выводом первого конденсатора и входом повторителя напряжения, выход которого соединен с выходной шиной и инвертирующим входом первого КНОК, первый диод, отличающийся тем, что дополнительно введены вторые диод и конденсатор, первый, второй, третий и четвертый резисторы, n-p-n-транзистор, триггер Шмитта, (k-1) входных шин, (k-1) первых КНОК, k вторых КНОК, k третьих и k четвертых диодов, k пятых, k шестых, k седьмых, k восьмых и k девятых резисторов, k третьих конденсаторов, где k=1, 2, …, общая шина через первый резистор соединена со вторым выводом первого конденсатора, первый вывод которого соединен с эмиттером n-p-n-транзистора, база которого соединена через второй резистор с выходной шиной и с анодом первого диода, катод которого соединен с управляющим входом аналогового ключа и выходом триггера Шмитта, вход которого соединен через второй конденсатор с общей шиной и через третий резистор - с анодом второго диода и первым выводом четвертого резистора, второй вывод которого соединен с катодом второго диода и выходом порогового элемента, вход которого соединен с первыми выводами пятых резисторов, инвертирующими входами дополнительных первых КНОК и выходной шиной, шина питания соединена с первыми выводами шестых и седьмых резисторов и коллектором n-p-n-транзистора, база которого соединена с точкой объединения катодов третьих и четвертых диодов, анод каждого третьего диода соединен со вторым выводом соответствующего шестого резистора и выходом соответствующего второго КНОК, неинвертирующий вход каждого второго КНОК соединен с общей шиной, а инвертирующий вход соединен со вторым выводом соответствующего пятого резистора и через соответствующий восьмой резистор - с соответствующей входной шиной, каждая входная шина через соответствующий девятый резистор соединена с неинвертирующим входом соответствующего первого КНОК, выход которого соединен со вторым выводом соответствующего седьмого резистора, анодом соответствующего четвертого диода и через соответствующий третий конденсатор - общей шиной.