Каскодный дифференциальный усилитель с малым напряжением смещения нуля

Иллюстрации

Показать всеИзобретение относится к радиотехнике и связи для усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях с малыми значениями напряжения смещения нуля (ОУ)). Технический результат: уменьшение напряжения смещения нуля (UСМ). Каскодный дифференциальный усилитель содержит входной (1) параллельно-балансный каскад, первый (2) и второй (3) токовые выходы которого подключены к соответствующим первому (4) и второму (5) выходным транзисторам (Т) и через первый (6) и второй (7) токостабилизирующие двухполюсники (ТД) соединены с первой (8) шиной источника питания (ИП), выходной эмиттерный повторитель (9), входной Т (10) которого имеет такой же тип проводимости, что первый Т (4) и второй Т (5), вспомогательный Т (11), база которого подключена к коллектору первого Т (4) и через третий ТД (12) соединена со второй (13) шиной ИП, а эмиттер подключен к объединенным базам первого Т (4) и второго Т (5), причем коллектор второго Т (5) связан с базой входного Т (10) выходного эмиттерного повторителя (9) и через четвертый ТД (14) соединен со второй (13) шиной ИП. Третий ТД (12) и четвертый ТД (14) выполнены на основе первого (15) и второго (16) дополнительных Т, базы которых подключены к цепи установления статического режима (17), эмиттеры связаны со второй (13) шиной ИП через первый (18) и второй (19) дополнительные резисторы, а коллектор Т (11) связан с эмиттером первого Т (15). 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях с малыми значениями напряжения смещения нуля (ОУ)).

Известны схемы дифференциальных усилителей (ДУ) на основе так называемых «перегнутых» каскодов [1-12], которые стали основой более чем 20 серийных операционных усилителей (НА2520, НА5190, AD797, AD8631, AD8632, ОР90 и др.). В связи с высокой популярностью такой архитектуры ДУ на их модификации выдано более 50 патентов. Предлагаемое изобретение относится к данному подклассу устройств.

Ближайшим прототипом заявляемого устройства является ДУ, описанный в патенте фирмы National Semiconductor США №5420540 (фиг.1), содержащий входной 1 параллельно-балансный каскад, первый 2 и второй 3 токовые выходы которого подключены к соответствующим первому 4 и второму 5 выходным транзисторам и через первый 6 и второй 7 токостабилизирующие двухполюсники соединены с первой 8 шиной источника питания, выходной эмиттерный повторитель 9, входной транзистор 10 которого имеет такой же тип проводимости, что и первый 4 и второй 5 выходные транзисторы, вспомогательный транзистор 11, база которого подключена к коллектору первого 4 выходного транзистора и через третий 12 токостабилизирующий двухполюсник соединена со второй 13 шиной источника питания, а эмиттер подключен к объединенным базам первого 4 и второго 5 выходных транзисторов, причем коллектор второго 5 выходного транзистора связан с базой входного транзистора 10 выходного эмиттерного повторителя 9 и через четвертый 14 токостабилизирующий двухполюсник соединен со второй 13 шиной источника питания.

Существенный недостаток известного каскодного дифференциального усилителя состоит в том, что он характеризуется сравнительно большим напряжением смещения нуля (Uсм).

Основная задача предлагаемого изобретения состоит в уменьшении напряжения смещения нуля (Uсм).

Поставленная задача достигается тем, что в известном ДУ, содержащем входной 1 параллельно-балансный каскад, первый 2 и второй 3 токовые выходы которого подключены к соответствующим первому 4 и второму 5 выходным транзисторам и через первый 6 и второй 7 токостабилизирующие двухполюсники соединены с первой 8 шиной источника питания, выходной эмиттерный повторитель 9, входной транзистор 10 которого имеет такой же тип проводимости, что и первый 4 и второй 5 выходные транзисторы, вспомогательный транзистор 11, база которого подключена к коллектору первого 4 выходного транзистора и через третий 12 токостабилизирующий двухполюсник соединена со второй 13 шиной источника питания, а эмиттер подключен к объединенным базам первого 4 и второго 5 выходных транзисторов, причем коллектор второго 5 выходного транзистора связан с базой входного транзистора 10 выходного эмиттерного повторителя 9 и через четвертый 14 токостабилизирующий двухполюсник соединен со второй 13 шиной источника питания, предусмотрены новые связи - третий 12 и четвертый 14 токостабилизирующие двухполюсники выполнены на основе первого 15 и второго 16 дополнительных транзисторов, базы которых подключены к цепи установления статического режима 17, эмиттеры связаны со второй 13 шиной источника питания через первый 18 и второй 19 дополнительные резисторы, а коллектор вспомогательного транзистора 11 связан с эмиттером первого 15 дополнительного транзистора.

На фиг.1 показана схема каскодного дифференциального усилителя-прототипа.

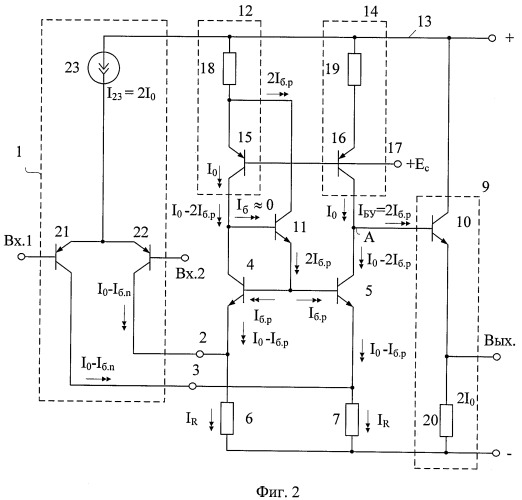

На фиг.2 представлена схема заявляемого ДУ.

На фиг.3 представлен вариант построения ДУ фиг.1 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». Здесь (без учета разброса параметров элементов) Uсм=-1,35 мВ.

На фиг.4 представлен заявляемый ДУ в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». Здесь Uсм=113,3 мкВ.

На фиг.5 приведена схема фиг.4 со специальным транзистором VT15, который повышает температурную стабильность Uсм ДУ фиг.4.

На фиг.6 приведены температурные зависимости Uсм ДУ фиг.3, фиг.4, фиг.5.

Каскодный дифференциальный усилитель фиг.2 содержит входной 1 параллельно-балансный каскад, первый 2 и второй 3 токовые выходы которого подключены к соответствующим первому 4 и второму 5 выходным транзисторам и через первый 6 и второй 7 токостабилизирующие двухполюсники соединены с первой 8 шиной источника питания, выходной эмиттерный повторитель 9, входной транзистор 10 которого имеет такой же тип проводимости, что и первый 4 и второй 5 выходные транзисторы, вспомогательный транзистор 11, база которого подключена к коллектору первого 4 выходного транзистора и через третий 12 токостабилизирующий двухполюсник соединена со второй 13 шиной источника питания, а эмиттер подключен к объединенным базам первого 4 и второго 5 выходных транзисторов, причем коллектор второго 5 выходного транзистора связан с базой входного транзистора 10 выходного эмиттерного повторителя 9 и через четвертый 14 токостабилизирующий двухполюсник соединен со второй 13 шиной источника питания. Третий 12 и четвертый 14 токостабилизирующие двухполюсники выполнены на основе первого 15 и второго 16 дополнительных транзисторов, базы которых подключены к цепи установления статического режима 17, эмиттеры связаны со второй 13 шиной источника питания через первый 18 и второй 19 дополнительные резисторы, а коллектор вспомогательного транзистора 11 связан с эмиттером первого 15 дополнительного транзистора.

В частном случае выходной эмиттерный повторитель 9 содержит резистор 10, а входной каскад 1 реализован на базе транзисторов 21, 22 и двухполюснике 23.

Рассмотрим работу заявляемого устройства (фиг.2).

Статический режим по току транзисторов 4 и 5 ДУ фиг.2 определяется транзисторами 15 и 16. Токи коллекторов этих транзисторов:

Поэтому эмиттерные токи транзисторов 4 и 5

где Iб.p - ток базы транзисторов 4 и 5.

При идентичных резисторах 6 и 7 и одинаковых токах выходов 2 и 3 эмиттерный ток транзистора 5 будет равен эмиттерному току транзистора 4

Таким образом, ток коллектора транзистора 5

Для цепи базы транзистора 10 (узел «А»)

Из последнего уравнения следует, что при IБУ=2Iб.р условием взаимной компенсации токов в цепи базы транзистора 10 и, как следствие, малых напряжений Uсм будет равенство

Поэтому предлагаемая схема ДУ имеет более низкие значения Uсм.

Данные теоретические выводы подтверждаются результатами моделирования схем фиг.3, фиг.4, фиг.5. Численные значения систематической составляющей Uсм (без учета разброса параметров элементов) лежат для предлагаемых схем в диапазоне до 150 мкВ. В то же время в ДУ-прототипе Uсм изменяется единицами милливольт (Uсм≈1,5 мВ).

Таким образом, заявляемое устройство имеет существенное преимущество в сравнении с ДУ-прототипом.

Источники информации

1. Патент США №5422600;

2. Патент США №4644295 (НА-2539);

3. Патент США №5734296;

4. Патент США №4293824;

5. Патент США №5420540;

6. Патент США №5952882;

7. Патент США №6717466;

8. Патент США №6542030;

9. Патент США №5422600;

10. Патент США №6456162;

11. Патент США №6456163;

12. Патент США №6617466.

Каскодный дифференциальный усилитель, содержащий входной (1) параллельно-балансный каскад, первый (2) и второй (3) токовые выходы которого подключены к соответствующим первому (4) и второму (5) выходным транзисторам и через первый (6) и второй (7) токостабилизирующие двухполюсники соединены с первой (8) шиной источника питания, выходной эмиттерный повторитель (9), входной транзистор (10) которого имеет такой же тип проводимости, что и первый (4) и второй (5) выходные транзисторы, вспомогательный транзистор (11), база которого подключена к коллектору первого (4) выходного транзистора и через третий (12) токостабилизирующий двухполюсник соединена со второй (13) шиной источника питания, а эмиттер подключен к объединенным базам первого (4) и второго (5) выходных транзисторов, причем коллектор второго (5) выходного транзистора связан с базой входного транзистора (10) выходного эмиттерного повторителя (9) и через четвертый (14) токостабилизирующий двухполюсник соединен со второй (13) шиной источника питания, отличающийся тем, что третий (12) и четвертый (14) токостабилизирующие двухполюсники выполнены на основе первого (15) и второго (16) дополнительных транзисторов, базы которых подключены к цепи установления статического режима (17), эмиттеры связаны со второй (13) шиной источника питания через первый (18) и второй (19) дополнительные резисторы, а коллектор вспомогательного транзистора (11) связан с эмиттером первого (15) дополнительного транзистора.