Комплементарный дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к радиотехнике и связи для усиления аналоговых сигналов с широким динамическим диапазоном в структуре аналоговых микросхем различного функционального назначения (например, прецизионных операционных усилителях (ОУ)). Технический результат: уменьшение абсолютного значения UСМ и его температурного дрейфа. Комплементарный дифференциальный усилитель содержит первый (1) и второй (2) входные транзисторы (Т), коллекторы которых подключены к коллектору первого (3) вспомогательного Т, первый (4) и второй (5) выходные Т, базы которых объединены и подключены к коллектору второго (6) вспомогательного Т и первому (7) токостабилизирующему двухполюснику (ТД), эмиттер первого Т (1) соединен с эмиттером первого Т (4), эмиттер второго Т (2) соединен с эмиттером второго Т (5), токовое зеркало (8), вход которого соединен с коллектором первого Т (4), а выход подключен к коллектору второго Т (5) и связан с базой третьего Т (9), эмиттер которого подключен ко второму ТД (10) и связан с выходом устройства, причем базы первого Т (3) и второго Т (6) связаны друг с другом. В схему введен дополнительный Т (11), база которого подключена к коллектору первого Т (3), эмиттер соединен с базами первого Т (3) и второго Т (6), а коллектор подключен ко входу токового зеркала (8). 2 з.п. ф-лы, 7 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном в структуре аналоговых микросхем различного функционального назначения (например, прецизионных операционных усилителях (ОУ)).

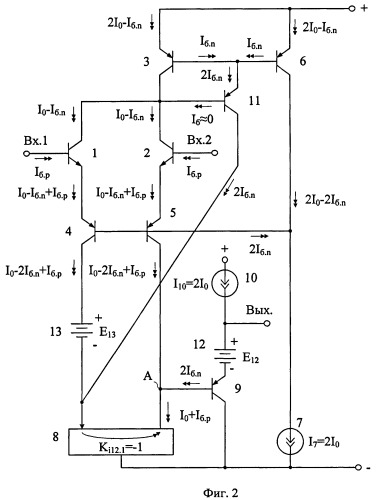

Существует несколько базовых архитектур дифференциальных каскадов (ДК). Одна из них (фиг.1), которая относится к классической архитектуре, была впервые использована в операционном усилителе µА741.

Известны схемы дифференциальных усилителей (ДУ) на n-p-n и р-n-р транзисторах с так называемой «архитектурой входного каскада операционного усилителя µА741» [1-7]. На их модификации выдано более 50 патентов для ведущих микроэлектронных фирм мира. Дифференциальные усилители данного класса, наряду с типовым параллельно-балансным каскадом, стали основным усилительным элементом многих аналоговых интерфейсов. Предлагаемое изобретение относится к данному подклассу устройств.

Наиболее близким по сущности к заявляемому техническому решению является классическая схема ДУ фиг.1, представленная в патенте фирмы Motorola США №4.030.044, которая также присутствует в большом числе других патентов, например [1-7].

Существенный недостаток известного ДУ фиг.1 состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм), зависящей от свойств его архитектуры.

Основная задача предлагаемого изобретения состоит в уменьшении абсолютного значения Uсм и его температурного дрейфа.

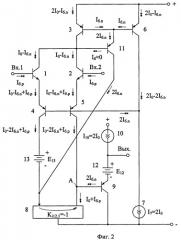

Поставленная задача достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, коллекторы которых подключены к коллектору первого 3 вспомогательного транзистора, первый 4 и второй 5 выходные транзисторы, базы которых объединены и подключены к коллектору второго 6 вспомогательного транзистора и первому 7 токостабилизирующему двухполюснику, эмиттер первого 1 входного транзистора соединен с эмиттером первого 4 выходного транзистора, эмиттер второго 2 входного транзистора соединен с эмиттером второго 5 выходного транзистора, токовое зеркало 8, вход которого соединен с коллектором первого 4 выходного транзистора, а выход подключен к коллектору второго 5 выходного транзистора и связан с базой третьего 9 вспомогательного транзистора, эмиттер которого подключен ко второму 10 токостабилизирующему двухполюснику и связан с выходом устройства, причем базы первого 3 и второго 6 вспомогательных транзисторов связаны друг с другом, предусмотрены новые элементы и связи - в схему введен дополнительный транзистор 11, база которого подключена к коллектору первого 3 вспомогательного транзистора, эмиттер соединен с базами первого 3 и второго 6 вспомогательных транзисторов, а коллектор подключен ко входу токового зеркала 8.

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 показано заявляемое устройство в соответствии с п.1 формулы изобретения.

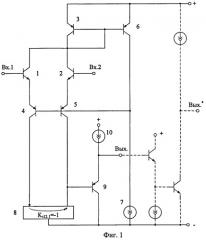

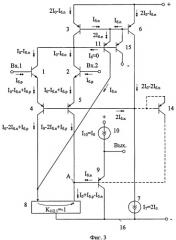

На фиг.3 представлена схема ДУ, соответствующая п.1, п.2 и п.3 формулы изобретения.

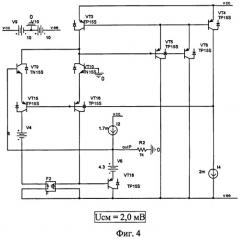

На фиг.4 и 5 показаны схемы дифференциального усилителя - прототипа (фиг.4) и заявляемого ДУ (фиг.5) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». Для более эффективного сравнения известного и заявляемого устройств токовые зеркала в их коллекторных цепях выполнены по одинаковой схеме. При этом можно показать, что свойства схемы фиг.4 по величине Uсм такие же, как и ДУ фиг.1.

На фиг.6 приведена схема заявляемого устройства, соответствующая п.1, п.2 и п.3 формулы изобретения, совпадающая с фиг.3.

На фиг.7 приведены температурные зависимости напряжения смещения нуля схем фиг.4, фиг.5.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, коллекторы которых подключены к коллектору первого 3 вспомогательного транзистора, первый 4 и второй 5 выходные транзисторы, базы которых объединены и подключены к коллектору второго 6 вспомогательного транзистора и первому 7 токостабилизирующему двухполюснику, эмиттер первого 1 входного транзистора соединен с эмиттером первого 4 выходного транзистора, эмиттер второго 2 входного транзистора соединен с эмиттером второго 5 выходного транзистора, токовое зеркало 8, вход которого соединен с коллектором первого 4 выходного транзистора, а выход подключен к коллектору второго 5 выходного транзистора и связан с базой третьего 9 вспомогательного транзистора, эмиттер которого подключен ко второму 10 токостабилизирующему двухполюснику и связан с выходом устройства, причем базы первого 3 и второго 6 вспомогательных транзисторов связаны друг с другом. В схему введен дополнительный транзистор 11, база которого подключена к коллектору первого 3 вспомогательного транзистора, эмиттер соединен с базами первого 3 и второго 6 вспомогательных транзисторов, а коллектор подключен ко входу токового зеркала 8.

На фиг.3 в соответствии с п.2 формулы изобретения в схему введен транзистор терморадиационной компенсации 14.

На фиг.3 в соответствии с п.3 формулы изобретения в схему введен вспомогательный транзистор 15, эмиттер которого подключен к эмиттеру дополнительного транзистора 11, база соединена с базой дополнительного транзистора 11, а коллектор связан с шиной источника питания 16.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля Uсм в схеме фиг.2, т.е. зависящие от схемотехники ДУ.

Если токи двухполюсников 7 и 10 равны величине 2I0, то токи коллектора (Iк.i) и базы (Iб.i) транзисторов схемы:

где Iб.i=Iэ.i/βi - ток базы n-p-n (Iб.р) или p-n-p (Iб.n) транзисторов схемы при их эмиттерном токе Iэ.i=I0;

βi - коэффициент усиления по току базы транзисторов.

Входной Iвх.8 и выходной Iвых.8 токи токового зеркала 8

где Ki=1 - модуль коэффициента передачи по току токового зеркала 12.

Как следствие, разность токов в узле «А» при его коротком замыкании на эквипотенциальную общую шину

где Iб.9=2Iб.n - ток базы p-n-р транзистора 9.

Подставляя (1)÷(7) в (8), находим, что разностный ток, определяющий Uсм ДУ, равен нулю: Iр=0.

Как следствие, это уменьшает Uсм, так как разностный ток Iр в узле «А» создает Uсм, зависящее от крутизны S преобразования входного дифференциального напряжения uвх ДУ в выходной ток узла «А»:

где rэ1=rэ2=rэ4=rэ5 - сопротивления эмиттерных переходов транзисторов 1, 2, 4, 5.

Поэтому для схемы фиг.2 систематическая составляющая Uсм близка к нулю:

где φТ=26 мВ - температурный потенциал.

Введение транзистора терморадиационной компенсации 14 (фиг.3) улучшает температурную стабильность Uсм при t>80°.

Введение транзистора 15 позволяет обеспечить эффект компенсации Uсм при эмиттерных токах транзистора 9, меньших чем 2I0.

В ДУ-прототипе Iр≠0, поэтому здесь систематическая составляющая Uсм получается на три порядка больше (Uсм=2,0 мВ), чем в заявляемой схеме (Uсм=-1 мкВ).

Компьютерное моделирование схем фиг.4, 5, 6 подтверждает (фиг.7) данные теоретические выводы.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока.

Библиографический список

1. Патент ФРГ №2.930.041.

2. Патент РФ №2019019.

3. Патент РФ №1107281.

4. А.св. СССР №375754.

5. Патент США №4.030.044.

6. Патент США №4.074.205.

7. Патент США №4.286.227.

1. Комплементарный дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, коллекторы которых подключены к коллектору первого (3) вспомогательного транзистора, первый (4) и второй (5) выходные транзисторы, базы которых объединены и подключены к коллектору второго (6) вспомогательного транзистора и первому (7) токостабилизирующему двухполюснику, эмиттер первого (1) входного транзистора соединен с эмиттером первого (4) выходного транзистора, эмиттер второго (2) входного транзистора соединен с эмиттером второго (5) выходного транзистора, токовое зеркало (8), вход которого соединен с коллектором первого (4) выходного транзистора, а выход подключен к коллектору второго (5) выходного транзистора и связан с базой третьего (9) вспомогательного транзистора, эмиттер которого подключен ко второму (10) токостабилизирующему двухполюснику и связан с выходом устройства, причем базы первого (3) и второго (6) вспомогательных транзисторов связаны друг с другом, отличающийся тем, что в схему введен дополнительный транзистор (11), база которого подключена к коллектору первого (3) вспомогательного транзистора, эмиттер соединен с базами первого (3) и второго (6) вспомогательных транзисторов, а коллектор подключен ко входу токового зеркала (8).

2. Устройство по п.1, отличающееся тем, что в схему введен транзистор терморадиационной компенсации (14).

3. Устройство по п.1, отличающееся тем, что в схему введен вспомогательный транзистор (15), эмиттер которого подключен к эмиттеру дополнительного транзистора (11), база соединена с базой дополнительного транзистора (11), а коллектор связан с шиной источника питания (16).