Комплементарный дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к радиотехнике и связи для усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения (например, прецизионных операционных усилителях (ОУ)). Технический результат: уменьшение абсолютного значения Uсм и его температурного дрейфа. Усилитель содержит первый (1) и второй (2) входные транзисторы (Т), коллекторы которых объединены и подключены ко входу первого (3) токового зеркала (ТЗ), согласованного с первой (4) шиной источника питания (ИП), первый (5) и второй (6) выходные Т, базы которых объединены и соединены с первым (7) токостабилизирующим двухполюсником (ТД), эмиттер первого Т (5) соединен с эмиттером первого Т (1), эмиттер второго Т (6) соединен с эмиттером второго Т (2), коллектор первого Т (5) связан со входом второго (8) ТЗ, согласованного со второй (9) шиной ИП, коллектор второго Т (6) подключен к выходу второго (8) ТЗ и соединен с базой входного Т (10) выходного эмиттерного повторителя (11). В схему введены первый (12) и второй (13) дополнительные Т, эмиттер первого Т (12) подключен к выходу первого ТЗ (3), его коллектор соединен с объединенными базами первого Т (5) и второго Т (6), база - подключена к эмиттеру второго Т (13), причем база второго Т (13) соединена с первым ТД (7), а коллектор подключен ко входу второго ТЗ (8). 1 з.п. ф-лы, 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения (например, прецизионных операционных усилителях (ОУ)).

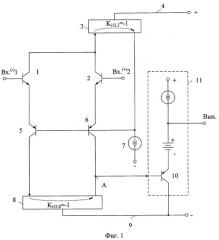

Существует несколько базовых архитектур дифференциальных усилителей (ДУ). Одна из них (фиг.1), реализованная на n-p-n и p-n-p транзисторов, относится к классической архитектуре. Впервые данная схема использована в операционном усилителе µA741. Комплементарные дифференциальные усилители (КДУ) данного класса, наряду с типовым параллельно-балансным каскадом, стали основным усилительным элементом многих аналоговых интерфейсов. Предлагаемое изобретение относится к данному подклассу устройств.

Наиболее близким по сущности к заявляемому техническому решению является схема КДУ (фиг.1), представленная в монографии Якубовского С.В., Барканова М.В., Кудряшова Б.П. Аналоговые и цифровые интегральные схемы. - М., Радио и связь, 1979. - С.224, рис.4.12а, которая также присутствует в большом числе патентов, например [1-17].

Существенный недостаток известного КДУ (фиг.1) состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм), зависящей от свойств его архитектуры.

Основная задача предлагаемого изобретения состоит в уменьшении абсолютного значения Uсм и его температурного дрейфа.

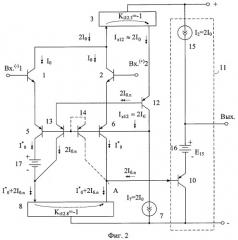

Поставленная задача достигается тем, что в комплементарном дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, коллекторы которых объединены и подключены ко входу первого 3 токового зеркала, согласованного с первой 4 шиной источника питания, первый 5 и второй 6 выходные транзисторы, базы которых объединены и соединены с первым 7 токостабилизирующим двухполюсником, эмиттер первого 5 выходного транзистора соединен с эмиттером первого 1 входного транзистора, эмиттер второго 6 выходного транзистора соединен с эмиттером второго 2 входного транзистора, коллектор первого 5 выходного транзистора связан со входом второго 8 токового зеркала, согласованного со второй 9 шиной источника питания, коллектор второго 6 выходного транзистора подключен к выходу второго 8 токового зеркала и соединен с базой входного транзистора 10 выходного эмиттерного повторителя 11, предусмотрены новые элементы и связи - в схему введены первый 12 и второй 13 дополнительные транзисторы, эмиттер первого 12 дополнительного транзистора подключен к выходу первого 3 токового зеркала, его коллектор соединен с объединенными базами первого 5 и второго 6 выходных транзисторов, база - подключена к эмиттеру второго 13 дополнительного транзистора, причем база второго 13 дополнительного транзистора соединена с первым 7 токостабилизирующим двухполюсником, а коллектор подключен ко входу второго 8 токового зеркала.

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 показано заявляемое устройство в соответствии с п.1 и п.2 формулы изобретения.

На фиг.3 показана схема фиг.2 с конкретным выполнением функциональных узлов 3, 8 и 11.

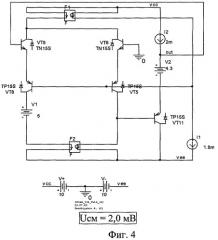

На фиг.4 и фиг.5 представлены схемы комплементарного дифференциального усилителя-прототипа (фиг.4) и заявляемого КДУ (фиг.5) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.6 приведены температурные зависимости напряжения смещения нуля схем фиг.4, фиг.5.

Комплементарный дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, коллекторы которых объединены и подключены ко входу первого 3 токового зеркала, согласованного с первой 4 шиной источника питания, первый 5 и второй 6 выходные транзисторы, базы которых объединены и соединены с первым 7 токостабилизирующим двухполюсником, эмиттер первого 5 выходного транзистора соединен с эмиттером первого 1 входного транзистора, эмиттер второго 6 выходного транзистора соединен с эмиттером второго 2 входного транзистора, коллектор первого 5 выходного транзистора связан со входом второго 8 токового зеркала, согласованного со второй 9 шиной источника питания, коллектор второго 6 выходного транзистора подключен к выходу второго 8 токового зеркала и соединен с базой входного транзистора 10 выходного эмиттерного повторителя 11. В схему введены первый 12 и второй 13 дополнительные транзисторы, эмиттер первого 12 дополнительного транзистора подключен к выходу первого 3 токового зеркала, его коллектор соединен с объединенными базами первого 5 и второго 6 выходных транзисторов, база - подключена к эмиттеру второго 13 дополнительного транзистора, причем база второго 13 дополнительного транзистора соединена с первым 7 токостабилизирующим двухполюсником, а коллектор подключен ко входу второго 8 токового зеркала.

В схеме фиг.2, в соответствии с п.2 формулы изобретения, в схему введен транзистор терморадиационной компенсации 14, коллектор которого соединен с выходом токового зеркала 8, база соединена с эмиттером и подключена к первому 7 токостабилизирующему двухполюснику. Выходной эмиттерный повторитель 11 реализован на основе двухполюсников 15, 16 и транзисторе 10.

В схеме фиг.3 двухполюсники 16 и 17 реализованы на основе резистора 17 и стабилитрона 16, а первое токовое зеркало 3 содержит p-n переход 18 и транзистор 19. Двухполюсник 15 в данной схеме реализован на транзисторе 20. Второе токовое зеркало 8 (прецизионная схема Вильсона) содержит транзисторы 21, 22 и p-n переход 23.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля Uсм в схеме фиг.2, т.е. зависящие от схемотехники ДУ.

Если токи двухполюсников 7 и 15 равны величине 2I0, то токи коллектора (Iк.i) и базы (Iб.i) транзисторов схемы:

где Iб.i=Iэ.i/βi - ток базы n-p-n (Iб.р) или p-n-p (Iб.n) транзисторов схемы при эмиттерном токе Iэ.i=I0;

βi - коэффициент усиления по току базы i-го транзистора.

Входной Iвх.8 и выходной Iвых.8 токи второго токового зеркала 8

где Кi=1 - модуль коэффициента передачи по току второго токового зеркала 8.

Как следствие, разность токов в узле «А» при его коротком замыкании на эквипотенциальную общую шину

где Iб.10=2Iб.n - ток базы p-n-p транзистора 10 выходного эмиттерного повторителя 11.

Подставляя (1) - (7) в (8) находим, что разностный ток, определяющий Uсм ДУ,

Как следствие, это уменьшает Uсм, так как разностный ток Ip в узле «А» создает напряжение Uсм, зависящее от крутизны S преобразования входного дифференциального напряжения (uвх) КДУ в выходной ток узла «А»:

где rэ1=rэ2=rэ5=rэ6 - сопротивления эмиттерных переходов транзисторов 1, 2, 5, 6.

Поэтому для схемы фиг.2

где φт=26 мВ - температурный потенциал.

В ДУ-прототипе Ip≠0, поэтому здесь систематическая составляющая Uсм получается на два-три порядка больше (Uсм=2,0 мВ), чем в заявляемой схеме (Uсм=-1 мкВ).

Компьютерное моделирование схем фиг.4, фиг.5 подтверждает (фиг.6) данные теоретические выводы.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока.

Библиографический список

1. Интегральные микросхемы. Операционные усилители [Текст]: справочник. - М., Издательский дом «Додэка-XXI», 2001. - С.90, Высоковольтный операционный усилитель 1443 УД1.

2. Патент США №4030044, fig.1.

3. Патент США №3786362, fig.1.

4. Патент США №3660773, fig.4.

5. Достал И. Операционные усилители [Текст] / И.Достал. - М., Мир, 1982. - С.79, рис.3.14в.

6. Патент США №4074205.

7. Патент США №4560948, fig.6.

8. Конелли Д. Аналоговые интегральные схемы [Текст] / Д.Конелли. - М., Мир, 1977. - С.85.

9. Патент США №4429284, fig.1.

10. Патент США №4855684, fig.4.

11. Патент ФРГ DE2633952, fig.5.

12. Патент США №4059808, fig.5.

13. Патент Японии №57-5364 H03F 3/343.

14. А.с. СССР 375754.

15. А.с. СССР 1107281.

16. А.с. СССР 1107279.

17. М.Херпи. Аналоговые интегральные схемы. - М.: Радио и связь, 1983, стр.174, рис.5.52.

1. Комплементарный дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, коллекторы которых объединены и подключены ко входу первого (3) токового зеркала, согласованного с первой (4) шиной источника питания, первый (5) и второй (6) выходные транзисторы, базы которых объединены и соединены с первым (7) токостабилизирующим двухполюсником, эмиттер первого (5) выходного транзистора соединен с эмиттером первого (1) входного транзистора, эмиттер второго (6) выходного транзистора соединен с эмиттером второго (2) входного транзистора, коллектор первого (5) выходного транзистора связан со входом второго (8) токового зеркала, согласованного со второй (9) шиной источника питания, коллектор второго (6) выходного транзистора подключен к выходу второго (8) токового зеркала и соединен с базой входного транзистора (10) выходного эмиттерного повторителя (11), отличающийся тем, что в схему введены первый (12) и второй (13) дополнительные транзисторы, эмиттер первого (12) дополнительного транзистора подключен к выходу первого (3) токового зеркала, его коллектор соединен с объединенными базами первого (5) и второго (6) выходных транзисторов, база подключена к эмиттеру второго (13) дополнительного транзистора, причем база второго (13) дополнительного транзистора соединена с первым (7) токостабилизирующим двухполюсником, а коллектор подключен ко входу второго (8) токового зеркала.

2. Устройство по п.1, отличающееся тем, что в схему введен транзистор терморадиационной компенсации (14), коллектор которого соединен с выходом токового зеркала (8), база соединена с эмиттером и подключена к первому (7) токостабилизирующему двухполюснику.