Комплементарный дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к радиотехнике и связи для усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения. Технический результат: уменьшение абсолютного значения UСМ и его температурного дрейфа. Усилитель содержит первый (1) входной параллельно-балансный каскад (ПБК) на p-n-р транзисторах (Т) и включенный параллельно ему по дифференциальному входу второй (2) входной ПБК на n-p-n T, первый (3) токостабилизирующий двухполюсник (ТД) в общей эмиттерной цепи (4) первого (1) входного ПБК, второй (5) ТД в общей эмиттерной цепи (6) второго (2) входного ПБК, первое (7) токовое зеркало (ТЗ), вход которого соединен с токовым выходом (8) второго (2) ПБК, а выход соединен с высокоимпедансным выходом (9) устройства, второе (10) ТЗ, вход которого соединен с токовым выходом (11) первого (1) ПБК, а выход соединен с высокоимпедансным выходом (9) устройства, буферный усилитель (12), вход которого соединен с высокоимпедансным выходом (9) устройства, а выход является низкоимпедансным выходом устройства. В схему введены первый (13) и второй (14) дополнительные Т, эмиттер первого Т (13) соединен с первым (3) ТД, коллектор подключен к общей эмиттерной цепи (4) первого (1) ПБК, а база через первый (15) неинвертирующий повторитель тока (ПТ) соединена со входом второго (10) ТЗ, эмиттер второго Т (14) соединен со вторым (5) ТД, коллектор соединен с общей эмиттерной цепью (6) второго (2) ПБК, а база через второй (16) неинвертирующий ПТ подключена ко входу первого (7) ТЗ. 7 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в прецизионных операционных усилителях (ОУ), компараторах и т.п.).

Известны схемы комплементарных дифференциальных усилителей (КДУ) на основе двух параллельно-включенных дифференциальных каскадов (ДК) с токостабилизирующими двухполюсниками в эмиттерных цепях входных транзисторов (так называемые «dual input stage») и выходных каскадов, выполненных на повторителях тока. КДУ с такой архитектурой стали основой построения многих современных операционных усилителей [1-15], в т.ч. ОУ с опцией rail-to-rail, имеющих максимальную амплитуду выходного напряжения, близкую к напряжению питания.

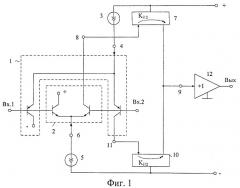

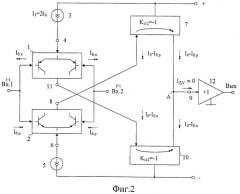

Ближайшим прототипом (фиг.1, фиг.2) заявляемого устройства является комплементарный дифференциальный усилитель, описанный в патенте США №5.291.149, fig. 3, содержащий первый 1 входной параллельно-балансный каскад на p-n-p транзисторах и включенный параллельно ему по дифференциальному входу второй 2 входной параллельно-балансный каскад на n-p-n транзисторах, первый 3 токостабилизирующий двухполюсник в общей эмиттерной цепи 4 первого 1 входного параллельно-балансного каскада на p-n-p транзисторах, второй 5 токостабилизирующий двухполюсник в общей эмиттерной цепи 6 второго 2 входного параллельно-балансного каскада на n-p-n транзисторах, первое 7 токовое зеркало, вход которого соединен с токовым выходом 8 второго 2 входного параллельно-балансного каскада на n-p-n транзисторах, а выход соединен с высокоимпедансным выходом 9 устройства, второе 10 токовое зеркало, вход которого соединен с токовым выходом 11 первого 1 входного параллельно-балансного каскада на p-n-p транзисторах, а выход соединен с высокоимпедансным выходом 9 устройства, буферный усилитель 12, вход которого соединен с высокоимпедансным выходом 9 устройства, а выход является низкоимпедансным выходом устройства.

Существенный недостаток известного ДУ (фиг.1) состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм), зависящей от свойств его архитектуры.

Основная задача предполагаемого изобретения состоит в уменьшении абсолютного значения Uсм и его температурного дрейфа.

Поставленная задача достигается тем, что в дифференциальном усилителе (фиг.1, фиг.2), содержащем первый 1 входной параллельно-балансный каскад на p-n-p транзисторах и включенный параллельно ему по дифференциальному входу второй 2 входной параллельно-балансный каскад на n-p-n транзисторах, первый 3 токостабилизирующий двухполюсник в общей эмиттерной цепи 4 первого 1 входного параллельно-балансного каскада на p-n-p транзисторах, второй 5 токостабилизирующий двухполюсник в общей эмиттерной цепи 6 второго 2 входного параллельно-балансного каскада на n-p-n транзисторах, первое 7 токовое зеркало, вход которого соединен с токовым выходом 8 второго 2 входного параллельно-балансного каскада на n-p-n транзисторах, а выход соединен с высокоимпедансным выходом 9 устройства, второе 10 токовое зеркало, вход которого соединен с токовым выходом 11 первого 1 входного параллельно-балансного каскада на p-n-p транзисторах, а выход соединен с высокоимпедансным выходом 9 устройства, буферный усилитель 12, вход которого соединен с высокоимпедансным выходом 9 устройства, а выход является низкоимпедансным выходом устройства, предусмотрены новые элементы и связи - в схему введены первый 13 и второй 14 дополнительные транзисторы, эмиттер первого 13 дополнительного транзистора соединен с первым 3 токостабилизирующим двухполюсником, коллектор подключен к общей эмиттерной цепи 4 первого 1 входного параллельно-балансного каскада на p-n-p транзисторах, а база через первый 15 неинвертирующий повторитель тока соединена со входом второго 10 токового зеркала, эмиттер второго 14 дополнительного транзистора соединен со вторым 5 токостабилизирующим двухполюсником, коллектор соединен с общей эмиттерной цепью 6 второго 2 входного параллельно-балансного каскада на n-p-n транзисторах, а база через второй 16 неинвертирующий повторитель тока подключена ко входу первого 7 токового зеркала.

Схема известного комплементарного дифференциального усилителя представлена на фиг.1. На фиг.2 показана функциональная схема КДУ фиг.1.

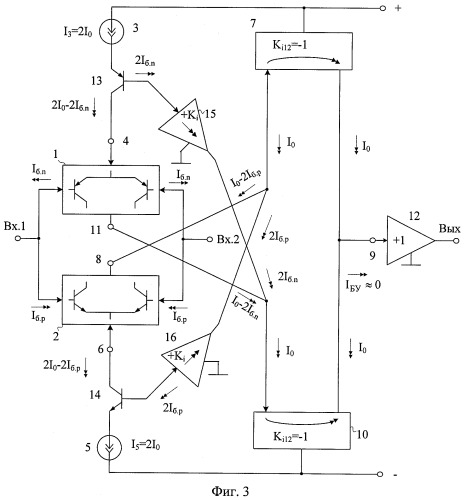

На фиг.3 представлена схема заявляемого устройства в соответствии с формулой изобретения.

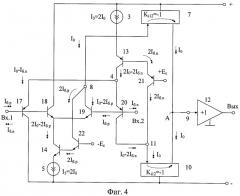

На фиг.4 показана схема заявляемого устройства фиг.3 с конкретным выполнением основных функциональных узлов 1, 2, 15 и 16. В качестве токовых зеркал 7 и 10 целесообразно использовать классические токовые зеркала Вильсона.

На фиг.5 и 6 показаны схемы дифференциального усилителя - прототипа (фиг.5) и заявляемого КДУ (фиг.6) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.7 приведены температурные зависимости напряжения смещения нуля схем фиг.5, фиг.6.

Комплементарный дифференциальный усилитель фиг.2 содержит первый 1 входной параллельно-балансный каскад на p-n-p транзисторах и включенный параллельно ему по дифференциальному входу второй 2 входной параллельно-балансный каскад на n-p-n транзисторах, первый 3 токостабилизирующий двухполюсник в общей эмиттерной цепи 4 первого 1 входного параллельно-балансного каскада на p-n-p транзисторах, второй 5 токостабилизирующий двухполюсник в общей эмиттерной цепи 6 второго 2 входного параллельно-балансного каскада на n-p-n транзисторах, первое 7 токовое зеркало, вход которого соединен с токовым выходом 8 второго 2 входного параллельно-балансного каскада на n-p-n транзисторах, а выход соединен с высокоимпедансным выходом 9 устройства, второе 10 токовое зеркало, вход которого соединен с токовым выходом 11 первого 1 входного параллельно-балансного каскада на p-n-p транзисторах, а выход соединен с высокоимпедансным выходом 9 устройства, буферный усилитель 12, вход которого соединен с высокоимпедансным выходом 9 устройства, а выход является низкоимпедансным выходом устройства. В схему введены первый 13 и второй 14 дополнительные транзисторы, эмиттер первого 13 дополнительного транзистора соединен с первым 3 токостабилизирующим двухполюсником, коллектор подключен к общей эмиттерной цепи 4 первого 1 входного параллельно-балансного каскада на p-n-p транзисторах, а база через первый 15 неинвертирующий повторитель тока соединена со входом второго 10 токового зеркала, эмиттер второго 14 дополнительного транзистора соединен со вторым 5 токостабилизирующим двухполюсником, коллектор соединен с общей эмиттерной цепью 6 второго 2 входного параллельно-балансного каскада на n-p-n транзисторах, а база через второй 16 неинвертирующий повторитель тока подключена ко входу первого 7 токового зеркала.

В качестве неинвертирующих повторителей тока 15 и 16 авторы рекомендуют использовать каскады с общей базой (транзисторы 21, 22 в КДУ фиг.4) или пассивные двухполюсники (например, стабилитроны).

Токовые зеркала 7 и 10 могут быть выполнены на основе прецизионных токовых зеркал Вильсона.

Буферный усилитель реализуется на базе классических архитектур с малыми входными токами.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля Uсм в схеме фиг.3, т.е. зависящие от схемотехники КДУ.

Если токи двухполюсников 5 и 3 равны величине 2I0, то токи коллектора (Iк.i) и базы (Iб.i) транзисторов схемы, а также токи выходов 8 и 11:

где Iб.i=Iэ.i/βi - ток базы n-p-n (Iб.р) или p-n-p (Iб.n) транзисторов схемы при их эмиттерном токе Iэ.i=I0;

βi - коэффициент усиления по току базы i-гo транзистора.

Входные (Iвх) и выходные (Iвых) токи токовых зеркал 7 и 10:

где Ki=1 - модуль коэффициента передачи по току неинвертирующих повторителей тока 15 и 16;

Кi12=1 - модуль коэффициента передачи по току токовых зеркал 7 и 10.

Как следствие, разность токов в узле «А» при его коротком замыкании на эквипотенциальную общую шину

где IБУ≈0 - входной ток буферного усилителя 12.

Подставляя (1)÷(10) в (11) находим, что разностный ток, определяющий Uсм КДУ, равен нулю: Iр=0.

Как следствие, это уменьшает Uсм, так как разностный ток Iр в узле «А» создает Uсм, зависящее от крутизны S преобразования входного дифференциального напряжения uвх ДУ в выходной ток узла «A»:

где rэ18=rэ19=rэ17=rэ20 - сопротивления эмиттерных переходов транзисторов 17, 18, 19, 20 (для КДУ фиг.4).

Поэтому для схемы фиг.3 - фиг.4 систематическая составляющая Uсм близка к нулю:

где φт=26 мВ - температурный потенциал.

В КДУ-прототипе Iр≠0, поэтому здесь систематическая составляющая Uсм получается более чем на порядок больше, чем в заявляемой схеме (фиг.7).

Компьютерное моделирование схем фиг.5, фиг.6 подтверждает (фиг.7) данные теоретические выводы.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока.

Библиографический список

1. Патент США №5.291.149 fig.3

2. Патент США №4.595.883

3. Патент США №5.225.791

4. Патент США №3.974.455

5. Патент США №4.783.637

6. А.св. СССР 611288

7. Патент Франции №2224932

8. Патент США №3.968.451

9. Патент США №5.512.859

10. Патент США №6.268.769 fig.3

11. Патент США №5.515.005

12. Патентная заявка США №2005/0024140 A1

13. Патент Японии JP 7050528

14. Патент WO 98/0091

15. Патент США №4.757.273 fig.22

Комплементарный дифференциальный усилитель, содержащий первый (1) входной параллельно-балансный каскад на p-n-р транзисторах и включенный параллельно ему по дифференциальному входу второй (2) входной параллельно-балансный каскад на n-p-n транзисторах, первый (3) токостабилизирующий двухполюсник в общей эмиттерной цепи (4) первого (1) входного параллельно-балансного каскада на р-n-р транзисторах, второй (5) токостабилизирующий двухполюсник в общей эмиттерной цепи (6) второго (2) входного параллельно-балансного каскада на n-p-n транзисторах, первое (7) токовое зеркало, вход которого соединен с токовым выходом (8) второго (2) входного параллельно-балансного каскада на n-p-n транзисторах, а выход соединен с высокоимпедансным выходом (9) устройства, второе (10) токовое зеркало, вход которого соединен с токовым выходом (11) первого (1) входного параллельно-балансного каскада на p-n-р транзисторах, а выход соединен с высокоимпедансным выходом (9) устройства, буферный усилитель (12), вход которого соединен с высокоимпедансным выходом (9) устройства, а выход является низкоимпедансным выходом устройства, отличающийся тем, что в схему введены первый (13) и второй (14) дополнительные транзисторы, эмиттер первого (13) дополнительного транзистора соединен с первым (3) токостабилизирующим двухполюсником, коллектор подключен к общей эмиттерной цепи (4) первого (1) входного параллельно-балансного каскада на p-n-р транзисторах, а база через первый (15) неинвертирующий повторитель тока соединена со входом второго (10) токового зеркала, эмиттер второго (14) дополнительного транзистора соединен со вторым (5) токостабилизирующим двухполюсником, коллектор соединен с общей эмиттерной цепью (6) второго (2) входного параллельно-балансного каскада на n-р-n транзисторах, а база через второй (16) неинвертирующий повторитель тока подключена ко входу первого (7) токового зеркала.