Предварительное декодирование инструкций переменной длины

Иллюстрации

Показать всеИзобретение относится к способу предварительного декодирования инструкций переменной длины, например, чтобы идентифицировать неопределенные инструкции. Техническим результатом является увеличение быстродействия. Способ включает: идентификацию свойства первой инструкции, причем свойство отлично от других свойств, закодированных в первом наборе битов предварительного декодирования, для которых все доступные кодирования определены либо зарезервированы; кодирование первой инструкции во втором формате, имеющем отличную длину от первого формата, включая часть первой инструкции и первый набор битов предварительного декодирования, причем второй формат содержит часть второй инструкции и второй набор битов предварительного декодирования, кодирование второго набора битов предварительного декодирования с использованием одного из доступных кодирований. 2 н. и 15 з.п. ф-лы, 4 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение, в общем, относится к области техники процессоров, а в частности, к способу предварительного декодирования инструкций переменной длины, например, чтобы идентифицировать неопределенные инструкции.

Уровень техники

Архитектуры с набором инструкций переменной длины известны в данной области техники. Например, когда расширения Thumb (16-битовые) добавляются в набор инструкций ARM (32-битовый), результирующая смесь может считаться набором инструкций переменной длины. В качестве еще одного примера, исполняемый Java-код содержит последовательность байт-кодов, причем каждая инструкция варьируется от 2 до 256 байтов по длине. В общем, наборы инструкций переменной длины содержат инструкции базового размера и более длинные инструкции, которые являются целым кратным от базового размера.

Архитектуры процессоров и наборы инструкций эволюционируют со временем. В частности, по мере того как совершенствуется полупроводниковая технология, функциональность может быть предоставлена в аппаратных средствах, которые раньше требовали объемных программных процедур для выполнения. Чтобы эффективно использовать усовершенствованные аппаратные структуры, в набор инструкций добавляются новые инструкции. Тем не менее, одним признаком стабильных процессорных архитектур является обратная совместимость. Т.е. программное обеспечение, написанное для процессорной архитектуры, должно выполняться на другом процессоре, который совместим с архитектурой, даже если он не реализует новейшую функциональность или не выполняет непосредственно новейшие инструкции. Соответственно, стандартные архитектуры процессоров включают в себя "неопределенную" инструкцию, которая формирует исключение, и функцию, ассоциативно связанную с неопределенной инструкцией, выполняется в программном обеспечении.

Один стандартный подход, предпринимаемый посредством традиционных высокопроизводительных процессоров для того, чтобы оптимизировать декодирование инструкций, - это предварительное декодирование. Предварительный декодер - это логическая схема, которая проверяет и частично декодирует инструкции, извлекаемые из памяти, до сохранения инструкций в кэше инструкций (I-кэше). Предварительный декодер формирует небольшое число битов предварительного декодирования, которые сохраняются вместе с каждой инструкцией в I-кэше. После извлечения инструкций из кэша конвейерный декодер может использовать биты предварительного декодирования для того, чтобы упростить задачу декодирования инструкций. Биты предварительного декодирования, например, могут идентифицировать инструкции ветвления, идентифицировать длину инструкции в архитектуре инструкций переменной длины и т.п. Биты предварительного декодирования также могут быть использованы для того, чтобы идентифицировать неопределенные инструкции.

В процессоре с наборами инструкций переменной длины, который реализует предварительное декодирование, небольшое число битов предварительного декодирования может быть ассоциативно связано с самой короткой, или базовой, длиной инструкции. Известная реализация кэша инструкций состоит в том, чтобы ассоциативно связать это число битов предварительного декодирования с каждой ячейкой хранения I-кэша (каждое из которых соответствует базовой длине инструкции). Более длинные инструкции, занимающие целое кратное ячеек хранения I-кэша, соответственно, ассоциативно связываются с большим числом битов предварительного декодирования. Число дискретных свойств, которые могут быть кодированы в битах предварительного декодирования, ассоциативно связанных с инструкций, тем самым является минимальным для базовой длины инструкции. Если все из доступных кодирований битов предварительного декодирования базовой длины инструкций заданы иначе, использование битов предварительного декодирования для того, чтобы идентифицировать неопределенную инструкцию базовой длины, должно потребовать увеличения числа битов предварительного декодирования, ассоциативно связанных с базовой длиной инструкции. Эта методика, в свою очередь, должна увеличивать число битов предварительного декодирования, сохраненных вместе с каждой ячейкой хранения в I-кэше. Поскольку неопределенные инструкции встречаются редко и инструкции более длинные, чем базовая длина, имеют значительное пространство кодирования битов предварительного декодирования, добавление битов предварительного декодирования для того, чтобы идентифицировать неопределенные инструкции базовой длины, может растрачивать ценное пространство хранения I-кэша.

Сущность изобретения

Согласно одному или более вариантам осуществления, описанным в данном документе, предварительный декодер может указывать свойство инструкции, когда пространство кодирования битов предварительного декодирования, ассоциативно связанных с этой длиной инструкции, полностью задано. Посредством изменения инструкции для того, чтобы имитировать инструкцию другой длины, предварительный декодер может использовать доступное кодирование битов предварительного декодирования, ассоциативно связанных с инструкцией другой длины, чтобы указать это свойство.

Один вариант осуществления относится к способу предварительного декодирования инструкции в процессоре. Свойство первой инструкции идентифицируется. Первая инструкция изменяется так, чтобы имитировать вторую инструкцию. Формируются биты предварительного декодирования для второй инструкции, которые идентифицируют свойство первой инструкции.

Другой вариант осуществления относится к процессору, выполненному с возможностью считывать инструкции из памяти. Процессор включает в себя кэш-память инструкций, сохраняющую инструкции, считываемые из памяти, и биты предварительного декодирования, ассоциативно связанные с каждой инструкцией. Процессор также включает в себя предварительный декодер, размещенный между памятью и кэшем инструкций, при этом предварительный декодер выполнен с возможностью идентифицировать свойство первой инструкции; изменять первую инструкцию так, чтобы имитировать вторую инструкцию; формировать биты предварительного декодирования для второй инструкции, которые идентифицируют свойство первой инструкции; и записывать биты предварительного декодирования для второй инструкции в кэш инструкций.

Краткое описание чертежей

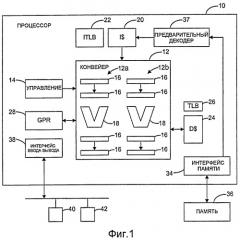

Фиг.1 - это функциональная блок-схема процессора.

Фиг.2 - это функциональная блок-схема, иллюстрирующая отображение инструкций переменной длины из памяти в кэш инструкций.

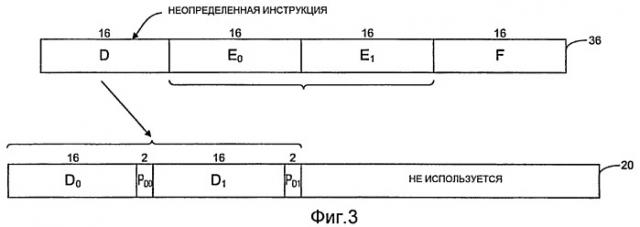

Фиг.3 - это функциональная блок-схема, иллюстрирующая отображение неопределенной инструкции из памяти в кэш инструкций.

Фиг.4 иллюстрирует способ предварительного декодирования инструкции согласно одному варианту осуществления.

Подробное описание изобретения

Фиг.1 - это функциональная блок-схема процессора 10. Процессор 10 выполняет инструкции в конвейере 12 выполнения инструкций согласно управляющей логике 14. Конвейер 12 может иметь суперскалярную структуру с несколькими параллельными конвейерами, такими как 12a и 12b. Каждый конвейер 12a, 12b включает в себя различные регистры или защелки 16, организованные в ступени конвейера, и одно или более арифметико-логических устройств (ALU) 18. Регистры или защелки 16 ступеней конвейера и ALU 18 могут считывать операнды и/или записывать результаты в регистры в файл 28 регистров общего назначения.

Конвейеры 12a, 12b извлекают инструкции из кэша 20 инструкций (I-кэша или I$), причем адресация памяти и разрешения управляются посредством буфера быстрого преобразования адреса команд (ITLB) 22. Доступ к данным осуществляется из кэша 24 данных (D-кэша или D$), причем адресация памяти и разрешения управляются посредством буфера быстрого преобразования адреса (TLB) 26. В различных вариантах осуществления ITLB 22 может содержать копию части TLB 26. Альтернативно ITLB 22 и TLB 26 могут быть интегрированы. Аналогично в различных вариантах осуществления процессора 10 I-кэш 20 и D-кэш 24 могут быть интегрированы или объединены. Промахи в I-кэше 20 и/или D-кэше 24 вызывают доступ к основной (вне микросхемы) памяти 36 под управлением интерфейса 34 памяти.

Инструкции, извлекаемые из памяти, обрабатываются в схеме 37 предварительного декодера перед кэшированием в I-кэше 20. Предварительный декодер 37 частично декодирует инструкции и присоединяет биты предварительного декодирования, которые сохраняются вместе с инструкциями в I-кэше 20. Когда инструкции извлекаются из I-кэша 20, биты предварительного декодирования предоставляют информацию о каждой инструкции, которая может быть использована посредством стадий конвейеров декодирования в конвейерах 12a и 12b для того, чтобы более быстро и/или более эффективно декодировать инструкцию. Например, биты предварительного декодирования могут идентифицировать длину инструкции в архитектуре инструкций переменной длины, идентифицировать инструкции ветвления и т.п.

Процессор 10 может включать в себя интерфейс 38 ввода/вывода (I/O), управляющий доступом к различным периферийным устройствам 40, 42. Специалисты в данной области техники должны признавать, что возможно множество вариантов процессора 10. Например, процессор 10 может включать в себя кэш второго уровня (L2) для I- и D-кэшей. Помимо этого, один или более функциональных блоков, проиллюстрированных в процессоре 10, могут быть опущены из конкретного варианта осуществления.

Фиг.2 - это функциональная блок-схема, иллюстрирующая отображение инструкций из памяти 36 в строку в I-кэш 20 посредством предварительного декодера 37, для одной иллюстративной и неограничивающей реализации. Инструкция A - это 16-битовая инструкция (базовая длина инструкции для этого примера). После извлечения инструкции A из памяти предварительный декодер 37 присоединяет два бита PA предварительного декодирования, которые сохранены вместе с инструкцией A в I-кэше 20. Инструкция B - это 32-битовая инструкция, сохраненная в памяти 36 как B0 и B1. Предварительный декодер 37 присоединяет четыре бита предварительного декодирования, сохраненные в I-кэше 20, как PB0 и PB1. Инструкция C - это 16-битовая инструкция, и она сохраняется в I-кэше 20 вместе с двумя битами PC предварительного декодирования.

Как указано посредством таблицы по фиг.2, инструкции A и C, каждая имеющая два бита предварительного декодирования, имеют пространство кодирования битов предварительного декодирования в четыре. Т.е. четыре дискретных свойства - например, длина инструкции, является ли инструкция ветвлением и т.п. - могут быть кодированы в биты предварительного декодирования для инструкций A и C. Инструкция B, имеющая четыре бита предварительного декодирования, имеет пространство кодирования битов предварительного декодирования в 16. Если поддерживается архитектурой, 48-битовая инструкция должна иметь шесть битов предварительного декодирования для пространства кодирования в 64 и т.д.

При условии, что в данной реализации все четыре кодирования битов предварительного декодирования для 16-битовых инструкций, таких как A и C, заданы, дополнительный бит предварительного декодирования может быть добавлен в каждую 16-битовую ячейку хранения в I-кэше 20, чтобы использовать биты предварительного декодирования для того, чтобы указать неопределенную 16-битовую инструкцию. Это должно привести к тому, что каждая ячейка хранения в I-кэше 20 имеет три ассоциативно связанных бита предварительного декодирования. 16-битовые инструкции в таком случае должны иметь пространство кодирования для предварительного декодирования в восемь - только пять из которых должны быть использованы. Дополнительно 32-битовые инструкции должны иметь пространство кодирования для предварительного декодирования в 64; 48-битовые инструкции должны иметь пространство кодирования для предварительного декодирования в 512. Поскольку это далеко превышает число дискретных свойств об инструкциях, которые предварительный декодер может указать, увеличение числа битов предварительного декодирования для 16-битовой длины инструкции приводит к существенному растрачиванию ценной емкости хранения I-кэша 20.

Согласно одному варианту осуществления неопределенная 16-битовая инструкция в этом примере может быть изменена так, чтобы имитировать 32-битовую инструкцию. То свойство, что инструкция фактически является 16-битовой неопределенной инструкцией, кодируется в одном из 16 кодирований для предварительного декодирования, ассоциативно связанных с 32-битовыми инструкциями. На фиг.3 инструкция D - это 16-битовая неопределенная инструкция. После записи инструкции D в I-кэш 20 она изменяется так, чтобы имитировать 32-битовую инструкцию, содержащую D0 и D1. Биты PD0 и PD1 предварительного декодирования записываются, указывая то, что инструкция D - это фактически 16-битовая неопределенная инструкция.

В одном варианте осуществления, где только факт 16-битовой неопределенной инструкции требуется для конвейера 12, предварительный декодер 37 может записывать только биты PD0 и PD1 предварительного декодирования в I-кэш 20, отбрасывая инструкцию D. В другом варианте осуществления, например, где данные в битовом поле инструкции являются стандартными или полезными для того, чтобы направлять программную ловушку, инструкция D может быть записана в D0 или D1 или и в то, и в другое, а также записывать биты PD0 и PD1 предварительного декодирования в I-кэш 20. В еще одном другом варианте осуществления предварительный декодер 37 может записывать инструкцию D в одно из D0 или D1 и может записывать дополнительную информацию в другую 16-битовую ячейку хранения I-кэша 20, а также записывать биты PD0 и PD1 предварительного декодирования. В любом случае именно биты PD0 и PD1 предварительного декодирования моделируют 32-битовую инструкцию (так, чтобы все биты предварительного декодирования считывались) и указывают то, что инструкция фактически является 16-битовой неопределенной инструкцией. Таким образом, предварительный декодер 37 может указывать неопределенную инструкцию базового размера без увеличения битов предварительного декодирования, ассоциативно связанных с инструкциями базового размера, тем самым исключая неэффективное использование памяти.

В варианте осуществления, проиллюстрированном на фиг.3, ни одна из инструкций E и F не декодируется предварительно или загружается в I-кэш 20. Поскольку фактическая длина инструкции в строке была изменена между памятью 36 и I-кэшем 20, оставшаяся часть строки кэша не может содержать все оставшиеся инструкции в соответствующих пространствах хранения (к примеру, и E, и F). Предварительный декодер 37 может помечать оставшуюся часть строки кэша как неиспользуемую или недопустимую либо может просто вставить недопустимые или неопределенные биты предварительного декодирования в соответствующие битовые позиции. При нормальном выполнении процессор захватывает в ловушку программное обеспечение при обнаружении неопределенной инструкции, и строка кэша с большой вероятностью должна быть заменена. Использование программного обработчика исключений для того, чтобы обрабатывать ловушку, вызываемую посредством неопределенной инструкции, позволяет программному обеспечению имитировать инструкции, которые не предполагались в то время, когда процессор, такой как процессор 10, закреплялся в кремнии или другом полупроводниковом материале. Если оказывается, что другой код переходит в строку кэша, он сталкивается с некорректным предварительным декодированием и/или не обнаруживает ожидаемую инструкцию, заставляя строку кэша перезагружаться или, возможно, вызывая исключение. Поскольку, как считается, неопределенные инструкции редко встречаются, влияние на производительность поврежденной строки I-кэша вследствие измененной неопределенной инструкции, моделирующей инструкцию другой длины, несущественно.

Способ, раскрытый в данном документе, не ограничен неопределенной инструкцией базовой длины инструкции, как описано выше. В общем, для любого свойства инструкции, которое может обычно быть указано посредством битов предварительного декодирования, но где пространство кодирования битов предварительного декодирования для ассоциативно связанной длины инструкции полностью задано, свойство может быть указано посредством изменения инструкции так, чтобы имитировать инструкцию другой длины, и использования доступного кодирования битов предварительного декодирования для инструкций другой длины. Например, допустим, что все 16 кодирований четырех битов предварительного декодирования, ассоциативно связанных с 32-битовыми инструкциями в предыдущем примере, заданы, но только задано три или меньше из четырех кодирований двух битов предварительного декодирования, ассоциативно связанных с 16-битовыми инструкциями. В этом случае конкретное свойство 32-битовой инструкции, не заданное в битах предварительного декодирования 32-битовых инструкций, может быть указано посредством изменения 32-битовой инструкции так, чтобы имитировать 16-битовую инструкцию, и кодирования релевантного свойства в доступном кодировании битов предварительного декодирования двух битов предварительного декодирования, ассоциативно связанных с 16-битовыми инструкциями. В этом случае половина битового поля 32-битовой инструкции теряется, так что кодируемое свойство - это предпочтительно такое свойство, которое не зависит от битового поля инструкции (к примеру, тот факт, что инструкция является неопределенной, хотя это не единственное свойство, которое может быть указано таким образом).

Фиг.4 иллюстрирует способ предварительного декодирования инструкции согласно одному варианту осуществления. При промахе в I-кэше 20 интерфейс 34 памяти извлекает, по меньшей мере, первую инструкцию из памяти 36 (этап 50). Предварительный декодер 37 проверяет первую инструкцию и идентифицирует свойство первой инструкции (этап 52), к примеру то, что первая инструкция является неопределенной. Предварительный декодер 37 изменяет первую инструкцию, чтобы имитировать вторую инструкцию (этап 54), например вторую инструкцию другой длины. Предварительный декодер 37 дополнительно формирует биты предварительного декодирования для второй инструкции, которые идентифицируют свойство первой инструкции (этап 56). Т.е. одно из доступных кодирований битов предварительного декодирования, ассоциативно связанных с длиной второй инструкции, назначается релевантному свойству первой инструкции. Предварительный декодер 37 записывает вторую инструкцию и ассоциативно связанные биты предварительного декодирования в I-кэш 20 (этап 58). Когда конвейер 12 извлекает вторую инструкцию и ее биты предварительного декодирования из I-кэша 20, логика в стадии декодирования конвейера проверяет биты предварительного декодирования, чтобы идентифицировать свойство первой инструкции (этап 60), к примеру то, что первая инструкция является неопределенной. Затем конвейер 12 выполняет соответствующее действие, такое как, к примеру, инструктирование прерыванию обрабатывать неопределенную инструкцию в программном обеспечении.

Согласно одному или более вариантов осуществления, описанных в данном документе, предварительный декодер 37 может указывать свойство инструкции, когда пространство кодирования битов предварительного декодирования, ассоциативно связанных с этой длиной инструкции, полностью задано. Посредством изменения инструкции для того, чтобы имитировать инструкцию другой длины, предварительный декодер 37 может использовать доступное кодирование битов предварительного декодирования, ассоциативно связанных с инструкцией другой длины, чтобы указать это свойство. Когда свойство более короткой инструкции указано в кодированиях битов предварительного декодирования более длинной инструкции, одна или более инструкций или частей инструкций должна быть вытеснена из строки I-кэша. Когда свойство более длинной инструкции указано в кодированиях битов предварительного декодирования более короткой инструкции, часть битового поля инструкции теряется. Соответственно, методика указания свойств инструкций, раскрытая в данном документе, обычно используется для того, чтобы указывать вызывающие исключения свойства инструкций, такие как то, что инструкция является неопределенной, хотя это не ограничено таким случаями.

Хотя настоящее изобретение описано в отношении конкретных признаков, аспектов и вариантов осуществления, должно быть очевидно, что множество вариаций, модификаций и других вариантов осуществления возможно в рамках широкой области применения настоящего изобретения, и соответственно, все вариации, модификации и варианты осуществления должны рассматриваться как находящиеся в рамках области применения изобретения. Следовательно, настоящие варианты осуществления должны рассматриваться во всех аспектах как иллюстративные, а не ограничивающие, и все изменения, попадающие в рамки смысла и эквивалентности прилагаемой формулы изобретения, должны охватываться ей.

1. Способ предварительного декодирования инструкции в процессоре, содержащий этапы, на которых:идентифицируют свойство первой инструкции, причем свойство отлично от других свойств, закодированных в первом наборе битов предварительного декодирования, для которых все доступные кодирования определены либо зарезервированы;кодируют первую инструкцию во втором формате, имеющем отличную длину от первого формата, включая часть первой инструкции и первый набор битов предварительного декодирования, причем второй формат содержит часть второй инструкции и второй набор битов предварительного декодирования, для которых все доступные кодирования второго набора битов предварительного декодирования не определены или не зарезервированы;кодируют второй набор битов предварительного декодирования с использованием одного из доступных кодирований, не определенных или не зарезервированных во втором наборе битов предварительного декодирования для идентификации свойства первой инструкции; изаписывают в местоположение хранения первую инструкцию, закодированную во втором формате, включая закодированный второй набор битов предварительного декодирования вместо первой инструкции, закодированной в первом формате.

2. Способ по п.1, в котором первая инструкция во втором формате вызывает исключение.

3. Способ по п.2, в котором первая инструкция является неопределенной.

4. Способ по п.1, в котором набор инструкций процессора - это набор инструкций переменой длины, и в котором инструкции первого формата и инструкции второго формата могут быть сохранены совместно в местоположении хранения.

5. Способ по п.1, в котором размер местоположения хранения изменяется в ответ на запись первой инструкции, закодированной во втором формате.

6. Способ по п.1, в котором первый формат длиннее второго формата.

7. Способ по п.1, в котором второй формат длиннее первого формата.

8. Способ по п.1, в котором первый формат имеет 18 бит, включающих в себя 16-битовый участок с инструкцией и два бита предварительного декодирования, ассоциативно связанные с ней.

9. Способ по п.8, в котором второй формат имеет 36 бит, включающих в себя 32-битовый участок с инструкцией и четыре бита предварительного декодирования, ассоциативно связанные с ней.

10. Способ по п.9, в котором одно из шестнадцати кодирований битов предварительного декодирования, ассоциативно связанных с 32-битовыми инструкциями, идентифицирует ассоциативно связанную 32-битовую инструкцию как 16-битовую неопределенную инструкцию.

11. Процессор, выполненный с возможностью считывать инструкции из памяти, содержащий:предварительный декодер, размещенный между памятью и кэшем инструкций, при этом предварительный декодер выполнен с возможностьюидентифицировать свойство первой инструкции, считанной из памяти, причем свойство отличается от других свойств, закодированных в первом наборе битов предварительного декодирования, для которых все доступные кодирования определены либо зарезервированы;кодировать первую инструкцию во втором формате, имеющем отличную длину от первого формата, включая часть первой инструкции и первый набор битов предварительного декодирования, причем второй формат содержит часть второй инструкции и второй набор битов предварительного декодирования, для которых все доступные кодирования второго набора битов предварительного декодирования не определены или не зарезервированы;кодировать второй набор битов предварительного декодирования с использованием одного из доступных кодирований, не определенных или не зарезервированных во втором наборе битов предварительного декодирования для идентификации свойства первой инструкции; изаписывать первую инструкцию, закодированную во втором формате, включая закодированный второй набор битов предварительного декодирования, в кэш инструкций.

12. Процессор по п.11, в котором инструкции, считываемые из памяти, принадлежат набору инструкций переменной длины.

13. Процессор по п.12, в котором кэш инструкций содержит множество ячеек хранения инструкций, соответствующих длине самой короткой инструкции, и в котором предопределенное число битов предварительного кодирования ассоциативно связывается с каждой ячейкой хранения.

14. Процессор по п.13, в котором кэш инструкций сохраняет инструкции, более длинные, чем самая короткая инструкция, в целом кратные ячейкам хранения, и ассоциативно связывает с каждой инструкцией биты предварительного декодирования, ассоциативно связанные с каждой ячейкой хранения.

15. Процессор по п.11, в котором первый формат имеет 18 бит, включающих в себя 16-битовый участок с инструкцией и два бита предварительного декодирования, ассоциативно связанные с ней.

16. Процессор по п.11, в котором второй формат имеет 36 бит, включающих в себя 32-битовый участок с инструкцией и четыре бита предварительного декодирования, ассоциативно связанные с ней.

17. Процессор по п.16, в котором одно из шестнадцати кодирований битов предварительного декодирования, ассоциативно связанных с 32-битовыми инструкциями, идентифицирует ассоциативно связанную 32-битовую инструкцию как 16-битовую неопределенную инструкцию.