Графическая система с конфигурируемыми кэшами

Иллюстрации

Показать всеИзобретение относится к графическим системам. Технический результат заключается в повышении производительности. Такой результат достигается благодаря тому, что система кэш-памяти дополнительно включает в себя блок управления, который определяет использование памяти процессорными блоками и назначает конфигурируемые кэши процессорным блокам на основе коэффициента использования памяти. 5 н. и 27 з.п. ф-лы, 7 ил., 1 табл.

Реферат

Уровень техники

I. Область техники

Изобретение в целом относится к схемам, более конкретно к графической системе.

II. Уровень техники

Графические системы широко используются для того, чтобы воспроизводить 2-мерные (2D) и 3-мерные (3D) изображения для различных приложений, таких как видеоигры, графика, системы автоматизированного проектирования (CAD), инструментальные средства моделирования и визуализации, создание изображений и т.д. 3D-изображение может моделироваться с помощью поверхностей, и каждая поверхность может быть аппроксимирована с помощью полигонов (многоугольников) (в типичном варианте треугольников). Число треугольников, используемых для того, чтобы представить 3D-изображение, зависит от сложности поверхностей, так же как и от желаемого разрешения изображения и может быть довольно большим, например исчисляться миллионами. Каждый треугольник определен тремя вершинами, и каждая вершина ассоциативно связана с различными атрибутами, такими как пространственные координаты, значения цвета и координаты текстуры. Каждый атрибут может иметь до четырех компонентов. Например, пространственные координаты в типичном варианте заданы горизонтальной и вертикальной координатами (x и y) и глубиной (z), значения цвета в типичном варианте заданы красным, зеленым и синим (r, g, b), а координаты текстуры в типичном варианте заданы горизонтальной и вертикальной координатами (u и v).

Графический процессор в графической системе может выполнять различные графические операции, чтобы визуализировать 2D- и 3D-изображение. Изображение состоит из множества треугольников, и каждый треугольник состоит из элементов изображения (пикселей). Графический процессор визуализирует каждый треугольник, определяя значения компонентов каждого пикселя внутри треугольника. Графические операции включают в себя растеризацию, тесты трафарета и глубины, наложение текстуры, затенение и т.д. Так как графический процессор выполняет различные графические операции по пиксельным данным, которые могут быть любыми данными, ассоциативно связанными с пикселями, возможность быстрого доступа к пиксельным данным имеет большое влияние на производительность.

Сущность изобретения

Графические системы с конфигурируемыми кэшами, имеющие хорошую производительность, описываются в данном документе. Графическая система включает в себя графический процессор и систему кэш-памяти. Графический процессор включает в себя процессорные блоки, которые выполняют различные графические операции, чтобы визуализировать графические изображения. Система кэш-памяти может включать в себя полностью конфигурируемые кэши, частично конфигурируемые кэши или комбинацию конфигурируемых и специализированных кэшей. Кэш является полностью конфигурируемым, если он может быть назначен любому из процессорных блоков, которым могут быть назначены кэши. Кэш является частично конфигурируемым, если он может быть назначен любому из поднабора процессорных блоков. Кэш является специализированным, если он назначен конкретному процессорному блоку. Кэши являются быстрыми запоминающими устройствами, которые хранят данные (например, пиксельные данные и/или инструкции) для процессорных блоков.

Система кэш-памяти может дополнительно включать в себя блок управления, коммутатор и схему разрешения конфликтов. Блок управления может определять использование памяти процессорными блоками и назначать конфигурируемые кэши процессорным блокам на основе коэффициента использования памяти. Конфигурируемые кэши могут быть назначены, чтобы достичь хорошего использования этих кэшей и избежать узкого места при обращении к памяти в любой момент в графическом процессоре. Коммутатор связывает процессорные блоки с их назначенными кэшами. Схема разрешения конфликтов облегчает обмены данными между кэшами и основной памятью.

Далее подробно описаны различные аспекты и варианты осуществления изобретения.

Краткое описание чертежей

Признаки и природа настоящего изобретения станут более очевидными из изложенного ниже подробного описания, рассматриваемого вместе с чертежами, на которых одинаковые символы ссылок идентифицируют соответственно по всему документу.

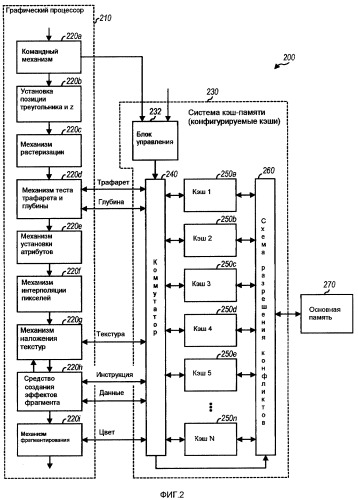

Фиг.1 показывает графическую систему со специализированными кэшами.

Фиг.2 показывает графическую систему с полностью конфигурируемыми кэшами.

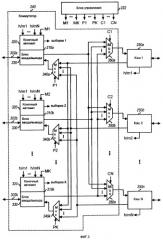

Фиг.3 показывает коммутатор в графической системе на фиг.2.

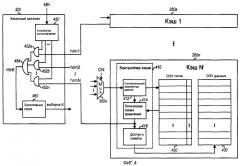

Фиг.4 показывает кэш и конечный автомат для процессорного блока.

Фиг.5 показывает графическую систему с конфигурируемыми и специализированными кэшами.

Фиг.6 показывает процесс работы графической системы с конфигурируемыми кэшами.

Фиг.7 показывает беспроводное устройство в системе беспроводной связи.

Подробное описание

Слово "примерный" используется в данном документе, чтобы обозначать "служащий в качестве примера, отдельного случая или иллюстрации". Любой вариант осуществления или структура, описанные в данном документе как "примерные", не обязательно должны быть истолкованы как предпочтительные или выгодные по сравнению с другими вариантами осуществления или структурами.

Фиг.1 показывает блок-схему графической системы 100 со специализированными кэшами. Графическая система 100 включает в себя графический процессор 110 и систему 130 кэш-памяти. Графический процессор 110 включает в себя различные процессорные блоки, размещенные в конвейере и используемые, чтобы визуализировать 2D- и 3D-изображения. Командный механизм 120a принимает и декодирует входящие команды, которые определяют графические операции, которые должны быть выполнены. Механизм 120b установки позиции треугольника и координаты z вычисляет необходимые параметры для последующего процесса растеризации. Например, механизм 120b может вычислить коэффициенты линейных уравнений для трех ребер каждого треугольника, коэффициенты для глубины (z), градиента и т.д. Механизм 120c растеризации раскладывает каждый треугольник или линию на пиксели и формирует экранную координату для каждого пикселя.

Механизм 120d теста трафарета и глубины выполняет тест трафарета (шаблона) по каждому пикселю, если позволено, чтобы определить, должен ли пиксель быть отображен или отброшен. Трафаретный буфер (не показан на фиг.1) хранит текущее значение трафарета для каждого пикселя в визуализируемом изображении. Механизм 120d сравнивает сохраненное значение трафарета для каждого пикселя с контрольным значением и сохраняет или отбрасывает пиксель на основе результата сравнения. Механизм 120d также выполняет тест глубины (который также называется z-тест) по каждому пикселю, если применимо, чтобы определить, должен ли пиксель быть отображен или отброшен. Z-буфер (не показан на фиг.1) хранит текущее z-значение для каждого пикселя в визуализируемом изображении. Механизм 120d сравнивает z-значение каждого пикселя (текущее z-значение) с соответствующим z-значением в z-буфере (сохраненным z-значением), отображает пиксель и обновляет z-буфер и, возможно, трафаретный буфер, если текущее z-значение ближе, чем сохраненное z-значение, и отбрасывает пиксель, если текущее z-значение дальше, чем сохраненное z-значение.

Механизм 120c установки атрибутов вычисляет необходимые параметры для последующей интерполяции атрибутов пикселя. Например, механизм 120c может вычислить коэффициенты линейных уравнений для интерполяции атрибутов. Механизм 120f интерполяции пикселей вычисляет значения компонентов атрибутов для каждого пикселя в треугольнике на основе экранной координаты пикселя и с помощью информации из механизма 120e. Механизм 120g наложения текстур выполняет наложение текстуры, если это разрешено, чтобы применить текстуру к каждому треугольнику. Изображение текстуры может быть сохранено в буфере текстур (не показан на фиг.1). Три вершины каждого треугольника могут быть ассоциативно связаны с тремя (u, v) координатами в изображении текстур, и каждый пиксель треугольника может затем быть ассоциативно связан с конкретными координатами текстуры в изображении текстуры. Текстурирование достигается посредством модификации каждого пикселя с помощью цвета изображения текстуры в местоположении, указанном координатами текстуры этого пикселя.

Каждый пиксель ассоциативно связан с информацией, такой как цвет, глубина, текстура и т.д. Фрагментом является пиксель и ассоциативно связанная с ним информация. Средство 120h создания эффектов фрагмента применяет программу системы программного обеспечения, которая может быть составлена из последовательности инструкций, к каждому фрагменту. Средство 120h создания эффектов фрагмента может также отправлять запросы текстур механизму 120g наложения текстур. Механизм 120i фрагментирования выполняет функции, такие как альфа-тест, смешивание с туманом, альфа-смешивание, логическая операция и операция имитации градаций серого, по каждому фрагменту и предоставляет результаты в цветовой буфер.

Графические операции, показанные на фиг.1, известны в данной области техники. Графический процессор может осуществлять программный интерфейс, такой как открытая графическая библиотека (OpenGL), Direct3D и т.д. OpenGL описывается в документе, озаглавленном "The OpenGL® Graphics System: A Specification", версия 2.0, датированном 22 октября 2004 года, который открыто доступен.

Вообще, графический процессор может включать в себя любое число процессорных блоков для любого набора графических операций. Каждый процессорный блок может быть механизмом, который реализован с помощью специализированных аппаратных средств, процессора или комбинации обоих. Например, механизмы, показанные на фиг.1, могут быть реализованы с помощью специализированных аппаратных средств, тогда как механизм создания эффектов фрагмента может быть реализован с помощью программируемого центрального процессора (CPU). Процессорные блоки могут быть размещены в различных порядках в зависимости от желаемой оптимизации. Например, чтобы сберечь энергию, может быть желательно выполнить тесты трафарета и глубины заблаговременно на конвейере, так что пиксели, которые не видны, отбрасываются заранее, как показано на фиг.1. Процессорные блоки могут также быть размещены в других порядках, например механизм 120d теста трафарета и глубины может быть расположен после механизма 120g наложения текстур.

Система 130 кэш-памяти включает в себя специализированные кэши 150a-150f для некоторых из процессорных блоков 120 в графическом процессоре 110. В конструкции, показанной на фиг.1, кэш 150a трафарета хранит значения трафарета (шаблона) для пикселей в области воспроизводимого изображения, а кэш 150b глубины хранит значения глубины для пикселей в той же или другой области. Механизм 120d теста трафарета и глубины обращается к значениям трафарета, сохраненным в кэше 150a, и выполняет тесты трафарета с помощью этих значений трафарета. Механизм 120d также обращается к z-значениям, сохраненным в кэше 150b, и выполняет тесты глубины с помощью этих z-значений. Кэш 150c текстур хранит таблицу наложения текстур, которая используется механизмом 120g наложения текстур, чтобы наложить текстуру на треугольники. Кэш 150d инструкций механизма создания эффектов хранит инструкции для средства 120h создания эффектов фрагмента, а кэш 150e данных механизма создания эффектов хранит данные для средства 120h создания эффектов фрагмента. Кэш 150f цвета хранит значения цвета (например, красного, зеленого и синего) для пикселей.

Схема 160 разрешения конфликтов связывается и облегчает обмены данными между кэшами 150a-150f и основной памятью 170. Неудачное обращение в кэш признается всякий раз, когда процессорный блок 120 обращается в ассоциативно связанный кэш 150 за данными, а запрошенные данные не сохранены в кэше. Результаты неудачного обращения в кэш в текущем содержимом кэша сохраняются обратно в основную память 170, если необходимо, и новая область данных выбирается из основной памяти 170 и загружается в кэш. Запрошенные данные могут затем быть получены из кэша и предоставлены процессорному блоку. Схема 160 разрешения конфликтов позволяет одному кэшу в момент времени обмениваться данными с основной памятью 170.

Система 130 кэш-памяти на фиг.1 улучшает производительность обращения к памяти для графической системы 100. Кэши 150 являются небольшими, быстрыми запоминающими устройствами, расположенными близко к графическому процессору 110. Быстрая кэш-память улучшает скорость обработки, так как процессорные блоки 120 могут извлекать данные и сохранять результаты быстрее. Основная память 170 является большой, более медленной памятью, расположенной дальше (например, вне микросхемы) от графического процессора 110. Основная память 170 хранит данные и инструкции, которые могут быть загружены в кэши 150. Кэши 150 уменьшают число выборок из основной памяти 170 и в целом улучшают производительность графической системы 100.

Фиг.1 показывает использование специализированных кэшей. Каждый кэш 150 хранит данные или инструкции для конкретного процессорного блока 120. Использование каждого кэша 150 зависит от выполняемого графического приложения. Например, приложение 3D-графики может выполнять только z-проход, который может включать только тест глубины и/или трафарета (шаблона). Для этого приложения может использоваться только трафаретный кэш 150a и/или кэш 150b глубины, а оставшиеся кэши 150c-150f могут быть свободны. В качестве другого примера, простое приложение создания эффектов может не использовать кэш 150d инструкций механизма создания эффектов или кэш 150e данных механизма создания эффектов, и эти кэши могут быть свободны. В качестве еще одного примера, графическое приложение может отключить наложение текстур, в таком случае кэш 150c текстур может быть не нужен. Как видно посредством этих примеров, использование специализированных кэшей может приводить в результате к плохому коэффициенту использования кэшей некоторыми графическими приложениями. Использование специализированных кэшей может также при обращении к памяти приводить в результате к узкому месту, возникающему в разных местах для разных графических приложений. Узкое место ограничивает производительность графической системы 100.

Фиг.2 показывает вариант осуществления графической системы 200 с полностью конфигурируемыми кэшами. Графическая система 200 включает в себя графический процессор 210 и систему 230 кэш-памяти. Графический процессор 210 включает в себя процессорные блоки 220a-220i, которые могут работать, как описано выше для процессорных блоков 120a-120i соответственно на фиг.1. Как показано на фиг.2, только некоторые из процессорных блоков могут использовать кэши, чтобы хранить данные и/или инструкции. В частности, кэши могут использоваться, чтобы хранить значения трафарета и/или значения глубины для механизма 220d теста трафарета и глубины, данные текстуры для механизма 220g наложения текстур, инструкции и/или данные для средства 220h создания эффектов фрагмента и цветовые значения для механизма 220i фрагментирования.

Система 230 кэш-памяти включает в себя N полностью конфигурируемых кэшей 250a-250n, которые могут быть предназначены для хранения данных и/или инструкций для процессорных блоков 220 в графическом процессоре 210, где, как правило, N>1. Кэши являются полностью конфигурируемыми в том, что каждый кэш может быть выделен для любого процессорного блока, которому могут быть назначены кэши. В варианте осуществления каждый кэш 250 может быть назначен только одному процессорному блоку 220, но данному процессорному блоку 220 может быть назначено ноль, один или множество кэшей 250. Блок 232 управления назначает доступные кэши 250a-250n механизму 220d теста трафарета и глубины, механизму 220g наложения текстур, средству 220h создания эффектов фрагмента и/или механизму 220i фрагментирования на основе коэффициента использования памяти этими процессорными блоками. Коммутатор 240 связывает процессорные блоки 220d, 220g, 220h и 220i с их назначенными кэшами 250a-250n. Коммутатор 240 также может называться перекрестным переключателем или некоторой другой терминологией. Схема 260 разрешения конфликтов связывает кэши 250a-250n с основной памятью 270 и облегчает обмены данными между кэшами и основной памятью. Схема 260 разрешения конфликтов также может называться селектором, интерфейсом памяти или некой другой терминологией.

Как правило, система кэш-памяти может включать в себя любое число кэшей, которые могут быть любого размера. Число кэшей и их размеры могут выбираться на основе компромисса между производительностью обращения к памяти и площадью схемы. Более крупные размеры кэшей ведут к более высоким коэффициентам попаданий и большей вероятности того, что запрошенные данные сохранены в кэшах. Однако более объемные размеры кэшей также требуют больше площади схемы, что может увеличить стоимость. В одном конкретном варианте осуществления система 230 кэш-памяти включает в себя двенадцать кэшей 250, и каждый кэш равен четырем килобайтам. В других вариантах осуществления меньше кэшей или добавочные кэши, так же как и другие размеры кэшей, могут использоваться для системы кэш-памяти.

Фиг.3 показывает блок-схему варианта осуществления коммутатора 240 на фиг.2. В этом варианте осуществления коммутатор 240 включает в себя K интерфейсных блоков 310a-310k, где, как правило, K может быть любым целым числом. Интерфейсные блоки могут также называться главными блоками или некоторой другой терминологией. В варианте осуществления, показанном на фиг.2, K равно шести, и шесть интерфейсных блоков существуют для трафарета, глубины, текстуры, инструкции средства создания эффектов, данных механизма создания эффектов и цвета. Данный процессорный блок 220 может взаимодействовать с одним или более интерфейсными блоками 310 в зависимости от требований данных процессорного блока. Коммутатор 240 дополнительно включает в себя K мультиплексоров (Mux) 340a-340k для K интерфейсных блоков 310a-310k соответственно и N мультиплексоров 350a-350n для N кэшей 250a-250n соответственно.

Каждый интерфейсный блок 310 связывается с ассоциативно связанным процессорным блоком 220 через соответствующий набор линий 302 связи. Каждый интерфейсный блок 310 включает в себя конечный автомат 320 и блок 330 ввода/вывода (I/O). Для каждого интерфейсного блока 310 I/O-блок 330 принимает адрес и/или выходные данные от ассоциативно связанного процессорного блока 220 через линии 302 связи и выдает адрес/данные на один вход каждого из N мультиплексоров 350a-350n. I/O-блок 330 также принимает входные данные или инструкции от ассоциативно связанного мультиплексора 340 и выдает данные/инструкции ассоциативно связанному процессорному блоку 220 через линии 302 связи.

Каждый мультиплексор 350 принимает адрес/данные от всех K I/O-блоков 330a-330k на K входах. Каждый мультиплексор 350 также принимает соответствующий управляющий сигнал Cn от блока 232 управления и выдает адрес/данные с одного входа, как определено управляющим сигналом Cn, ассоциативно связанному кэшу 250. Каждый мультиплексор 350, таким образом, связывает один интерфейсный блок 310 с ассоциативно связанным кэшем 250.

Каждый мультиплексор 340 принимает входные данные или инструкции из всех N кэшей 250a-250n на N входах. Каждый мультиплексор 340 также принимает соответствующий управляющий сигнал Pk от блока 232 управления и выдает данные/инструкции с одного входа, как определено управляющим сигналом Pk, ассоциативно связанному I/O-блоку 330. Каждый мультиплексор 340, таким образом, связывает один кэш 250 с ассоциативно связанным интерфейсным блоком 310.

Каждый кэш 250 принимает адрес от ассоциативно связанного мультиплексора 350 и определяет, сохранены ли в кэше запрошенные данные/инструкции по этому адресу. Каждый кэш 250 выдает индикатор попадания/промаха (h/m), который указывает попадание в кэш (например, высокий логический уровень), если запрошенные данные/инструкция сохранены в кэше, или промах в кэше (например, низкий логический уровень), если запрошенные данные/инструкция не сохранены в кэше. Каждый кэш 250 выдает запрошенные данные/инструкцию, если существует попадание в кэш. Каждый кэш 250 ожидает выборку из основной памяти 270 и затем выдает запрошенные данные/инструкцию, если они отсутствуют в кэше.

Для каждого интерфейсного блока 310 конечный автомат 320 принимает индикаторы попадания/промаха из всех N кэшей 250a-250n и управляющий сигнал Mk, который указывает, какие кэши, если есть в наличии, были назначены этому интерфейсному блоку. Конечный автомат 320 определяет, сохранены ли запрошенные данные/инструкция в каком-либо из назначенных кэшей, на основе индикаторов попадания/промаха для назначенных кэшей. Конечный автомат 320 формирует команду выборки, если запрошенные данные/инструкция не сохранены в каком-либо из назначенных кэшей.

Блок 232 управления формирует управляющие сигналы M1-MK для конечных автоматов 320a-320k соответственно, управляющие сигналы P1-PK для мультиплексоров 340a-340k соответственно и управляющие сигналы C1-CN для мультиплексоров 350a-350n соответственно. Эти управляющие сигналы определяют, какие кэши, если есть в наличии, назначены каждому интерфейсному блоку 310.

Фиг.3 показывает вариант осуществления коммутатора 240 для полностью конфигурируемых кэшей. Как правило, полная конфигурируемость кэшей может быть достигнута посредством использования мультиплексоров с достаточным числом входов, проектирования конечных автоматов, чтобы оценить любое возможное назначение кэша, и формирования правильных управляющих сигналов для конечных автоматов и мультиплексоров. Коммутатор 240 может также быть осуществлен с помощью других схем, которые могут установить соответствие процессорных блоков с доступными кэшами.

Фиг.4 показывает блок-схему варианта осуществления кэша 250n и конечного автомата 320 для интерфейсного блока 310k на фиг.3. Кэш 250n включает в себя контроллер 410 кэша, ОЗУ 420 тегов и ОЗУ 430 данных. Контроллер 410 кэша выполняет проверку адреса для каждого обращения к кэшу 250n и гарантирует, что доступ осуществляется к корректным данным/инструкции. ОЗУ 420 тегов хранит путь, по которому данные/инструкции в настоящее время хранятся в кэше 250n. ОЗУ 430 данных хранит данные/инструкции. Каждая строка ОЗУ 430 данных может хранить данные для одного или более пикселей или одной или более инструкций в зависимости от того, сконфигурирован ли кэш 250n хранить данные или инструкции.

Кэш 250n может быть осуществлен со структурой кэша с прямым соответствием или со структурой кэша с М-образно установленной ассоциативной связью. Для структуры кэша с прямым соответствием каждая строка памяти на следующем уровне (например, основной памяти 270) может быть сопоставлена только с одной строкой ОЗУ 430 данных. Каждая строка ОЗУ 430 данных (или каждая строка кэша) ассоциативно связана с тегом в ОЗУ 420 тегов, которое идентифицирует конкретную строку основной памяти 270, сохраненную в этой строке кэша. В качестве примера, если основная память 270 имеет 256k строк, а ОЗУ 430 данных имеет 4k строк, тогда каждая строка кэша ассоциативно связывается с конкретным 12-битным адресом и 32 строки основной памяти 270 устанавливаются в соответствие с каждой строкой кэша. Конкретная строка основной памяти 270, хранящаяся в каждой строке кэша, может быть затем идентифицирована по 12-битному адресу для строки кэша и 5-битному тегу, который указывает, какая из 32 строк основной памяти 270 сохранена в строке кэша. Для структуры кэша с M-образно установленной ассоциативной связью каждая строка основной памяти 270 может быть сопоставлена с любой из M возможных линий ОЗУ 430 данных. Как правило, структура тега может зависеть от размера основной памяти, размера кэша, структуры кэша, размера каждой строки кэша и/или других факторов.

ОЗУ 420 тегов хранит тег для каждой строки ОЗУ 430 данных и обновляется всякий раз, когда любая строка в ОЗУ 430 данных заменяется. Тег для каждой строки кэша указывает строку основной памяти 270, хранящейся в этой строке кэша. В блоке 410 управления синтаксический анализатор 412 адреса принимает от мультиплексора 350n адрес для обращения к памяти процессорным блоком 220, делает синтаксический анализ (разбор) адреса, чтобы получить целевой тег и адрес строки кэша, выдает адрес строки кэша в ОЗУ 420 тегов и выдает целевой тег логической схеме 414 сравнения. ОЗУ 420 тегов предоставляет сохраненный тег для адреса строки кэша из синтаксического анализатора 412. Логическая схема 414 сравнения сравнивает сохраненный тег с целевым тегом, указывает попадание в кэш, если теги эквивалентны, и указывает промах в кэше, если теги разные. Доступ к ОЗУ 420 тегов может быть осуществлен множество раз, если кэш 250n осуществляет структуру кэша с M-образно установленной ассоциативной связью.

Блок 416 доступа к памяти управляет доступом к ОЗУ 430 данных, когда существует попадание в кэш. Если доступом к памяти является чтение, тогда осуществляется доступ в ОЗУ 430 данных, чтобы прочитать данные/инструкцию, сохраненную по адресу строки кэша. Если доступом в память является запись, тогда ОЗУ 430 данных записывается по адресу строки кэша и "грязный бит" кэша обновляется, чтобы указать, что строка кэша была записана, так что стока будет записана обратно в основную память 270 перед заменой.

Конечный автомат 320 для блока 310k интерфейса определяет, сохранены ли запрошенные данные/инструкция в каком-либо кэше, назначенном этому интерфейсному блоку. В конечном автомате 320 устройство 450 сопоставления принимает управляющий сигнал MK от блока 232 управления и формирует N разрешающих сигналов для N кэшей 250a-250n. Каждый разрешающий сигнал устанавливается в высокий логический уровень, если ассоциативно связанный кэш 250 назначается интерфейсному блоку 310k. N логических элементов 452a-452n И принимают N разрешающих сигналов и N индикаторов попадания/промаха от N кэшей 250a-250n соответственно. Каждый логический элемент 452 И предоставляет либо (1) низкий логический уровень, если его разрешающий сигнал находится на низком логическом уровне, который указывает, что ассоциативно связанный кэш 250 не назначен интерфейсному блоку 310k, либо (2) индикатор попадания/промаха из ассоциативно связанного кэша 250, если разрешающий сигнал находится на высоком логическом уровне, который указывает, что кэш назначен интерфейсному блоку 310k. Логический элемент 454 ИЛИ принимает выходные данные логических элементов 452a-452n И и формирует индикатор попадания для интерфейсного блока 310k.

Блок 460 заполнения кэша управляет заполнением одного из кэшей, назначенных интерфейсному блоку 310k, когда имеется промах кэша. В варианте осуществления назначенный кэш, который является наиболее давно использовавшимся (LRU), т.е. неиспользованный в течение самого длительного времени, выбирается для заполнения кэша. Блок 460 заполнения кэша может заполнить весь или часть выбранного кэша новыми данными/инструкциями из основной памяти 270. Интерфейсный блок 310k может быть остановлен, пока строка целевого кэша заполняется из основной памяти 270, а ОЗУ тегов выбранного кэша обновляется, чтобы отразить новые данные/инструкции, загруженные в ОЗУ данных.

Графическая система с полностью конфигурируемыми кэшами обеспечивает большую гибкость с точки зрения назначения кэшей процессорным блокам. Данному процессорному блоку может быть назначено ноль, один, множество или даже все из доступных кэшей в зависимости от требований данных процессорных блоков. Доступные кэши могут быть назначены процессорным блокам таким способом, чтобы достичь хорошего использования кэшей и избежать узкого места при обращении к памяти в любом месте в графическом процессоре невзирая на выполняющееся графическое приложение. Доступные кэши могут интеллектуально назначаться процессорным блокам, как описано ниже.

Во многих случаях хорошая производительность может быть достигнута с частично конфигурируемыми кэшами. Кэши являются частично конфигурируемыми в том, что каждый кэш может быть назначен одному из поднабора процессорных блоков. Были выполнены исследования на различных графических приложениях, чтобы установить выгоды использования кэшей для разных графических операций. Эти исследования указывают, что кэши являются очень полезными в увеличении производительности тестов трафарета и глубины и наложении текстур многих графических приложений и только отчасти полезны для цвета и механизма создания эффектов. Следовательно, система кэш-памяти может быть спроектирована с большинством из доступных кэшей, являющихся конфигурируемыми для тестов трафарета и глубины и наложения текстур, и только с несколькими из кэшей, являющихся конфигурируемыми для цвета и механизма создания эффектов. Применение частично конфигурируемых кэшей может упростить схемы блока управления, который назначает конфигурируемые кэши, так же как и коммутатора, который связывает процессорные блоки с их назначенными кэшами.

Фиг.5 показывает вариант осуществления графической системы 500 с конфигурируемыми и специализированными кэшами. Графическая система 500 включает в себя графический процессор 510 и систему 530 кэш-памяти. Графический процессор 510 может включать в себя процессорные блоки, которые работают, как описано выше для процессорных блоков 120a-120i на фиг.1. В частности, графический процессор 510 может включать в себя механизм теста трафарета и глубины, механизм наложения текстур, механизм создания эффектов фрагмента и механизм фрагментирования, которые могут использовать данные и/или инструкции, сохраненные в кэшах.

В варианте осуществления, показанном на фиг.5, система 530 кэш-памяти включает в себя R частично конфигурируемых кэшей 550a-550r и один специализированный кэш 550s, где, как правило, R≥1. Таблица показывает возможные назначения каждого из кэшей 550a-550s, где каждый "X" указывает правильное назначение кэша. Как показано в таблице, каждый из P частично конфигурируемых кэшей 550a-550p может быть назначен для теста трафарета, теста глубины или наложения текстуры. Частично конфигурируемый кэш 550q может быть назначен для инструкций механизма создания эффектов, теста трафарета, теста глубины или наложения текстуры. Частично конфигурируемый кэш 550r может быть назначен для данных механизма создания эффектов, теста трафарета, теста глубины или наложения текстуры. Специализированный кэш 550s используется, чтобы хранить значения цвета для механизма фрагментирования. В варианте осуществления P=8, и до 10 кэшей может быть назначено для теста трафарета, теста глубины и/или наложения текстуры, предполагая, что кэши 550q и 550r не используются для инструкций и данных механизма создания эффектов. Меньшее число или дополнительные кэши также могут использоваться для системы 530 кэш-памяти.

| Процессорный блок | Кэш 550a | ... | Кэш 550p | Кэш 550q | Кэш 550r | Кэш 550s |

| Тест трафарета | X | ... | X | X | X | |

| Тест глубины | X | ... | X | X | X | |

| Наложение текстуры | X | ... | X | X | X | |

| Инструкция механизма создания эффектов | X | |||||

| Данные механизма создания эффектов | X | |||||

| Цвет | X |

Блок 532 управления назначает конфигурируемые кэши 550a-550r механизму теста трафарета и глубины, механизму наложения текстур и/или механизму создания эффектов фрагмента на основе коэффициента использования памяти этими процессорными блоками. Коммутатор 540 связывает процессорные блоки с их назначенными кэшами 550a-550r. Схема 560 разрешения конфликтов связывает кэши 550a-550s с основной памятью 570.

Фиг.5 также показывает вариант осуществления коммутатора 540. В этом варианте осуществления коммутатор 540 включает в себя интерфейсные блоки 580a-580e для теста трафарета, теста глубины, наложения текстуры, инструкции механизма создания эффектов и данных механизма создания эффектов соответственно. Интерфейсный блок 580a связывает механизм теста трафарета и глубины с кэшами, назначенными для теста трафарета, если предусмотрены, среди кэшей 550a-550r. Интерфейсный блок 580b связывает механизм теста трафарета и глубины с кэшами, назначенными для теста глубины, если предусмотрены, среди кэшей 550a-550r. Интерфейсный блок 580c связывает механизм наложения текстур с назначенными кэшами, если предусмотрены, среди кэшей 550a-550r. Интерфейсный блок 580d связывает механизм создания эффектов фрагмента с кэшем 550q, если назначен. Интерфейсный блок 580e связывает механизм создания эффектов фрагмента с кэшем 550r, если назначен. Каждый интерфейсный блок 580 может включать в себя конечный автомат и I/O-блок, например, как показано на фиг.3. Для простоты мультиплексоры для интерфейсных блоков и мультиплексоры для кэшей не показаны на фиг.5.

Фиг.5 показывает конкретный вариант осуществления системы кэш-памяти с конфигурируемыми и специализированными кэшами. Как правило, система кэш-памяти может включать в себя любое число конфигурируемых кэшей и любое число специализированных кэшей. Конфигурируемые кэши могут использоваться для любого набора графических операций, и специализированные кэши могут также использоваться для любого набора графических операций. Использование как конфигурируемых, так и специализированных кэшей может упростить схемы блока управления и коммутатора.

В вариантах осуществления, показанных на фиг.2 и 5, блок управления может назначать конфигурируемые кэши процессорным блокам различными способами. В одном варианте осуществления блок управления назначает кэши для каждого графического изображения или кадра, который должен быть визуализирован, на основе коэффициента использования памяти в предыдущем изображении/кадре. Блок управления может установить использование памяти, подсчитывая число обращений к памяти, сделанных каждым процессорным блоком, число попаданий в кэш для каждого кэша, число промахов кэша для каждого кэша и т.д. Блок управления может затем назначить больше кэшей процессорным блокам с высоким использованием памяти и меньше или не назначить кэши процессорным блокам с низким использованием памяти.

В другом варианте осуществления блок управления назначает конфигурируемые кэши процессорным блокам на основе связности графических изображений/кадров. Связность ссылается на количество изменений в последовательных 2D/3D-кадрах. Меньше кэшей может быть назначено для большей связности, когда кадры, более вероятно, должны отображать похожее содержимое, и больше кэшей может быть назначено для меньшей связности.

Еще в одном варианте осуществления блок управления назначает конфигурируемые кэши процессорным блокам на основе характеристик выполняемого графического приложения. Например, если графическая система выполняет приложение 2D-графики, тогда тест глубины не нужен и кэш может не назначаться для теста глубины. С другой стороны, если приложение 3D-графики использует только z-обход, тогда все конфигурируемые кэши могут быть назначены тесту глубины. В качестве другого примера, если выполняется простая программа создания эффектов и все из инструкций механизма создания эффектов могут быть сохранены в механизме создания эффектов фрагмента, то кэш может не назначаться механизму создания эффектов фрагмента.

Еще в одном варианте осуществления блок управления динамически назначает конфигурируемые кэши. Например, блок управления может назначить один или более кэшей процессорному блоку, когда запросы данных отправляются процессорным блоком. Блок управления может регулировать число кэшей, назначенных процессорному блоку, на основе числа запросов, статистики попаданий/промахов в кэше и/или других факторов, которые могут быть определены на лету. Операции сброса и задания недействительности могут быть выполнены на лету для кэша, который переключается или переназначается от одного процессорного блока другому процессорному блоку.

Еще в одном варианте осуществления блок управления назначает кэши с помощью комбинации статических и динамических назначений. Например, блок управления может предварительно назначить один или более кэшей данному процессорному блоку в начале воспроизведения кадра, изображения или пакета, например, на основе текущей статистики по использованию памяти процессорным блоком. Блок управления может регулировать назначение кэша этому процессорному блоку во время воспроизведения кадра, изображения или пакета, например, периодически. Новое назначение к