Дифференциальный операционный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в компараторах и прецизионных решающих усилителях с малыми значениями э.д.с. смещения нуля). Технический результат: уменьшение абсолютного значения Uсм и его температурного и радиационного дрейфа. Дифференциальный операционный усилитель содержит входной дифференциальный каскад (ДК) (1) с первым (2) и вторым (3) токовыми выходами, токовое зеркало (4), вход которого связан с первым (2) токовым выходом ДК (1), а выход связан с базой входного транзистора (Т) (5) буферного усилителя (6), первый (7) и второй (8) вспомогательные Т, первый (9) токостабилизирующий двухполюсник (ТД). В схему введен первый дополнительный Т (10) и второй ТД (11), коллектор первого Т (10) связан с шиной (12) источника питания, база подключена ко входу токового зеркала (4), эмиттер соединен со вторым (3) токовым выходом ДК (1), коллектор первого вспомогательного Т (7) подключен ко входу токового зеркала (4), база соединена с эмиттером Т (5) буферного усилителя (6) и коллектором второго вспомогательного Т (8) и первым выходом устройства, эмиттер первого Т (7) соединен с базой второго Т (8), эмиттер которого подключен ко второму ТД (11) и второму выходу устройства, причем первый ТД (9) связан с выходом токового зеркала (4). 3 з.п. ф-лы, 8 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в компараторах и прецизионных решающих усилителях с малыми значениями э.д.с. смещения нуля).

В современной радиоэлектронной аппаратуре находят применение дифференциальные операционные усилители (ОУ) с существенными различными параметрами.

Особое место занимают дифференциальные операционные усилители (ОУ) с несимметричным включением неуправляемой активной нагрузки. Такие ОУ имеют одноканальную структуру входного каскада и характеризуются меньшими фазовыми искажениями сигнала по цепи общей обратной связи. Предлагаемое изобретение относится к классу ОУ на базе несимметричных входных каскадов [1-11], которые до сих пор находили применение только в устройствах с низкими требованиями к стабильности нулевого уровня.

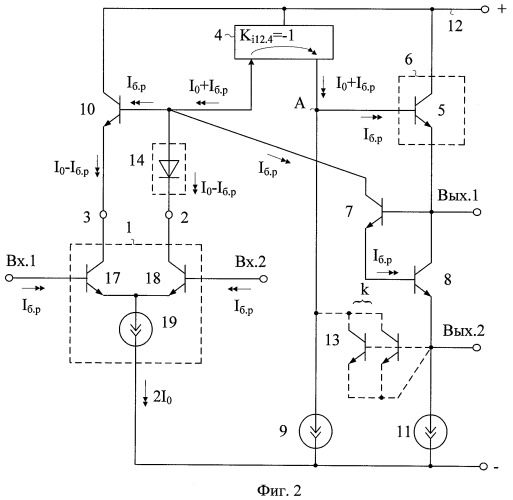

Наиболее близким по сущности к заявляемому техническому решению является классическая схема ОУ фиг.1, представленная в патенте США №4.366.442 fig.2, которая также присутствует в большом числе других патентов, например, [1-11], имеющих в качестве цепи нагрузки входных транзисторов несимметрично включенные управляемые токовые зеркала или неуправляемые токостабилизирующие двухполюсники.

Существенный недостаток известного ОУ фиг.1 состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм), зависящей от свойств его архитектуры.

Основная задача предлагаемого изобретения состоит в уменьшении абсолютного значения Uсм и его температурного и радиационного дрейфа.

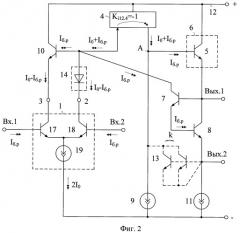

Поставленная задача достигается тем, что в дифференциальном операционном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, токовое зеркало 4, вход которого связан с первым 2 токовым выходом выходного дифференциального каскада 1, а выход связан с базой входного транзистора 5 буферного усилителя 6, первый 7 и второй 8 вспомогательные транзисторы, первый 9 токостабилизирующий двухполюсник, предусмотрены новые элементы и связи - в схему введен первый дополнительный транзистор 10 и второй токостабилизирующий двухполюсник 11, коллектор первого 10 дополнительного транзистора связан с шиной 12 источника питания, база подключена ко входу токового зеркала 4, эмиттер соединен со вторым 3 токовым выходом входного дифференциального каскада 1, коллектор первого 7 вспомогательного транзистора подключен ко входу токового зеркала 4, база соединена с эмиттером входного транзистора 5 буферного усилителя 6 и коллектором второго 8 вспомогательного транзистора и первым выходом устройства, эмиттер первого 7 вспомогательного транзистора соединен с базой второго 8 вспомогательного транзистора, эмиттер которого подключен ко второму 11 токостабилизирующему двухполюснику и второму выходу устройства, причем первый 9 токостабилизирующий двухполюсник связан с выходом токового зеркала 4.

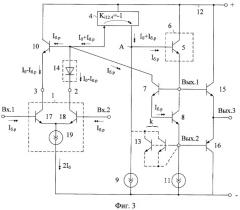

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1, п.2 и п.3 формулы изобретения. На фиг.3 представлена схема заявляемого устройства в соответствии с п.4 формулы изобретения.

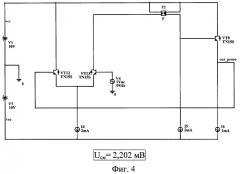

На фиг.4 и фиг.5 показаны схемы дифференциального ОУ-прототипа (фиг.4) и заявляемого ОУ (фиг.5) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.6 приведены температурные зависимости напряжения смещения нуля сравниваемых схем фиг.4 и фиг.5.

На фиг.7 показана схема ОУ фиг.2 в среде компьютерного моделирования PSpice при четырех параллельно включенных транзисторах терморадиационной компенсации, а на фиг.8 - графики зависимости Uсм схем фиг.4 и фиг.7.

Дифференциальный операционный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, токовое зеркало 4, вход которого связан с первым 2 токовым выходом выходного дифференциального каскада 1, а выход связан с базой входного транзистора 5 буферного усилителя 6, первый 7 и второй 8 вспомогательные транзисторы, первый 9 токостабилизирующий двухполюсник. В схему введен первый дополнительный транзистор 10 и второй токостабилизирующий двухполюсник 11, коллектор первого 10 дополнительного транзистора связан с шиной 12 источника питания, база подключена ко входу токового зеркала 4, эмиттер соединен со вторым 3 токовым выходом входного дифференциального каскада 1, коллектор первого 7 вспомогательного транзистора подключен ко входу токового зеркала 4, база соединена с эмиттером входного транзистора 5 буферного усилителя 6 и коллектором второго 8 вспомогательного транзистора и первым выходом устройства, эмиттер первого 7 вспомогательного транзистора соединен с базой второго 8 вспомогательного транзистора, эмиттер которого подключен ко второму 11 токостабилизирующему двухполюснику и второму выходу устройства, причем первый 9 токостабилизирующий двухполюсник связан с выходом токового зеркала 4.

Кроме этого, на фиг.2, в соответствии с п.2 формулы изобретения, в схему введены k>2 транзисторов терморадиационной компенсации 13, коллекторы которых соединены с выходом токового зеркала 4.

Также на фиг.2, в соответствии с п.3 формулы изобретения, вход токового зеркала 4 связан со вторым 2 токовым выходом входного дифференциального каскада 1 через согласующий токостабилизирующий двухполюсник 14, содержащий один или несколько p-n переходов.

На фиг.3, в соответствии с п.4 формулы изобретения, эмиттер первого 5 входного транзистора буферного усилителя 6 связан с базой первого 15 выходного транзистора, а эмиттер второго 8 вспомогательного транзистора соединен с базой второго 16 выходного транзистора, причем эмиттеры первого 15 и второго 16 выходных транзисторов объединены и подключены к третьему выходу устройства (Вых.3). Это обеспечивает двухтактное усиление сигнала. В схемах фиг.2. фиг.3 входной дифференциальный каскад 1 реализован на базе транзисторов 17, 18 и двухполюснике 19.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля Uсм в схеме фиг.2, т.е. зависящие от схемотехники ОУ.

Если ток двухполюсника 19 равен величине 2I0, а токи двухполюсников 9 и 11 - величине I0(I9=I11=I0), то токи коллекторов транзисторов схемы:

где Iб.р=Iэ.i/βi - ток базы n-p-n (Iб.р) или p-n-p (Iб.n) транзисторов при эмиттерном токе Iэ.i=I0;

Iвх.4, Iвых.4 - входной и выходной токи токового зеркала 4;

βi - коэффициент усиления по току базы транзисторов.

Учитывая, что транзисторы 13 закрыты, находим, что разность токов в узле «А» при его коротком замыкании на эквипотенциальную общую шину

где Iб.5=Iб.p - ток базы p-n-p транзистора 5.

Таким образом, в заявляемом устройстве при выполнении условия (9) уменьшается систематическая составляющая Uсм, обусловленная конечной величиной (3 транзисторов и его радиационной (или температурной) зависимостью. Как следствие, это уменьшает Uсм, так как разностный ток Ip в узле «А» создает Uсм, зависящее от крутизны S преобразования входного дифференциального напряжения uвх в выходной ток узла «А»:

где rэ17=rэ18 - сопротивления эмиттерных переходов входных

транзисторов 17 и 18 входного дифференциального каскада 1. Поэтому для схемы фиг.2

где φт=26 мВ - температурный потенциал.

В ОУ-прототипе Ip≠0, поэтому здесь систематическая составляющая Uсм получается значительно больше, чем в заявляемой схеме (фиг.4, фиг.5).

Компьютерное моделирование схем фиг.4, фиг.5 и фиг.7 подтверждает (фиг.6, фиг.8) данные теоретические выводы.

Несмотря на существенное уменьшение β транзисторов вследствие радиационных воздействий, предлагаемый ОУ имеет и в этом случае меньшее напряжение смещения нуля, чем ОУ-прототип.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока.

Литература

1. Патент США №4.415.868 fig.3.

2. Патент ФРГ №2928841 fig.3.

3. Патент Японии JP 54-34589 кл. 98 (5) А014.

4. Патент Японии JP 154-10221, кл. H03F 3/45.

5. Патент Японии JP 54-102949, кл. 98 (5) А21.

6. Патент США №4.366.442 fig.2.

7. Патент США №6.426.678.

8. Патентная заявка США 2007/0152753 fig.5c.

9. Патент США №6.531.920, fig.4.

10. Патент США №4.262.261.

11. Ежков Ю.А. Справочник по схемотехнике усилителей. - 2-е изд., перераб. - М.: ИП РадиоСофт, 2002. - 272 с. - Рис.9.3 (стр.235).

1. Дифференциальный операционный усилитель, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, токовое зеркало (4), вход которого связан с первым (2) токовым выходом выходного дифференциального каскада (1), а выход связан с базой входного транзистора (5) буферного усилителя (6), первый (7) и второй (8) вспомогательные транзисторы, первый (9) токостабилизирующий двухполюсник, отличающийся тем, что в схему введен первый дополнительный транзистор (10) и второй токостабилизирующий двухполюсник (11), коллектор первого (10) дополнительного транзистора связан с шиной (12) источника питания, база подключена ко входу токового зеркала (4), эмиттер соединен со вторым (3) токовым выходом входного дифференциального каскада (1), коллектор первого (7) вспомогательного транзистора подключен ко входу токового зеркала (4), база соединена с эмиттером входного транзистора (5) буферного усилителя (6), и коллектором второго (8) вспомогательного транзистора, и первым выходом устройства, эмиттер первого (7) вспомогательного транзистора соединен с базой второго (8) вспомогательного транзистора, эмиттер которого подключен ко второму (11) токостабилизирующему двухполюснику и второму выходу устройства, причем первый (9) токостабилизирующий двухполюсник связан с выходом токового зеркала (4).

2. Дифференциальный операционный усилитель по п.1, отличающийся тем, что в схему введены k>2 транзисторов терморадиационной компенсации (13), коллекторы которых соединены с выходом токового зеркала (4).

3. Дифференциальный операционный усилитель по п.1, отличающийся тем, что вход токового зеркала (4) связан со вторым (2) токовым выходом входного дифференциального каскада (1) через согласующий токостабилизирующий двухполюсник (14).

4. Дифференциальный операционный усилитель по п.1, отличающийся тем, что эмиттер первого (5) входного транзистора буферного усилителя (6) связан с базой первого (15) выходного транзистора, а эмиттер второго (8) вспомогательного транзистора соединен с базой второго (16) выходного транзистора, причем эмиттеры первого (15) и второго (16) выходных транзисторов объединены и подключены к третьему выходу устройства.