Усилитель считывания с одним входом и двумя выходами

Иллюстрации

Показать всеИзобретение относится к устройствам для записи или считывания информации в цифровых запоминающих устройствах, а именно к усилителям считывания с одним входом и двумя выходами. Техническим результатом является повышение синхронности выходных сигналов и увеличение быстродействия за счет отсутствия генерации дополнительных дифференциальных сигналов. Устройство содержит защелку, состоящую из пары nMOSFET, в которой первый и второй nMOSFET перекрещены один с другим, и пары pMOSFET, в которой первый и второй pMOSFET перекрещены один с другим; первый ключ pMOSFET, соединенный с защелкой и состоящий из стока, истока, затвора; второй ключ pMOSFET, соединенный с защелкой и состоящий из стока, истока, затвора; два предзаряжающих транзистора nMOSFET, выполненных с возможностью обеспечения низкого импеданса между нулевым уровнем и защелкой; pMOSFET, выполненный с возможностью обеспечения низкого импеданса между Vcc и истоками pMOSFET защелки; инвертор с цепью предзаряда, который состоит из включенных последовательно первого nMOSFET, управляемого битовой линией, и второго nMOSFET в диодном включении, причем второй nMOSFET инвертора соединяет нулевой уровень и исток первого nMOSFET инвертора, а сток первого nMOSFET инвертора предзаряжен и соединен с линией данных через ключ или через мультиплексор. 1 з.п. ф-лы, 4 ил.

Реферат

Изобретение относится к устройствам для записи или считывания информации в цифровых запоминающих устройствах, а именно к усилителям считывания с одним входом и двумя выходами, и может применяться, в частности, в ROM (постоянных запоминающих устройствах) и в низковольтных цепях.

Из уровня техники известны различные конструкции усилителей считывания и разветвителей, однако большинство решений направлено на снижение энергопотребления таких устройств (см., например, патент Японии №11260064 [1] и патент США №7313040 [2]).

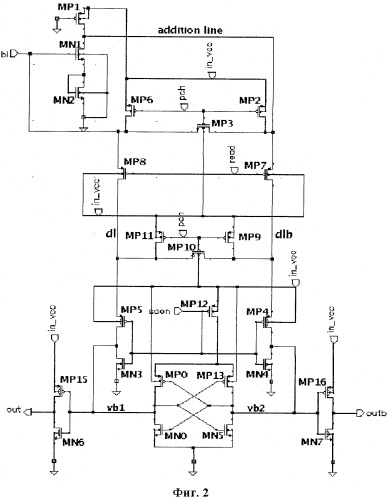

Наиболее близким к заявленному изобретению является усилитель считывания с одним входом и двумя выходами (Фиг.1), описанный в патенте США №6501302 [3], содержащий перекрестно соединенные транзисторы, подключенные к опорному напряжению; первый входной транзистор и второй входной транзистор, которые соединены с перекрестно соединенными транзисторами, причем первый входной транзистор соединен с битовой линией, а второй входной транзистор соединен с опорным напряжением; при этом инвертор выполнен с возможностью пересылки входного сигнала с битовой линии в виде комплементарного к исходному; контрольная цепь соединена со вторым входным транзистором и выполнена с возможностью получения сигнала, комплементарного к сигналу битовой линии, на выходе перекрестно соединенных транзисторов - дифференциальный сигнал. Приведенный в данном патенте метод преобразования недифференциального входного сигнала в дифференциальный выходной включает получение входного сигнала с битовой линии, инвертирование полученного сигнала с целью преобразования в комплементарный, управление разрядом и зарядом опорных узлов, с помощью сигнала, комплементарного сигналу с битовой линии, получение дифференциального выходного сигнала, соответствующего входному сигналу. Данный усилитель выбран в качестве прототипа заявляемого изобретения.

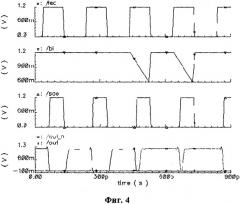

Недостатком прототипа является недостаточная синхронность выходных сигналов. Как видно из Фиг.1, node_f предзаряжается в течение всей фазы sc, и в то же время на node_t подается сигнал с bl. Таким образом, результат на выходе out появляется позже, чем на выходе out_n. Фактически выходной сигнал прототипа не является дифференциальным (см. Фиг.4). Кроме того, поскольку выход задают после sae фазы, то может быть использован единственный выход out_n, это приводит к возникновению такой проблемы, как генерация дополнительного дифференциального сигнала на основе out_n и временных задержек.

Задачей, на решение которой направлено заявляемое изобретение, является создание усилителя считывания с одним входом и двумя выходами с повышенной синхронностью выходных сигналов и увеличенным быстродействием благодаря отсутствию генерации дополнительных дифференциальных сигналов.

Технический результат достигается за счет создания усилителя считывания с одним входом и двумя выходами, содержащего защелку, которая состоит из пары nMOSFET, в которой первый и второй nMOSFET перекрещены один с другим, и пары pMOSFET, в которой первый и второй pMOSFET перекрещены один с другим; первый ключ pMOSFET, соединенный с защелкой и состоящий из стока, истока, затвора; второй ключ pMOSFET, соединенный с защелкой, и состоящий из стока, истока, затвора; два предзаряжающих транзистора nMOSFET, выполненных с возможностью обеспечения низкого импеданса между нулевым уровнем и защелкой; pMOSFET, выполненный с возможностью обеспечения низкого импеданса между Vcc и истоками pMOSFET защелки; инвертор с цепью предзаряда, который состоит из включенных последовательно первого nMOSFET, управляемого битовой линией, и второго nMOSFET в диодном включении, причем второй nMOSFET инвертора соединяет нулевой уровень и исток первого nMOSFET инвертора, а сток первого nMOSFET инвертора предзаряжен и соединен с линией данных через ключ или мультиплексор.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими чертежами.

Фиг.1. Усилитель считывания с одним входом и двумя выходами, известный из уровня техники (прототип).

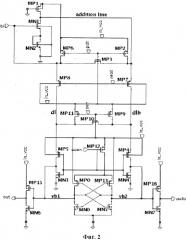

Фиг.2. Усилитель считывания с одним входом и двумя выходами, выполненный согласно изобретению.

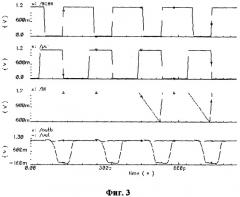

Фиг.3. Временная диаграмма усилителя считывания с одним входом и двумя выходами, выполненного согласно изобретению.

Фиг.4. Временная диаграмма усилителя считывания с одним входом и двумя выходами, известного из уровня техники (прототипа).

Цепь заявляемого усилителя считывания с одним входом и двумя выходами (см. Фиг.2) состоит из входного инвертора (MP1, MN1 и MN2); двух цепей предзаряда MP9, MP10, MP11 и MP2, MP3, MP6; защелки (устройства MN0, MP0, MN5, MP13, MP12); транзисторов MN3, MN4, предзаряжающих выходные узлы защелки; части мультиплексора (MP8 и MP7); двух ключей MP4, MP5 и выходных инверторов (MN6, MP15 и MN7, MP16).

Защелка (см. Фиг.2) состоит из пары nMOSFET (MN0, MN5), в которой первый и второй nMOSFET (MN0, MN5) перекрещены друг с другом и пары pMOSFET (MP0, MP13), в которой первый и второй pMOSFET (MP0, MP13) перекрещены друг с другом. pMOSFET (MP5) соединен с защелкой и состоит из стока, истока, затвора. pMOSFET (MP4) соединен с защелкой и состоит из стока, истока, затвора. Два nMOSFET (MN3, MN4), обеспечивают низкий импеданс между нулевым уровнем и защелкой. pMOSFET (MP12) обеспечивает низкий импеданс между Vcc и истоками pMOSFET (MP0, MP13) защелки. Инвертор с цепью предзаряда состоит из первого nMOSFET (MN1), управляемого битовой линией, второго nMOSFET (MN2) в диодном включении, включенных последовательно, причем второй nMOSFET (MN2) обеспечивает соединение нулевого уровня и истока первого nMOSFET (MN1), а сток первого nMOSFET (MN1) предзаряжен и соединен с линией данных через ключ или мультиплексор.

Заявляемое устройство (см. Фиг.2) работает по алгоритму, состоящему из трех этапов. На первом этапе на read подают высокий уровень, на pch подают низкий уровень, на saen подают высокий уровень. Проходные транзисторы PMOS MP7 и MP8 закрыты. Транзисторы MP9, MP10, MP11 и MP2, MP3, MP6, формирующие две цепи предзаряда, открыты. MN3 и MN4 открыты. MP4, MP5 закрыты. Линии bl, addition line, dl, dlb предзаряжены высоким уровнем, a vb1, vb2 предзаряжены низким уровнем.

На втором этапе на read подается низкий уровень, на pch - высокий, на saen - высокий. MP9, MP10 и MP11 закрыты. Проходные PMOS MP7 и МР8 открыты. При начале чтения напряжение на битовой линии начинает падать. Предположим, что считывается 1 (высокий уровень), при этом MN1, находящийся в режиме насыщения, формирует ток, которым заряжается МР4. Размеры MN1, MN2 и MP1 подбирают таким образом, чтобы ток на addition line был ниже тока bl в случае считывания нуля.

На третьем этапе на read подают низкий уровень, pch находится на высоком уровне, на saen подают низкий уровень. Устройства MP4 и MP5 открыты. Устройства MN3 и MN4 закрыты. Разница токов Idl и Idlb формирует заряд в узлах vb1 и vb2. Результат запоминают с помощью транзисторов MN0, MP0 и MN5, MP13.

Устройства MN6, MP15 и MN7, MP16 формируют два инвертора, которые усиливают и инвертируют результат.

На Фиг.3 показаны четыре полные стадии (этапа) работы заявляемого усилителя считывания. На первых двух стадиях считывают 1 (напряжение на bl Vcc=1.2 V). На следующих двух стадиях считывают 0 (напряжение на bl опускается до Vcc - delta=0.6 V).

Результат (out и outb) инвертирован.

Предпочтительная реализация заявляемого усилителя считывания основана на CMOS схемотехнике. В описанном выше примере заявленного усилителя используют pMOSFET устройства MP5 и MP4 с высоким пороговым напряжением (W/L=1.5u/0.06u), другие устройства, кроме выходных MOSFET в инверторах, это устройства с низким пороговым напряжением (MP6 и MP2 с w/1=5u/0.06u, MN1 и MN2 с w/1=0.21u/0.06u, MP1 с w/1=0.5u/0.06u). Вместо проходных PMOS MP2 и MP6 может быть использован мультиплексор для выбора столбца памяти.

При использовании в ROM с фазой предзаряда и фазой усиления заявляемый усилитель считывает бит информации в фазе чтения, в ходе которой обеспечивается низкий импеданс между битовой линией (bl) и выходным портом защелки, кроме того, низкий импеданс обеспечивается также между дополнительной линией (addition line) и выходным портом защелки.

Приведенный выше вариант выполнения изобретения изложен с целью иллюстрации настоящего изобретения, и специалистам должно быть понятно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла настоящего изобретения, раскрытого в прилагаемой формуле изобретения.

1. Усилитель считывания с одним входом и двумя выходами, содержащий защелку, которая состоит из пары nMOSFET, в которой первый и второй nMOSFET перекрещены один с другим, и пары pMOSFET, в которой первый и второй pMOSFET перекрещены один с другим; первый ключ pMOSFET, соединенный с защелкой и состоящий из стока, истока, затвора; второй ключ pMOSFET, соединенный с защелкой и состоящий из стока, истока, затвора; два предзаряжающих транзистора nMOSFET, выполненных с возможностью обеспечения низкого импеданса между нулевым уровнем и защелкой; pMOSFET, выполненный с возможностью обеспечения низкого импеданса между Vcc и истоками pMOSFET защелки; инвертор с цепью предзаряда, который состоит из включенных последовательно первого nMOSFET, управляемого битовой линией, и второго nMOSFET в диодном включении, причем второй nMOSFET инвертора соединяет нулевой уровень и исток первого nMOSFET инвертора, а сток первого nMOSFET инвертора предзаряжен и соединен с линией данных через ключ.

2. Усилитель по п.1, отличающийся тем, что сток первого nMOSFET инвертора соединен с линией данных через мультиплексор.