Двухканальная система телевидения

Иллюстрации

Показать всеИзобретение относится к технике радиосвязи и может быть использовано для цифрового телевещания параллельно двух телеканалов на одной несущей частоте. Техническим результатом является цифровое телевещание системой телевидения параллельно двух телеканалов применением разделения сигналов их кодов по полярному признаку. Результат достигается тем, что в систему телевидения, содержащую передающую и приемную сторону, вводятся на передающей стороне второй фотоэлектрический преобразователь /ФЭЛ/, вторые три АЦП видеосигнала, вторые три кодера, на приемной стороне второй канал обработки кодов сигналов R2, G2, В2 второго телеканала и второй плоскопанельный экран. 18 ил, 2 табл.

Реферат

Изобретение относится к технике радиосвязи и может быть использовано для цифрового телевещания параллельно двух телеканалов на одной несущей частоте.

За пототип принята "Система телевидения" [1], содержащая на передающей стороне один Фотоэлектрический преобразователь /ФЭП/, формирующий три аналоговых сигнала основных цветов R, G, В одного телеканала, три АПП видеосигнала, два АЦП сигнала, звука, задающий генератор синусоидальных колебаний и синтезатор частот, три кодера, формирователь кодов, два самоходных распределителя импульсов /СРИ/, передатчик радиосигналов из одного канала, на приемной стороне содержащая блок управления, тракт приема и обработки кодов видеосигналов, плоскопанельный светодиодный экран, канал формирования управляющих сигналов и два канала звукового сопровождения. Тракт приема и обработки кодов видеосигналов включает блок приема радиосигналов, усилитель радиочастоты и двухполярный амплитудный детектор, и один канал обработки кодов видеосигналов в составе канала сигнала R, канала сигнала G и канала сигнала В. Канал сигнала R включает первый формирователь импульсов, первый приемный регистр, регистр R, декодер, блок удвоения кодов, накопитель кодов кадра и формирователь управляющих сигналов, канал сигнала G включает регистр G, декодер, блок удвоения кодов, накопитель кодов кадра и формирователь управляющих сигналов, канал сигнала В включает второй формирователь импульсов, второй приемный регистр, регистр В, декодер, блок удвоения кодов, накопитель кодов кадра и формирователь управляющих сигналов. Недостатком системы прототипа является цифровое телевещание одного телеканала.

Цель изобретения - выполнение системой телевидения параллельного формирования кодов видеосигналов двух телеканалов, передачу и прием их на одной несущей частоте.

Техническим результатом является цифровое телевещание системой телевидения параллельно двух телеканалов применением разделения сигналов их кодов по полярному признаку.

Сущность изобретения в том, что в систему телевидения, содержащую на передающей стороне один фотоэлектрический преобразователь /ФЭП/, три АЦП видеосигнала, два АЦП сигнала звука, генератор синусоидальных колебаний и синтезатор частот, формирователь кодов, два самоходных распределителя импульсов /СРИ/, два ключа и передатчик радиосигнала, на приемной стороне блок управления, тракт приема и обработки кодов видеосигналов, включающий блок приема радиосигнала, усилитель радиочастоты, двухполярный амплитудный детектор и один канал обработки кодов цветовых сигналов R1, G1, B1, один плоскопанельный экран, канал формирования управляющих сигналов и два канала звукового сопровождения, вводятся на передающей стороне второй ФЭП, вторые три АЦП видеосигнала, вторые три кодера, на приемной стороне второй канал обработки цветовых сигналов R2, G2, B2 второго телеканала и второй плоскопанельный экран. На передающей стороне в обоих телеканалах применяется видеорежим: 700отсч × 1000стр × 25 Гц, где 700 - число кодируемых отсчетов в строке, 1000 - число кодируемых строк в кадре, 25 Гц - частота кадров. Частота дискретизации при аналого-цифровом преобразовании составляет: fд = 25 Гц × 1000 × 700=17.5 МГц, частота строк: 25 Гц × 1000стр = 25 кГц. При формировании цифрового изображения всегда будут последовательно идущие коды, равные по величине, и чем выше частота дискретизации, тем равных кодов будет больше. Для сжатия видеоинформации каждого цветового сигнала применяется свой кодер с общим коэффициентом сжатия 4. При сжатии потока кодов в четыре раза частота дискретизации на выходе каждого кодера составляет 4,375 МГц После кодеров существует два потока кодов: первый - поток кодов первого телеканала, включающий девятиразрядные коды цветовых сигналов R1, G1, B1, второй - поток кодов второго телеканала из девятиразрядных кодов цветовых сигналов R2, G2, B2. Следующий за кодерами формирователь кодов из потоков кодов обоих телеканалов выдает на выходе один поток кодов, в котором единицы кодов первого телеканала представляются положительными полусинусоидами, единицы кодов второго телеканала представляются отрицательными полусинусоидами. Тактовая частота синусоидальных колебаний в формирователе кодов составляет: fт - 4.375 МГц × 27разр = 118,125 МГц, где 4,375 МГц - частота дискретизации кодов после кодеров, 27 - число разрядов в каждом суммарном коде /9×3/ выходного потока с формирователя кодов.

Период следования кодов 228 нс период следования разрядов в коде 8,5 нс Несущая частота в передатчике применяется

fн = 118,125 МГц × 15=1771,875 МГц.

Верхняя боковая частота fнв=1771,875+118,125=1890 МГц, нижняя боковая частота fнн=1771,875-118,125=1653,75 МГц. На приемной стороне декодеры 100% восстанавливают потоки кодов каждого цвета, затем число отсчетов в каждой строке удваивается с 700 до 1400 и воспроизводятся два видеорежима 1400отсч × 1000стр × 25 Гц.

Разрешение кадра при воспроизведении изображения в каждом канале составляет 1400×1000=1,4×106 пикселов.

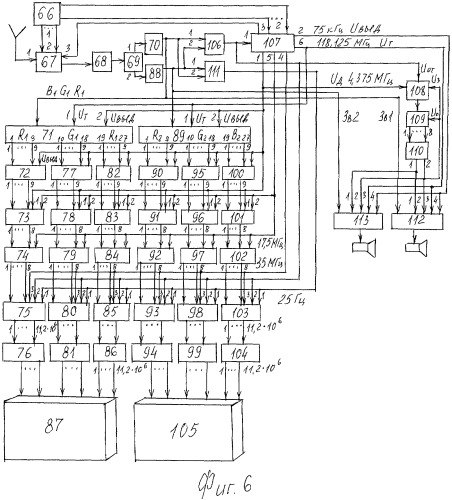

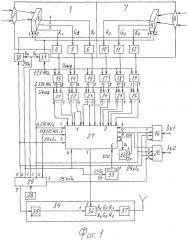

Передающая сторона на фиг.1, структура цифрового потока на фиг.2, кодер на фиг.3, диаграмма работы кодера на фиг.4, формирователь кодов на фиг.5, приемная сторона на фиг.6, спектр амплитудно-модулированного сигнала на фиг.7, двухполярный амплитудный детектор на фиг.8, декодер на фиг.9, блок удвоения отсчетов на фиг.10, накопитель кодов кадра на фиг.11, блок регистров на фиг.12, 13, блок выделения ССИ /КСИ/ на фиг.14, временные диаграммы работы системы на фиг.15, общий вид элемента матрицы на фит.16, излучающая ячейка на фиг.17, расположение матриц в экране на фиг.18.

Передающая сторона включает /фиг.1/ первый ФЭП 1, являющийся датчиком сигналов трех основных цветов R1, G1, B1 первого телеканала и содержащий объектив 2, в фокальной плоскости которого расположена фоточувствительная сторона первой матрицы ПЗИ 3 и прибора с зарядовой инжекцией из трехслойного КМОП-датчика ([2] с.552, [3] с.832-835), с оптическим разрешением 1400×1000, обеспечивающая 24-битную глубину цвета, с первого по третий выходы матрицы ПЗИ 3 подключены к входам первого-третьего предварительных усилителей 4, 5, 6, выходы которых являются выходами первого ФЭП 1. Передающая сторона включает второй ФЭП 7, являющийся датчиком сигналов трех основных цветов R2, G2, B2 второго телеканала и содержащий объектив 8, в фокальной плоскости которого расположена фоточувствительная сторона второй матрицы ПЗИ 9, идентичной первой матрице ПЗИ 3. Выходы матрицы ПЗИ 9 подключены к входам четвертого-шестого предварительных усилителей 10, 11, 12, выходы которых являются выходами второго ФЭП 7. Передающая сторона включает первый 13, второй 14 и третий 15 АЦП видеосигнала, преобразующие аналоговые видеосигналы первого телеканала в 8-разрядные коды, первый АЦП 16 сигнала звука первого телеканала включает четвертый 17, пятый 18 и шестой 19 АЦП видеосигнала, преобразующие видеосигналы второго телеканала в 8-и разрядные коды, и второй АЦП 20 сигнала звука включает первый 21, второй 22, третий 23 кодеры, входы которых подключены соответственно к выходам АЦП 13, 14, 15 первого канала, включает четвертый 24, пятый 25 и шестой 26 кодеры, входы которых подключены соответственно к выходам АЦП 17, 18, 19 второго канала. Передающая сторона включает формирователь 27 кодов, последовательно соединенные задающий генератор 28 синусоидальных колебаний со стабильностью 10-7 и синтезатор 29 частот, первый 30 и второй 31 ключи, первый самоходный распределитель 32 импульсов /СРИ/ ([4] с.269, 274), формирующий код строчных синхроимпульсов из 27 единиц /ССИ/, второй СРИ 33, формирующий код кадрового синхроимпульса /КСИ/ из 27 единиц, и передатчик 34 радиосигналов, включающий последовательно соединенные усилитель 35 несущей частоты 1771,875 МГц, амплитудный модулятор 36 и выходной усилитель 37. Амплитудный модулятор 36 состоит из последовательно соединенных кольцевого модулятора и полосового фильтра [5 с.234]. В кольцевом модуляторе появляется несущая частота, полосовой фильтр отфильтровывает нижнюю боковую частоту 1653,75 МГц, верхняя боковая частота 1890 МГц с информацией кодов первого канала R1, G1, B1 и кодов R2, G2, B2 второго канала поступает в выходной усилитель 37. При стабильности несущей 10-7 занимаемая полоса в эфире составляет ± 189 Гц или 378 Гц. АЦП 13-15 и 17-19 видеосигналов выполнены идентично и принимаются без изменений, как в аналоге [6 с. 9, фиг.3]. АЦП 16 и 20 сигнала звука выполнены, идентично как в аналоге [6 с. 9, фиг.4]. АЦП 16, 20 преобразуют звуковые сигналы в 16-и разрядные коды, поступающие с частотой дискретизации 75 кГц /25 кГц × 3/ на третий и четвертый информационные входы формирователя 27 кодов /фиг.1/. Кодеры 21-26 идентичны, каждый включает /фиг.3/ последовательно соединенные регистр 38, схему 39 сравнения /компаратор/, счетчик 40 импульсов и дешифратор 41, последовательно соединенные блок 42 элементов задержек, блок 43 ключей и буферный накопитель 44 кодов кадра. Информационными входами являются поразрядно объединенные первый-восьмой входы регистра 38. первые 1-8 входы схемы 39 сравнения и входы блока 42 элементов задержек. Выходами являются первый-девятый выходы буферного накопителя 44 кодов кадра, объем которого составляет 200×103 девятиразрядных кодов. Управляющим входом является управляющий вход /4,375 МГц/ блока 44. Формирователь 27 кодов включает /фиг.5/ четыре канала, первый и второй каналы идентичны. Первый канал включает последовательно соединенные первый блок 45 элементов И из 27 элементов И, первый 46 и второй 47 элементы ИЛИ, первый выходной ключ 48 и первый СРИ 49, второй канал включает второй блок 50 элементов И из 27 элементов И, третий 51 и четвертый 52 элементы ИЛИ, второй выходной ключ 53 и второй СРИ 54. Третий канал включает третий блок 55 элементов И из 16 элементов И, пятый элемент 56 ИЛИ и третий СРИ 57, четвертый канал включает четвертый блок 58 элементов И из 16 элементов И, шестой элемент 59 ИЛИ и четвертый СРИ 60. Формирователь 27 кодов включает первый 61, второй 62, третий 63 ключи и последовательно соединенные счетчик 64 импульсов и дешифратор 65. Информационными входами блока 27 являются: первым - первые /с первого по 27/ входы элементов И блока 45, вторым - первые /с первого по 27/ входы элементов И блока 50, третьим - первые /с первого по 16/ входы элементов И блока 55, четвертым - первые /с первого по 16/ входы элементов И блока 58, пятым - сигнальный вход третьего ключа 63, шестым - третий вход четвертого элемента ИЛИ 52. Первым выходом блока 27 являются объединенные выходы выходных ключей 48, 53, вторым - третий выход дешифратора 65. подключенный к входу СРИ 32. Управляющими входами блока 27 являются: первым - объединенные входы ключей 61, 62 и счетный вход счетчика 64 импульсов, вторым - объединенные сигнальные входы выходных ключей 48, 53, третьим - управляющий вход U0 счетчика 64 импульсов, четвертым - управляющий вход третьего ключа 63 /U/. Первый выход дешифратора 65 подключен к первому управляющему входу Uот ключа 61, второй выход дешифратора 65 подключен к второму управляющему входу UЗ ключа 61 и к первому управляющему входу Uот - ключа 62, третий выход дешифратора 65 подключен к второму управляющему входу Uз ключа 62 и является вторым выходом блока 27, подключенным к входу СРИ 32 /Фиг.1/. Вторые входы элементов И в блоках 45, 50, 55, 58 подключены соответственно к выходам СРИ 49, 54, 57, 60, каждый из которых имеет по 27 выходов. Выходы СРИ 57, 60 с первого по шестнадцатый подключены к вторым входам элементов И в блоках 55, 58, а остальные выходы с 17-го по двадцать седьмой свободны. Выход первого ключа 61 подключен к входам СРИ 49, 54, выход ключа 62 подключен к входам СРИ 57, 60. Вход третьего ключа 63 является пятым информационным входом блока 27, а выход ключа 63 подключен к третьему входу второго элемента ИЛИ 47. Приемная сторона включает /Фиг.6/ антенну, блок 66 управления /выбор каналов/, тракт приема и обработки кодов видеосигналов, канал формирования управляющих сигналов, первый и второй плоскопанельные экраны и два идентичных канала звукового сопровождения. Тракт приема и обработки кодов видеосигналов производит прием кодов первого телеканала /R1, G1, B1/, прием кодов второго телеканала /R2, G2, B2/ и включает последовательно соединенные блок 67 приема радиосигналов, усилитель 68 радиочастоты и двухполярный амплитудный детектор 69, первый канал обработки кодов видеосигналов, который включает последовательно соединенные первый формирователь 70 импульсов, первый приемный регистр 71, содержащий двадцать семь разрядов, и три канала: канал сигнала R1, канал сигнала G1, канал сигнала B1. Канал сигнала R1 включает последовательно соединенные регистр 72 R1, декодер 73, блок 74 удвоения /обработки/ кодов, накопитель 75 кодов R1 кадра и блок 76 импульсных усилителей, канал сигнала G1 включает последовательно соединенные регистр G1 77, декодер 78, блок 79 удвоения кодов, накопитель 80 кодов G1 кадра и блок 81 импульсных усилителей, канал сигнала В1 включает последовательно соединенные регистр В1 82, декодер 83, блок 84 удвоения кодов, накопитель 85 кодов В1 кадра и блок 86 импульсных усилителей. Выходы блоков 76, 81, 86 подключены к соответствующим входам первого плоскопанельного экрана 87.

Второй канал обработки кодов видеосигналов включает последовательно соединенные второй формирователь 88 импульсов, второй приемный регистр 89 и три канала: канал сигнала R2 канал сигнала G2, канал сигнала B2, канал сигнала R2 включает последовательно соединенные регистр R2 90, декодер 91, блок 92 удвоения кодов, накопитель кодов R2 кадра 93 и блок 94 импульсных усилителей, содержащий импульсных усилителей по числу выходов накопителя 93 кодов R2 кадра /11,2×106/, канал сигнала G2 включает последовательно соединенные регистр G2 95, декодер 96, блок 97 удвоения кодов, накопитель 98 кодов G2 кадра, блок 99 импульсных усилителей. Канал сигнала В2 включает последовательно соединенные регистр В2 100, декодер 101, блок 102 удвоения кодов, накопитель 103 кодов В2 кадра и блок 104 импульсных усилителей. Выходы блоков 94, 99, 104 подключены к соответствующим входам второго плоскопанельного экрана 105. Порядок работы приемной стороны определяет канал формирования управляющих сигналов, включающий последовательно соединенные блок 106 выделения строчных синхроимпульсов /ССИ/, синтезатор 107 частот, ключ 108, счетчик 109 импульсов и дешифратор 110 и блок 111 выделения кадрового синхроимпульса /КСИ/.

Каналы звукового сопровождения 112, 113 идентичны, применяются без изменений, как в прототипе, каждый включает преобразователь кодов звука в аналоговый сигнал /ЦАП/, усилитель мощности с фильтром низких частот и громкоговоритель.

Декодеры идентичны, каждый включает /фиг.9/ последовательно соединенные первый девятиразрядный регистр 114, накопитель 115 кодов кадра емкостью 200×103 девятиразрядных кодов /200 кодов × 1000 строк/, второй девятиразрядный регистр 116, первый блок 117 ключей из восьми ключей и третий восьмиразрядный регистр 118, последовательно соединенные второй блок 119 ключей из восьми ключей, восьмиразрядный вычитающий счетчик 120 импульсов и дешифратор 121, первый 122, второй 123, третий 124 и четвертый 125 ключи. Информационным входом декодера являются первый-девятый входы первого регистра 114, выходом являются первый-восьмой выходы третьего регистра 118. Управляющими входами являются: первым - объединенные управляющий вход регистра 114 и сигнальный вход /4,375 МГц/ третьего ключа 124, вторым - объединенные сигнальные входы /17,5 МГц/ ключей 122, 123, 125. Выход девятого разряда второго регистра 116 подключен параллельно к первому управляющему входу второго ключа 123, к вторым управляющим входам третьего 124 и четвертого 125 ключей и первого ключа 122, к второму управляющему входу первого блока ключей 117 и к первому управляющему входу второго блока 119 ключей. Выход первого ключа 122 подключен к первому управляющему входу /Uвыд1/ третьего регистра 118, второй управляющий вход /Uвыд2/ которого подключен к выходу второго ключа 123, к которому подключен и счетный вход вычитающего счетчика 120 импульсов, выход дешифратора 121 подключен параллельно к первому управляющему входу /Uот/ первого блока 117 ключей, к второму управляющему входу /Uз/ второго блока ключей 119, к первым управляющим входам ключей 122, 124, 125 и к второму управляющему входу /Uз/ второго ключа 123. Выход третьего ключа 124 подключен к управляющему входу /Uвыд/ накопителя 115 кодов кадра, выход четвертого ключа 125 подключен к управляющему входу /Uвыд/ второго регистра. Блоки 74, 79, 84, 92, 97, 102 удвоения /обработки/ кодов идентичны, каждый включает /фиг.10/ триггер 126, вход которого является управляющим входом блока 74, первый 127 и второй 128 блоки ключей /каждый из восьми ключей/, первый 129, второй 130, третий 131 и четвертый 132 регистры, сумматор 133, пятый 134 и шестой 135 регистры. выполняющие хранение кодов 57 нс и 16 диодов. Информационным входом блока 74 являются поразрядно объединенные первый-восьмой входы блоков 127, 128 ключей. Выходом являются поразрядно объединенные выходы 0-7 сумматора 133 и первый-восьмой выходы регистров 134, 135. Входы регистров 129, 130 поразрядно объединены и подключены к первому-восьмому выходам блока 127 ключей, выходы регистра 130 и 129 через диоды поразрядно объединены и подключены к первой группе входов сумматора 133. Входы регистров 131, 132 поразрядно объединены и подключены к первому-восьмому выходам второго блока 128 ключей, выходы регистра 132 и 131 через диоды поразрядно объединены и подключены к второй группе входов сумматора 133. Первый выход триггера 126 параллельно подключен к управляющим входам второго 130, третьего 131 и пятого 134 регистров и к управляющему входу первого блока 127 ключей. Второй выход триггера 126 подключен параллельно к управляющим входам первого регистра 129, четвертого 132 и шестого 135 регистров и к управляющему входу второго блока 128 ключей.

Накопители 75, 80, 85, 93, 98, 103 кодов кадра идентичны, каждый включает /фиг.11/ блоки 136 регистров по числу строк в кадре 1361-1000. Информационным входом накопителя кодов кадра являются поразрядно объединенные первый-восьмой входы всех блоков 136 регистров. Выходами являются выходы всех блоков регистров 136, всего выходов 11,2×106 /1400×8×1000/. Управляющими входами являются: первым - первый управляющий вход Uк /25 Гц/ первого блока 1361 регистров, вторым - объединенные вторые управляющие входы 25 кГц блоков 136 регистров, третьим - объединенные третьи входы /Uд/ блоков регистров 136. Управляющий выход каждого предыдущего блока регистров является первым управляющим входом для каждого последующего блока регистров. Управляющий первый выход последнего блока 1361000 регистров подключен параллельно к четвертым управляющим входам всех блоков 136 регистров. Блоки 136 регистров идентичны, каждый включает /фиг.12, 13/ первый 137 и второй 138 ключи, распределитель 139 импульсов и восемь регистров 1401-8, каждый из которых включает по 1400 разрядов, по числу отсчетов в строке. Информационными входами блока регистров являются поразрядно объединенные первый-восьмой третьи входы разрядов восьми регистров 140. Выходами являются параллельные выходы всех /1400/ разрядов восьми регистров 140, всего выходов с блока 136 регистров 11200 /1400×8/. Выходы 1000 блоков регистров 136 являются выходами каждого накопителя кодов кадра: 11,2×106. Управляющими входами блока 136 являются: первым - первый управляющий вход /Uк/ 25 Гц первого ключа 137, вторым - сигнальный вход 25 кГц /Uвыд/ второго ключа 138, третьим - сигнальный вход /Uд/ 35 МГц первого ключа 137. четвертым - первый управляющий вход /Uот/ второго ключа 138. Последний выход /1400/ распределителя 139 импульсов является первым управляющим выходом каждого блока 136 и подключен к первому управляющему входу первого ключа 137 в следующем блоке 136 регистров. Выход ключа 137 подключен к входу блока 139, выходы которого последовательно с первого по 1400-й подключены к первым /тактовым/ входам разрядов параллельно восьми регистров 140. Выход второго ключа 138 подключен параллельно к вторым входам разрядов восьми регистров 140 и к второму управляющему входу Uз своего ключа 138, прошедший импульс Uвыд закрывает ключ 138. Выходы накопителей 75, 80, 85, 93, 98, 103 кодов кадра подключены /фиг.6/ к информационным входам блоков 76, 81, 86, 94, 99, 104 импульсных усилителей, каждый из которых включает импульсных усилителей по числу разрешения кадра и по числу восьми разрядов в коде /1400×1000×8/, всего импульсных усилителей в блоке 11,2×106. С окончанием периода кадра 40 мс в накопителях кодов кадра сосредотачиваются все коды кадра 11,2×106×3 первого канала в блоках 75, 80, 85, а коды кадра второго канала сосредотачиваются в накопителях 93, 98, 103. С приходом сигнала с последнего блока 1361000 регистров /фиг.11/ все коды кадра из накопителей кодов кадра выдаются в блоки 76, 81, 86 и в блоки 94, 99, 104 импульсных усилителей, с выходов которых сигналы разрядов кодов /единицы кодов/ соответствующей амплитуды и длительностью 40 мс поступают параллельно на соответствующие входы своих плоскопанельных экранов 87, 105. Первый 87 и второй 105 плоскопанельные экраны идентичны, каждый включает элементы матриц по числу разрешения кадра 1400×1000. Элемент матрицы включает /фиг.16/ один микросветодиод 141 белого свечения и расположенные соответствующим образом три идентичные излучающие ячейки: первая 142 /левая/ излучает красный цвет R, вторая 143 /верхняя/ излучает зеленый цвет G, третья 144 /правая/ излучает синий цвет B. Каждая излучающая ячейка включает /фиг.17/ непрозрачный корпус 145, в переднем торце которого размещена микролинза 146, по оптической оси ее и последовательно друг за другом расположены с первого по восьмой нейтральные микросветофильтры 1471-8 с коэффициентами поглощения излучения в последовательности их расположения в порядке двоичного кода, включает с первого по восьмой микропьезоэлементы 1481-8, один торец каждого из них закреплен неподвижно в корпусе ячейки, второй свободный торец соответствующим образом соединен со своим нейтральным микросветофильтром 147. Управляющие входы микропьезоэлементов являются информационными входами излучающей ячейки и подключены к выходам соответствующих импульсных услителей в блоках 76, 81, 86 и 94, 99, 104. После восьмого микросветофильтра 1478 в выходном торце корпуса 145 ячейки размещен цветной светофильтр 149 одного из цветов R, G, B, оптическая ось которого является продолжением оси микролинзы 146. Излучающая плоскость микросветодиода 141 /фиг.16/ расположена в фокальных плоскостях трех микролинз 146. Излучение светодиода собирается микролинзой 146 и направляется на нейтральные микросветофильтры 147 ячейки. Принцип действия излучающей ячейки основан на том, что каждый последующий микросветофильтр 147 поглощает часть излучения соответственно своему коэффициенту поглощения, значения приведены в таблице 1, соответствуют принципу двоичного кода

| Таблица 1 | |||||||||

| Разряды кода | Исходное излучение | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| Вес разряда | 256 | 128 | 64 | 32 | 16 | 8 | 4 | 2 | 1 |

| Вес разряда в % | 100% | 50 | 25 | 12,5 | 6,25 | 3,125 | 1,562 | 0,78 | 0,39 |

| Плотность светоф. | 0х | 2х | 4х | 8х | 16х | 32х | 64х | 128х | 256х |

| Коэффициенты | 0,000 | 0,5 | 0,25 | 0,125 | 0,0625 | 0,031 | 0,0156 | 0,007 | 0,0039 |

Коэффициент поглощения первого микросветофильтра 1471 - 0,5 /первый разряд кода/, второго микросветофильтра 1472 - 0,25 /второй разряд кода/, третьего микросветофильтра 1473 - 0,125…1478 - 0,0039 /восьмой разряд кода/. В отсутствие управляющих сигналов /единиц кода/ на входах микропьезоэлементов 148 микросветофильтры перекрывают поток излучения от светодиода 141 /фиг.17/ до уровня ниже предела чуствительности зрения человека. При поступлении на микропьезоэлемент управляющего сигнала /импульс единицы кода/ свободный торец его совершает изгиб и поворачивает микросветофильтр 147 на 90° вниз /или вправо, влево/, поток излучения проходит без ослабления к следующему микросветофильтру 147. Внутренние поверхности корпуса 145 ячейки имеют светопоглощающее покрытие. В качестве пьезоэлементов применяются трубчатые пьезоэлементы, работающие на изгиб [10, с.27]. Значению 1 в коде соответствует открытое положение микросветофильтра 147, значению 0 в коде соответствует закрытое положение микросветофильтра 147 /как шлагбаум/. Яркость цветного излучения с выхода светофильтра 149 прямо пропорционально величине кода. На фиг.17 представлен момент преобразования кода 10110110 в яркость излучения. Выходом излучающей ячейки является выходное излучение после цветного светофильтра 149. Площадь каждого микросветофильтра 147 - порядка 15×15 мкм2. Излучающие ячейки не имеют электронных микросхем, выполняются микроэлектронным изделием с использованием микротехнологии. Непосредственное преобразование кодов в яркость излучения дает максимально возможную достоверность в цветопередаче на экранах 87, 105. Форма элемента матрицы из трех излучающих ячеек /фиг.16/ удобна для набора матрицы экранов разных размеров. Ячейки изготавливаются отдельно, по три объединяются в элемент матрицы, а из них набирается любого размера плоскопанельный экран. Точность преобразования кода в яркость каждой ячейкой зависит от точности соблюдения коэффициентов поглощения нейтральными светофильтрами во всех излучающих ячейках.

Результатом является полная достоверность цветопередачи 16777216 оттенков цветов, снижение инерционности элементов до микросекунд и выполнение тонких плоскопанельных экранов различных размеров. В качестве светодиодов белого излучения могут быть применены светодиоды по технологии СДТ /или PLЕД/ [11, с.43]. Блок 106 выделения строчных синхроимпульсов /ССИ/ и блок 111 выделения кадровых синхроимпульсов /КСИ/ идентичны, каждый включает /фиг.14/ счетчик 152 импульсов: дешифратор 153, элемент НЕ 154 и два диода Д1 и Д2. Счетчик 152 - пятиразрядный, ведет счет 27-и импульсов /код 11011/. Информационным входом блока 106 /111/ является счетный вход счетчика 152 импульсов, подключаемый к выходу первого формирователя 70 импульсов, управляющим входом является управляющий вход 2 счетчика 152, который через диод Д1 подключен к выходу второго формирователя 88 импульсов /фиг.6/. В блоке 111 информационный вход подключается к выходу блока 88, а управляющий вход подключается к выходу первого формирователя 70 импульсов. Управляющий вход в обоих блоках 106, 111 подключается также через диод Д2 к выходу элемента НЕ 154, вместе они подключены к управляющему входу счетчика 152 импульсов после диода Д1. Код ССИ является 27-и разрядным кодом из одних единиц и поступает на счетный вход блока 106 с формирователя 70 импульсов. Код КСИ является также 27-и разрядным кодом из одних единиц и поступает на счетный вход блока 111 с второго формирователя 88 импульсов.

Работа блоков 106, 111, фиг.14

С поступлением кода ССИ на счетный вход счетчика 152 он ведет счет 27 импульсов, следующих подряд. В результате на выходах 1, 2, 4, 5 разрядов счетчика появляются сигналы, которые дешифруются блоком 153, и на выходе блока 106 /111/ появляется строчный синхроимпульс ССИ /КСИ/. При поступлении импульсов кода ССИ на счетный вход счетчика 152 с выхода блока 88 /фиг.6/ импульсов нет. Начиная со второго кода строки с блока 88 пойдут коды на управляющий вход счетчика 152, и с приходом каждого импульса /единицы кода/ счетчик 152 будет обнуляться и не сможет достигнуть счета 27. Параллельно на счетный вход счетчика 152 также идут коды с блока 70, в которых есть и единицы, и нули, а по каждому нулю элемент НЕ 154 выдает импульс, обнуляющий счетчик 152, в добавление при выходе импульса ССИ с блока 153 он через диод Д2 поступает также на управляющий вход счетчика 152 и обнуляет его. Таким образом, схема блока 106 /111/ исключает появление на выходе ложного сигнала ССИ /КСИ/. В блок 111 при поступлении с блока 88 кода КСИ на счетный вход счетчика 152 на выходах 1, 2, 4, 5 его разрядов появляется код, дешифруемый блоком 153, и на выходе блока 111 появляется синхроимпульс КСИ 25 Гц. Работа блока 111 аналогична работе блока 106.

ФЭП 1 первого телеканала матрицей ПЗИ 3 формирует три аналоговых сигнала основных цветов R1, G1, B1. Объектив 2 создает изображение в фокальной плоскости, в которой расположена фоточувствительная сторона матрицы ПЗИ 3. На каждый из трех слоев матрицы ПЗИ 3 с ключа 30 поступают импульсы 25 кГц частоты строк для считывания сигналов пикселов по вертикали, на второй вход матрицы ПЗИ с ключа 31 поступают импульсы 17,5 МГц для считывания сигналов пикселов по горизонтали [3, c.832]. Аналоговые видеосигналы с ПЗИ 3 поступают на входы предварительных усилителей 4, 5, 6, с выходов которых поступают на входы соответственно АЦП 13, 14, 15, с выходов которых восьмиразрядные коды цветовых сигналов с дискретизацией 17,5 МГц поступают на входы своих кодеров 21, 22, 23. Синхронизация считывания сигналов с матрицы ПЗИ выполняется сигналом частоты кадров 25 Гц, открывающим ключи 30, 31 в начале каждого кадра на 40 мс. Второй ФЭП 7 работает аналогично и синхронно с ФЭП 1, во втором ФЭП 7 идентичная матрица ПЗИ 9, считывание сигналов пикселов с нее идет импульсами с ключей 30, 31. Аналоговые сигналы с ПЗИ 9 поступают на входы предварительных усилителей 10, 11, 12, с которых они поступают на входы АЦП 17, 18, 19, с выходов которых восьмиразрядные коды сигналов R2, G2, B2 с дискретизацией 17,5 МГц поступают на входы кодеров 24, 25, 26. Синтезатор 29 частот выдает с первого выхода импульсы 17,5 МГц дискретизации кодов в АЦП 13-15 и 17-19 и на сигнальный вход ключа 31, со второго выхода импульсы 4,375 МГц Uвыд с кодеров 21-26, с третьего выхода импульсы 75 кГц дискретизации кодов звука, с четвертого - тактовые синусоидальные колебания 118,125 МГц на второй управляющий вход формирователя 27 кодов, с пятого - импульсы частоты строк 25 кГц на сигнальный вход ключа 30 и на третий управляющий вход блока 27 и на третьи управляющие входы АЦП 16, 20, с шестого - импульсы 25 Гц частоты кадров на управляющие входы ключей 30, 31 и в СРИ 33, с седьмого - синусоидальные колебания несущей частоты 1771,875 МГц со стабильностью 10-7 в передатчик 34 радиосигналов. АЦП 13-15, 17-19 преобразуют аналоговые видеосигналы первого и второго телеканалов в восьмиразрядные коды, поступающие в параллельном виде в кодеры 21-23 первого канала и 24-26 второго канала.

Работа кодеров, фиг.3, 4

Коды в параллельном виде поступают на входы регистра 38, на первые входы схемы сравнения 39 и на входы блока 42 элементов задержек. Исходное состояние ключей в блоке 43 открытое. Код в блоке 42 задерживается на время срабатывания схемы сравнения /18 нс/ и поступает через открытые ключи блока 43 на входы буферного накопителя 44 кодов емкостью 200×103 девятиразрядных кодов. Схема сравнения 39 выполняет сравнение по величине каждого предыдущего и последующего кодов с целью выявления их равенства или неравенства. При следовании неравных кодов они проходят через блок 42, открытые ключи блока 43 и поступают на первый-восьмой входы буферного накопителя 44 кодов. Выдача кодов из блока 44 выполняется сигналами Uвыд 4,375 МГц. Поступление кодов в блок 44 при следовании неравных кодов идет с частотой 17,5 МГц. В общем потоке кодов имеется большое число и равных по величине кодов. Кодер выполняет сжатие потока кодов с плавающим коэффициентом от 1 до 255. Общий коэффициент сжатия потока кодов за кадр принимается не менее 4, поэтому частота выдачи кодов с блока 44 и принимается 4,375 МГц //. При коэффициенте выше 4 частота выдачи 4,375 МГц будет тем более удовлетворять. Схема сравнения выполняет сравнение кодов по величине и представляется двумя микросхемами 530 СП1 с временем срабатывания 18 не [12, c.279]. При неравенстве кодов A>B появляется сигнал на выходе 2 блока 39 /в микросхеме выход 5 [12, с.272, рис.2.190], при равенстве кодов A=B появляется сигнал с выхода 1 /в микросхеме выход 7/. При равенстве кодов сигнал с выхода 1 блока 39 закрывает ключи в блоке 43, поступает счетным импульсом в счетчик 40 импульсов и как сигнал Uвыд на первый управляющий вход регистра 38. Счетчик 40 производит счет импульсов с выхода 1 блока 39 пока идут коды, равные по величине. Счетчик 40 - восьмиразрядный, максимальный код в нем 11111111 /255/, отсюда и максимальный коэффициент сжатия 255. Счетчик из микросхем К531ИЕ160 с временем срабатывания 8 нс [12, с.248]. При появлении неравных кодов A<B со схемы 39 сравнения следует сигнал с выхода 2 или 3, которые объединены, сигнал с них используется для выдачи кода числа равных кодов из счетчика 40 через диоды на первый-восьмой входы блока 44 и для заполнения в блоке 44 девятого разряда, с которого сигнал используется для опознания по нему кода числа равных кодов при декодировании. Этот же сигнал открывает ключи в блоке 43 /вход 1/ и обнуляет регистр 38 /вход 2/. Выданный перед этим с блока 44 код является первым кодом последовательности, на диаграмме 1 фиг.4 они помечены крестиками. Коды, равные по величине и подсчитанные счетчиком 40, исключаются из потока /диаграмма 111 фиг.4/, за счет их и идет сжатие. Емкость буферного накопителя 44 кодов соответствует числу 9-и разрядных кодов в кадре: 200×103 для обеспечения темпа следования с частотой 4,375 МГц. При следовании подряд кодов, равных по величине, более 255 в работу вступает дешифратор 41. При коде 11111111 дешифратор 41 выдает сигнал, который параллельно открывает ключи в блоке 43 /вход 1/, обнуляет регистр 38, сигналом Uвыд выдает код из счетчика 40 /вход 1/ и обнуляет его /вход 2/, а в девятый разряд блока 44 поступает сигнал опознания кода числа равных кодов. Пропускная способность кодера определяется временем срабатывания схемы сравнения 39, которая обеспечивает до 40 Мбайт/с, и удовлетворяет требуемой 17,5 Мбайт/с. С выходов кодеров 21-26 коды в параллельном виде поступают на первый и второй информационные входы формирователя 27 кодов, который /фиг.5/ первым кодом в строке выдает код ССИ /фиг.2/, а из сжатых потоков кодов R1, G1, B1 первого канала и кодов R2, G2, B2 второго канала формирует с №2 по №197 коды одного потока и затем три кода сигналов звука 3в1, 3в2 /фиг.2/. Код КСИ является первым кодом только в первой строке каждого кадра, при этом импульсов кода ССИ нет. Код ССИ является первым кодом в каждой строке, начиная со второй строки кадра, при этом нет импульсов других кодов. Единицы кодов первого телеканала R1, G1, B1 представляются на выходе блока 27 положительными полусинусоидами моночастоты 118,125 МГц, единицы в кодах второго телеканала R2, G2, B2 представляются на выходе блока 27 отрицательными полусинусоидами той же моночастоты.

Работа формирователя 27 кодов, фиг.5

Временные диаграммы работы блока 27 на фиг.15. Блок 27 преобразует параллельные коды в последовательные и заменяет в них представление единиц с импульсов на положительные и отрицательные полусинусоиды: положительные - коды первого телеканала, отрицательные - коды второго телеканала. На первый информационный вход в блок 45 элементов И поступают 9-и разрядные коды с кодеров 21-23, на второй информационный вход в блок 50 элементов И поступают 9-и разрядные коды с кодеров 24-26, на третий информационный вход в блок 55 поступают 16-и разрядные коды звука с АЦП 16, на четвертый информационный вход в блок 58 элементов И поступают 16-и разрядные коды звука АЦП 20, на пятый информационный вход поступает в последовательном виде 27-и разрядный код ССИ с блока 32 в ключ 63, на шестой информационный вход поступает последовательный 27-и разрядный код КСИ с блока 33 на третий вход элемента ИЛИ 52. На вторые входы элементов И 45, 50 поступают последовательно 27 импульсов с выходов СРИ 49, 54, сигнал Uп пуска на которые поступает с первого ключа 61. С выходов блоков 45, 50 импульсы кодов последовательно через элементы ИЛИ 46, 47 и 51, 52 поступают на управляющие входы соответственно выходных ключей 48, 53 и открывают их на время своей длительности 8,5 нс . Выходной ключ 48 в открытом состоянии пропускает одну положительную полусинусоиду на выход, выходной ключ 53 в открытом состоянии пропускает на выход одну отрицательную полусинусоиду. Выходы ключей 4