Модуль коммутационной сети

Иллюстрации

Показать всеИзобретение относится к автоматике и вычислительной технике и может быть использовано при построении коммутационных средств вычислительных, управляющих и информационно-измерительных систем, а также абонентских систем связи с децентрализованным управлением. Техническим результатом изобретения является расширение области применения устройства за счет введения средств для приоритетной передачи сообщений в зависимости от их срочности. В каждый блок организации очереди сообщений модуля коммутационной сети известного устройства, содержащего с первого по третий блоки организации очереди сообщений, регистр идентификатора модуля, блок анализа очередей сообщений, мультиплексор, регистр, демультиплексор, триггер, блок синхронизации, первый и второй элементы сравнения, первый дешифратор, второй дешифратор и элемент И, дополнительно введены (k-1) элементов сравнения, первая группа из (k-1) блоков элементов И, второй элемент задержки, элемент ИЛИ, вторая группа из (k-1) блоков элементов И, первая группа из (k-1) элементов И, вторая группа из (k-1) элементов И, третья группа из (k-1) элементов И, четвертая группа из (k-1) элементов И. 6 ил.

Реферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении коммутационных средств вычислительных, управляющих и информационно-измерительных систем, а также абонентских систем связи с децентрализованным управлением.

Известно устройство-модуль матричного коммутатора, содержащий три блока организации очередей сообщений, регистр идентификатора модуля, блок анализа очереди сообщений, мультиплексор, регистр, демультиплексор, триггер, блок синхронизации, первый и второй элементы сравнения, первый и второй дешифраторы, элемент И (а.с. 1575167 СССР, G06F 7/00, 15/16; опубл. 30.06.90; БИ N24).

Недостатком указанного модуля является узкая область применения в силу высокой аппаратной сложности блока организации очереди сообщений.

Наиболее близким к предлагаемому модулю по технической сущности является модуль коммутационной сети, содержащий три блока организации очередей сообщений, регистр идентификатора модуля, блок анализа очереди сообщений, мультиплексор, регистр, демультиплексор, триггер, блок синхронизации, первый и второй элементы сравнения, первый и второй дешифраторы, элемент И (патент RU №2175146, МПК G06 7/00, опубл. 20.10.2001).

Недостатком указанного модуля является ограниченная область применения, обусловленная отсутствием средств для приоритетной передачи (коммутации) сообщений в зависимости от их срочности, что приводит к неоправданным задержкам срочных сообщений.

Технической задачей изобретения является расширение области применения устройства за счет введения средств для приоритетной передачи сообщений в зависимости от их срочности.

Техническая задача решается тем, что в каждый блок организации очереди сообщений модуля коммутационной сети, содержащего с первого по третий блоки организации очереди сообщений, регистр идентификатора модуля, блок анализа очередей сообщений, мультиплексор, регистр, демультиплексор, триггер, блок синхронизации, первый и второй элементы сравнения, первый дешифратор, второй дешифратор и элемент И, причем первый управляющий выход блока анализа очередей сообщений соединен со входом первого дешифратора и управляющим входом мультиплексора, выход которого соединен с информационным входом регистра, первая группа выходов которого соединена с первым входом первого элемента сравнения, вторая группа выходов регистра соединена с первым входом второго элемента сравнения, первая, вторая и третья группы выходов регистра соединены с информационным входом демультиплексора, выходы которого с первого по третий являются выходами модуля с первого по третий соответственно, второй управляющий выход блока анализа очередей сообщений соединен с входом установки триггера и первым входом элемента И, выход которого подключен к входу сброса триггера, прямой выход которого подключен ко входу запуска блока синхронизации, первый выход которого подключен к входу синхронизации регистра и входу синхронизации регистра идентификатора модуля, первая группа выходов которого соединена со вторым входом первого элемента сравнения, выход которого соединен с первым входом второго дешифратора, вторая группа выходов регистра идентификатора модуля соединена со вторым входом второго элемента сравнения, выход которого подключен ко второму входу второго дешифратора, выход которого подсоединен к управляющему входу демультиплексора, третий выход блока синхронизации соединен со вторым входом элемента И и с информационным входом демультиплексора, входы модуля с первого по третий соединены с информационными входами блоков организации очереди сообщений с первого по третий соответственно, информационные выходы блоков организации очереди сообщений с первого по третий подключены к входам мультиплексора с первого по третий соответственно, управляющие выходы блоков организации очереди сообщений с первого по третий подключены к входам блока анализа очередей сообщений с первого по третий соответственно, второй выход блока синхронизации подсоединен к входам синхронизации блоков организации очереди сообщений с первого по третий, выходы первого дешифратора с первого по третий подключены ко входам опроса блоков организации очереди сообщений с первого по третий соответственно, каждый блок организации очереди сообщений включает k регистров (где k - максимальная длина очереди сообщений), k-1 блоков элементов ИЛИ, группу из k элементов И, группу из k элементов ИЛИ, регистр длины очереди, элемент И, элемент ИЛИ, элемент задержки, причем первый разряд информационного входа блока подключен к первым входам элементов И группы с первого по k-й и первому входу элемента ИЛИ, выход которого подсоединен к входу элемента задержки, выход которого подключен к входу синхронизации регистра длины очереди, выход которого подсоединен к управляющему выходу блока, выходы блоков элементов ИЛИ с первого по (k-1)-й подключены к информационным входам регистров с первого по (k-1)-й соответственно, выходы регистров с второго по k-й соединены с вторыми входами блоков элементов ИЛИ с первого по (k-1)-й соответственно, выход первого регистра соединен с информационным выходом блока, выходы элементов И группы с первого по k-й соединены с первыми входами элементов ИЛИ группы с первого по k-й соответственно, выходы которых подключены к входам синхронизации регистров с первого по k-й соответственно, вход синхронизации и вход опроса блока подключены соответственно к первому и второму входам элемента И, выход которого подключен к вторым входам элементов ИЛИ группы с первого по k-й и второму входу элемента ИЛИ, блок элементов И, группа из k элементов ИЛИ-НЕ, элемент И-НЕ, причем с второго по (m+1)-й разряды информационного входа блока (m - разрядность кода сообщения) подключены к первому входу блока элементов И, выход которого подключен к информационному входу k-го регистра и к первым входам блоков элементов ИЛИ с первого по (k-1)-й, выход элемента И соединен с вторым входом блока элементов И, выходы регистров с первого по k-й соединены с входами элементов ИЛИ-НЕ группы с первого по k-й соответственно, выходы которых подсоединены к вторым входам элементов И группы с первого по k-й соответственно, входу элемента И-НЕ и информационному входу регистра длины очереди, выходы элементов ИЛИ-НЕ группы с первого по (k-1)-й соединены с третьими входами элементов И группы с второго по k-й соответственно, выход элемента И-НЕ подключен к управляющему выходу блока, дополнительно введены (k-1) элементов сравнения, первая группа из (k-1) блоков элементов И, второй элемент задержки, элемент ИЛИ, вторая группа из (k-1) блоков элементов И, первая группа из (k-1) элементов И, вторая группа из (k-1) элементов И, третья группа из (k-1) элементов И, четвертая группа из (к-1) элементов И, причем первые входы каждого из (k-1) элементов сравнения подключены к выходам соответствующих (k-1) регистров, соединенных с информационными входами первой группы из (k-1) блоков элементов И, а вторые входы к выходу блока элементов И, выходы каждого из (k-1) элементов сравнения подключены к прямому входу соответствующего элемента И третьей группы из (k-1) элементов И, инверсный вход которого подключен к инверсному выходу элемента ИЛИ, при этом выход (i)-го элемента третьей группы подключен к прямому (управляющему) входу i-ro блока элементов И первой группы, инверсному (управляющему) входу (i-1)-го блока элементов И второй группы, ко входу i-го элемента И четвертой группы, на второй вход которого подается первый разряд информационного входа блока, а выход подключен к первому дополнительному входу i-го элемента ИЛИ в группе из к элементов ИЛИ, выходы элементов И второй группы подключены к первым входам первой группы из (k-1) элементов И, вторые входы которых подключены к выходу дополнительно введенного второго элемента задержки, на вход которого подается первый разряд информационного входа блока, выходы первой группы дополнительно введенных (k-1) элементов И подключены к вторым дополнительным входам элемента ИЛИ в группе из к элементов ИЛИ за исключением первого, выход i-го блока элементов И первой группы подключен к дополнительно введенным входам (i+1) элемента ИЛИ из состава k-1 блоков элементов ИЛИ, а также дополнительно введенного элемента ИЛИ, выход которого подключен к информационному входу k-го регистра.

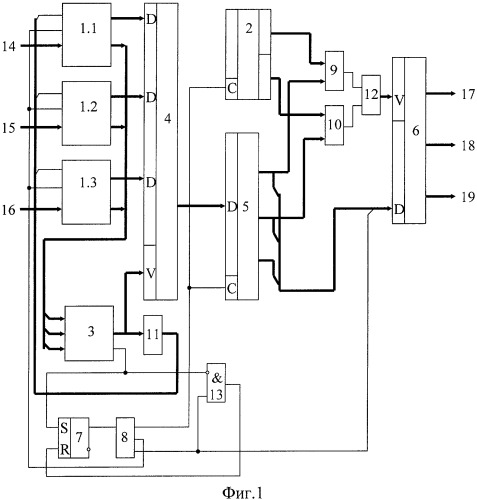

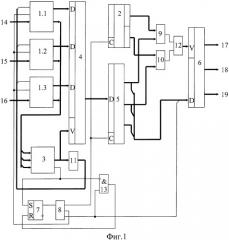

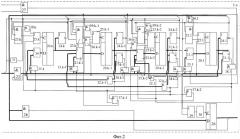

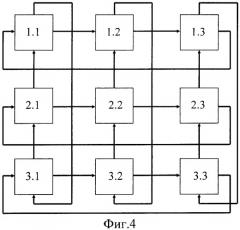

Сущность изобретения поясняется чертежами, где на фиг.1 представлена функциональная схема модуля коммутационной сети; на фиг.2 изображена функциональная схема блока организации очереди сообщений; на фиг.3 дана функциональная схема блока анализа очередей сообщений; на фиг.4 показана структура коммутационной сети из девяти модулей; на фиг.5 приведен формат сообщения, на фиг.6 проиллюстрирован принцип передачи приоритетных сообщений.

Общие особенности предлагаемого изобретения состоят в следующем.

Предлагаемый модуль совместно с другими аналогичными модулями образует коммутационную сеть (структуру) обмена сообщениями. Сеть представляет собой однородную матрицу, каждый модуль которой соединен с двумя соседними модулями по входу и с двумя соседними модулями по выходу. Каждому модулю сети присваивается идентификатор (адрес), состоящий из двух кодов, определяющих местоположение модуля в матрице. Первый код соответствует номеру строки, второй код - номеру столбца (фиг.4). Аналогичные коды включаются в адресную часть сообщения для идентификации приемников сообщений (фиг.5).

Передача информации между любыми модулями сети осуществляется по минимальному физическому пути через другие модули (транзитным способом). Поступающие в модуль сообщения заносятся в блоки организации очереди сообщений (фиг.2).

В прототипе очереди сообщений на обработку формируется в блоках организации очереди сообщений в зависимости от времени их поступления на вход устройства и не обеспечивают приоритетной передачи (коммутации) сообщений в зависимости от их срочности.

Для обеспечения приоритетной передачи (коммутации) сообщений поступившее сообщение с более высоким приоритетом должно быть обслужено раньше сообщений, уже находящихся в очереди но с более низким приоритетом. Принцип работы предлагаемого устройства поясняется на фиг.6. Здесь на фиг.6,а,б показаны гипотетические очереди сообщений. Каждому сообщению, находящемуся в очереди, соответствует свой номер приоритета, показанный сверху над каждым сообщением. Например в очередь, показанную на фиг.6,а поступает новое сообщение Y с приоритетом 18. В этом случае оно должно попасть в очередь между сообщениями Б и С с приоритетами 20 и 15 соответственно. Тогда очередь приобретает вид, показанный на фиг.6,б. Технически это означает, что все сообщения в очереди с приоритетом, меньшим приоритета нового сообщения, должны быть сдвинуты влево, а новое сообщение должно быть записано на освободившееся место.

Модуль коммутационной сети (фиг.1) содержит блоки 1.1-1.3 организации очереди сообщений, регистр 2 идентификатора модуля, блок 3 анализа очередей сообщений, мультиплексор 4, регистр 5, демультиплексор 6, триггер 7, блок 8 синхронизации, первый элемент 9 сравнения и второй элемент 10 сравнения, первый дешифратор 11, второй дешифратор 12 и элемент И 13, причем первый управляющий выход блока 3 анализа очередей сообщений соединен со входом дешифратора 11 и управляющим входом мультиплексора 4, выход которого соединен с информационным входом регистра 5, первая группа выходов которого соединена с первым входом элемента 9 сравнения, вторая группа выходов регистра 5 соединена с первым входом элемента 10 сравнения, первая, вторая и третья группы выходов регистра 5 соединены с информационным входом демультиплексора 6, выходы которого с первого по третий являются выходами 17-19 модуля соответственно, второй управляющий выход блока 3 анализа очередей сообщений соединен с входом установки триггера 7 и первым входом элемента И 13, выход которого подключен к входу сброса триггера 7, прямой выход которого подключен ко входу запуска блока 8 синхронизации, первый выход которого подключен к входу синхронизации регистра 5 и входу синхронизации регистра 2 идентификатора модуля, первая группа выходов которого соединена со вторым входом элемента 9 сравнения, выход которого соединен с первым входом дешифратора 12, вторая группа выходов регистра 2 идентификатора модуля соединена со вторым входом элемента 10 сравнения, выход которого подключен ко второму входу дешифратора 12, выход которого подсоединен к управляющему входу демультиплексора 6, третий выход блока 8 синхронизации соединен со вторым входом элемента И 13 и с информационным входом демультиплексора 6, входы 14-16 модуля соединены с информационными входами блоков 1.1-1.3 организации очереди сообщений соответственно, информационные выходы блоков 1.1-1.3 организации очереди сообщений подключены к входам мультиплексора 4 с первого по третий соответственно, управляющие выходы блоков 1.1-1.3 организации очереди сообщений подключены ко входам блока 3 анализа очередей сообщений с первого по третий соответственно, второй выход блока 8 синхронизации подсоединен к входам синхронизации блоков 1.1-1.3 организации очереди сообщений, выходы дешифратора 11 с первого по третий подключены ко входам опроса блоков 1.1-1.3 организации очереди сообщений соответственно.

Блок 1.s организации очереди сообщений (s=1, 2, 3) (фиг.2) содержит регистры 20.1-20.k, блоки элементов ИЛИ 21.1-21.k-1, элементы И 23.1-23.k, элементы ИЛИ 25.1-25.k, регистр 26 длины очереди, элемент И 27, элемент ИЛИ 29, элемент задержки 30, блок элементов И 22, элементы ИЛИ-НЕ 24.1 -24.k, элемент И-НЕ 28, причем первый разряд информационного входа блока подключен к первым входам элементов И 23.1-23.k и первому входу элемента ИЛИ 29, выход которого подсоединен к входу элемента 30 задержки, выход которого подключен к входу синхронизации регистра 26, выход которого подсоединен к управляющему выходу блока, выходы блоков элементов ИЛИ 21.1-21.k-1 подключены к информационным входам регистров 20.1-20.k-1, выходы регистров 20.2-20.k соединены с вторыми входами блоков элементов ИЛИ 21.1-21.k-1 соответственно, выход регистра 20.1 соединен с информационным выходом блока, выходы элементов И 23.1-23.k соединены с первыми входами элементов ИЛИ 25.1-25.k соответственно, выходы которых подключены к входам синхронизации регистров 20.1-20.k соответственно, вход синхронизации и вход опроса блока подключены соответственно к первому и второму входам элемента И 27, выход которого подключен к вторым входам элементов ИЛИ 25.1-25.k и второму входу элемента ИЛИ 29, причем с второго по (m+1)-й разряды информационного входа блока подключены к первому входу блока элементов И 22, выход элемента И 27 соединен с вторым входом блока и элементов И 22, выходы регистров 20.1-20.k соединены с входами элементов ИЛИ-НЕ 24.1-24.k соответственно, выходы которых подсоединены к вторым входам элементов И 23.1-23.k соответственно, входу элемента И-НЕ 28 и информационному входу регистра 26, выходы элементов ИЛИ-НЕ 24.1-24.k-1 соединены с третьими входами элементов И 23.2-23.k соответственно, выход элемента И-НЕ 28 подключен к управляющему выходу блока, а также дополнительно введенную группу 31.1, 31.2, …, 31 k-1 элементов сравнения, первую 32.1, 32.2, …, 32.k-1 группу блоков элементов И, второй 33 элемент задержки, элемент ИЛИ 34, вторую 35.1, 35.2, …, 35.k группу блоков элементов И, первую 36.1, 36.2, …, 36.k-1 группу элементов И, вторую 37.2. 37.3, …, 37.k-1 группу элементов И, третью 38.1, 38.2,…, 38.k-1 группу элементов И, четвертую 39.2, 39.3, …, 39.k группу элементов И, причем первые входы 31.1, 31.2, … 31.k-1 элементов сравнения подключены к выходам соответствующих 20.1-20.k регистров, соединенных с информационными входами первой группы 32.1, 32.2, …, 32.k-1 блоков элементов И, а вторые входы - к выходу 22 блока элементов И, выходы каждого 31.1, 31.2, …, 31.k-1 элемента сравнения подключены к прямому входу соответствующего элемента И третьей группы 38.1, 38.2,…, 38.k-1 элементов И, инверсный вход которого подключен к выходу соответствующего элемента ИЛИ-НЕ 24.1-24.k-1, при этом выходы элементов третьей группы 38.1, 38.2, …, 38.k-1 подключены к управляющим входам 32.1, 32.2,…, 32.k-1 блоков элементов И первой группы, инверсному (управляющему) входам 35.1, 35.2, …, 35.k блоков элементов И второй группы, ко входам 39.2, 39.3, …, 39.k элементов И четвертой группы, на второй вход которых подается первый разряд информационного входа блока, а выходы подключены к первым дополнительным входам 25.1-25.k элементов ИЛИ, выходы элементов И 37.2, 37.3, 37.k-1 второй группы подключены к первым входам первой группы 36.1, 36.2, 36.k-1 элементов И, вторые входы которых подключены к выходу дополнительно введенного второго элемента задержки 33, на вход которого подается первый разряд информационного входа блока, выходы первой группы дополнительно введенных 36.1, 36.2, … 36.k-1 элементов И, подключены к вторым дополнительным входам элемента ИЛИ 25.2-25.k, выходы 32.1, 32.2, …, 32.k-1 блоков элементов И первой группы подключены к дополнительно введенным входам 21.1-21.k-1 элементов ИЛИ, а также дополнительно введенного элемента ИЛИ 34, выход которого подключен к информационному входу 20.k-го регистра.

Блок 3 анализа очередей сообщений (фиг.3) содержит с первого по третий элементы 40-42 сравнения, узел 43 постоянной памяти, элемент ИЛИ 44, причем первые разряды с первого по третий входы блока подключены соответственно к первому, второму и третьему входам элемента ИЛИ 44, разряды со второго по (k+1)-й первого входа блока подключены к первому входу элемента 40 сравнения и к второму входу элемента 42 сравнения, разряды с второго по (k+1)-й второго входа блока подключены к первому входу элемента 41 сравнения и к второму входу элемента 40 сравнения, разряды с второго по (k+1)-й третьего входа блока подключены к первому входу элемента 42 сравнения и к второму входу элемента 41 сравнения, первые, вторые, третьи выходы элементов 40-42 сравнения подсоединены к соответствующим входам узла 43 постоянной памяти, выход которого подключен к первому управляющему выходу блока, второй управляющий выход блока подсоединен к выходу элемента ИЛИ 44.

Назначение элементов модуля коммутационной сети (фиг.1) состоит в следующем.

Блоки 1.1-1.3 организации очереди сообщений предназначены для организации очередей сообщений, поступающих от двух соседних модулей и собственного операционного устройства.

Регистр 2 идентификатора модуля предназначен для хранения адреса (идентификатора), определяющего местонахождение модуля в пределах коммутационной сети.

Блок 3 анализа очередей сообщений предназначен для анализа соотношения текущих длин очередей сообщений в блоках 1.1-1.3 организации очереди сообщений и организации опроса указанных блоков в зависимости от длины очереди поступивших сообщений, а также для формирования сигнала управления триггером 7.

Мультиплексор 4 предназначен для коммутации информационных выходов блоков 1.1-1.3 организации очереди сообщений с регистром 5 в зависимости от кода, поступающего из блока 3 анализа очередей сообщений.

Регистр 5 предназначен для хранения адресной и информационной части сообщения во время выбора направления его дальнейшей передачи.

Демультиплексор 6 предназначен для коммутации сообщения собственному операционному устройству или соседним модулям в одном из двух направлений.

Триггер 7 предназначен для формирования сигнала запуска блока 8 синхронизации.

Блок 8 синхронизации предназначен для формирования трех сдвинутых относительно друг друга последовательностей импульсов t1, t2, t3 для синхронизации работы модуля.

Первый 9 и второй 10 элементы сравнения предназначены для сравнения адресной части поступившего на обслуживание сообщения с адресом данного модуля.

Первый дешифратор 11 предназначен для преобразования кода опроса, выдаваемого блоком 3 анализа очередей сообщений, в соответствующий унитарный код.

Второй дешифратор 12 предназначен для формирования кода, определяющего направление выдачи сообщения.

Элемент И 13 предназначен для формирования управляющего сигнала, сбрасывающего триггер 7 в нулевое состояние, при отсутствии сообщений в блоках 1.1-1.3 организации очереди сообщений.

Входы 14, 15, 16 модуля предназначены для приема сообщений от собственного операционного устройства и двух соседних модулей коммутационной сети соответственно.

Выходы 17, 18, 19 модуля предназначены для передачи сообщений собственному операционному устройству и двум соседним модулям коммутационной сети соответственно.

Назначение элементов блока 1.s организации очереди сообщений (s=1, 2, 3) (фиг.2) состоит в следующем.

Регистры 20.1-20.k предназначены для хранения очереди поступающих на обслуживание сообщений.

Блоки 21.1-21.k-1 элементов ИЛИ предназначены для подключения информационных входов регистров 20.1-20.k-1 к выходу блока элементов И 22 и к выходам регистров 20.2-20.k соответственно при приеме сообщения или сдвиге очереди сообщений к выходу, а также для сдвига сообщений от выхода, находящихся в очереди в случае поступления более приоритетного сообщения (фиг.6).

Блок 22 элементов И предназначен для блокировки прохождения информации на информационные входы регистров 20.1-20.k в процессе сдвига очереди сообщений.

Элементы И 23.1-23.k, так же как и в прототипе, предназначены для разрешения или запрещения передачи импульса записи с информационного входа блока организации очереди сообщений на первые входы элементов ИЛИ 25.1-25.k, что обеспечивает формирование очереди сообщений в зависимости от времени их поступления.

Элементы ИЛИ-НЕ 24.1-24.k предназначены для формирования признаков наличия сообщения в регистрах, соответственно образующих код текущей длины очереди сообщений.

Элементы ИЛИ 25.1-25.k предназначены для передачи импульсов на входы синхронизации регистров 20.1-20.k при поступлении нового сообщения и в ходе сдвига очереди сообщений.

Регистр 26 длины очереди предназначен для хранения кода текущей длины очереди сообщений.

Первый 27 элемент И предназначен для блокировки передачи импульса с входа синхронизации блока организации очереди сообщений на вторые входы элементов ИЛИ 25.1-25.k, на второй вход блока элементов И 22 и на второй вход элемента ИЛИ 29.

Элемент И-НЕ 28 предназначен для формирования сигнала наличия сообщений в блоке организации очереди сообщений.

Первый элемент ИЛИ 29 предназначен для формирования сигнала, управляющего записью информации в регистр 26.

Первый элемент 30 задержки предназначен для задержки сигнала управления записью информации в регистр 26 на время, необходимое для установки нового кода длины очереди сообщений.

Группа 31.1, 31.2, …, 31.k-1 элементов сравнения предназначена для сравнения приоритета сообщений, находящихся в очереди с величиной приоритета поступившего сообщения.

Первая группа 32.1, 32.2, …, 32.k-1 элементов И служит для разрешения передачи сообщений с выхода j-го регистра на вход (j-1)-го регистра по результатам сравнения приоритетов в 31.1, 31.2, 31.k-1 элементах сравнения.

Второй элемент 33 задержки необходим для задержки единичного сигнала на время, достаточное для поступления кода сообщения на D-вход регистра 20.j (j=2, …, k) с выхода (j+1)-го регистра.

Элемент ИЛИ 34 предназначен для объединения сигналов с выходов элемента 32.k-1 И и элемента И 35.k с последующей подачей на D-вход регистра 20.k.

Вторая группа 35.1, 35.2, …, 35.k-1 блоков элементов И предназначена для коммутации сообщений с выхода блока элементов 22 И на D-входы соответствующих регистров по результатам сравнения приоритетов в 31.1, 31.2, …, 31.k-1 элементах сравнения.

Первая группа 36.2, 36.3, …, 36.k-1 элементов И предназначена для объединения сигналов с выхода элемента 33 задержки и с соответствующих выходов элементов четвертой 37.2, 37.3, …, 37.k-1 группы элементов И.

Вторая группа 37.2, 37.3, …, 37.k-1 элементов И служит для разрешения прохождения единичного сигнала на синхровход одного из регистров 20.2, …, 20.k., в который помещается входное сообщение по результатам сравнения его приоритета и приоритетов сообщений из очереди.

Третья 38.1, 38.2, …, 38.k-1 группа элементов И запрещает действия по результатам сравнения приоритета при отсутствии сообщения в регистре.

Четвертая 39.2, 39.3, …, 39.k группа элементов И служит для разрешения подачи единичного импульса записи на входы регистров 20.1-20.k через соответствующие элементы ИЛИ 25.1-25.k, что обеспечивает сдвиг сообщений в очереди влево.

Назначение элементов блока 3 анализа очередей сообщений (фиг.3) не отличается от прототипа и поэтому здесь не рассматривается.

Рассмотрим работу предлагаемого устройства. Учитывая, что модуль предназначен для работы в составе однородной коммутационной сети, его функционирование будем рассматривать во взаимосвязи с другими аналогичными модулями. Структура сети на базе предлагаемого модуля, содержащей девять идентичных модулей, представлена на фиг.4.

В начальный момент времени в блоках 1.1-1.3 организации очереди сообщений (фиг.1) сообщения отсутствуют, состояние регистров 20.1-20.k и 26 (фиг.2) нулевое, на прямом выходе триггера 7 находится уровень логического нуля, блокирующий формирование импульсов блоком 8 синхронизации. В регистре 5 сообщение отсутствует. В регистре 2 идентификатора модуля хранится адрес i.j текущего модуля, где i и j - номер соответственно строки и столбца коммутационной сети (фиг.4), содержащих модуль. Цепи начальной установки на фиг.1, 3, 4 не показаны с целью упрощения.

Работа модуля начинается в момент поступления нового сообщения (формат сообщения изображен на фиг.5). В случае отсутствия в формате сообщения кода приоритета, работа устройства не отличается от прототипа и поэтому здесь не рассматривается. Рассмотрим работу устройства в случае наличия в формате сообщения поля приоритета.

Предположим, что к моменту прихода сообщения уже имеется очередь сообщений, содержащаяся в регистрах 20.1-20.k-1, а в регистре 20.k сообщения не присутствует, то есть этот регистр пустой. Очередь расположилась в порядке старшинства приоритетов, то есть первым в очереди сообщений располагается сообщение с самым высоким приоритетом, вторым с более низким относительно первого и т.д. Приоритеты сообщений хранятся в регистрах 20.1-20.k-1 вместе с сообщениями согласно формату (фиг.5). Предположим также, что новое сообщение в результате анализа его приоритета должно быть сохранено в регистре 20.i (i=1, 2, …, k-1), а ранее хранящееся в нем сообщение необходимо сдвинуть в регистр 20.i-1, то есть должна произойти «вставка» нового сообщения в очередь сообщений.

Сообщение поступает на первый вход блока элементов И 22. С выхода блока элементов И 22 приоритет нового сообщения (фиг.5) подается на вторые входы группы 31.1, 31.2, …, 31.k-1 элементов сравнения. К этому моменту на соответствующих первых входах элементов сравнения 31.1, 31.2, …, 31.k-1 уже присутствуют приоритеты сообщений, хранящихся в очереди.

Предположим, что новое общение имеет приоритет меньше сообщения, содержащегося в регистре 20.k-2, и больше, чем в регистре 20.k-1. Поэтому новое сообщение необходимо сохранить в регистре 20.k-1. В свою очередь, сообщение, которое хранится в регистре 20.k-1, необходимо переназначить (сдвинуть) влево в регистр 20.k.

Положительный потенциал с выхода элемента сравнения 31.k-1 подается на первый вход элемента И 38.k-1. При наличии сообщения, хранящегося в регистре 20.k-1, на второй вход элемента И 38.k-1 поступает также разрешающий потенциал с выхода элемента ИЛИ- НЕ 24.k-1. В результате с выхода элемента 38.k-1 разрешающий потенциал через блок элементов 32.k-1 обеспечивает поступление сообщения, хранящегося в регистре 20.k-1, через элемент ИЛИ 34 на D-вход регистра 20.k и одновременно в блоке элементов 35.k запрещает прохождение входного сообщения. Кроме того, этот же разрешающий потенциал пропускает через элемент И 39.k и ИЛИ 25.k импульс записи, по окончании которого в регистр 20.k переписывается сообщение, хранившееся ранее в регистре 20.k-1.

Так как результат сравнения в элементе 31.k-2 сравнения отрицательный, то на его выходе присутствует нулевой потенциал, который подается также и на первый вход элемента И 38.k-2. Следовательно, на выходе элемента И 38.k-2 появляется нулевой потенциал, который поступает на входы блоков элементов И 35.k-1, 32.k-2, элементов И 37.k-1, 37.k-2. Так как этот сигнал подается на инверсный вход элемента 35.k-1, то на его выходе появляется код нового сообщения, которое проходит через элемент ИЛИ 21.k-1 и далее поступает на D-вход регистра 20.k-1. В то же время нулевой потенциал с выхода элемента И 38.k-2 поступает на первый инверсный вход элемента 37.k-1, на прямой вход которого подается разрешающий потенциал с элемента 38.k-1. В результате на выходе элемента И 37.k-1 появляется единичный потенциал, который подается на первый вход элемента И 36.k-1. Синхроимпульс с выхода элемента 33 задержки поступает на второй вход элемента И 36.2. Следовательно, на его выходе появляется единичный импульс, который проходит через элемент ИЛИ 25.k-1 и поступает на синхровход регистра 20.k-1, обеспечивая запись нового сообщения в регистр 20.k-1.

Таким образом, новое сообщение, поступившее на вход очереди, было записано с учетом имеющегося в нем приоритета. При этом сообщения с меньшим приоритетом, ранее хранившиеся в регистре 20.k-1, оказались смещенными на одну позицию в регистр 20.k. В то же время очередность других k-2х сообщений оказалась не нарушена. Этим обеспечивается расширение функциональных возможностей устройства, а следовательно, области его целесообразного применения.

Модуль коммутационной сети, содержащий с первого по третий блоки организации очереди сообщений, регистр идентификатора модуля, блок анализа очередей сообщений, мультиплексор, регистр, демультиплексор, триггер, блок синхронизации, первый и второй элементы сравнения, первый дешифратор, второй дешифратор и элемент И, причем первый управляющий выход блока анализа очередей сообщений соединен со входом первого дешифратора и управляющим входом мультиплексора, выход которого соединен с информационным входом регистра, первая группа выходов которого соединена с первым входом первого элемента сравнения, вторая группа выходов регистра соединена с первым входом второго элемента сравнения, первая, вторая и третья группы выходов регистра соединены с информационным входом демультиплексора, выходы которого с первого по третий являются выходами модуля с первого по третий соответственно, второй управляющий выход блока анализа очередей сообщений соединен с входом установки триггера и первым входом элемента И, выход которого подключен к входу сброса триггера, прямой выход которого подключен ко входу запуска блока синхронизации, первый выход которого подключен к входу синхронизации регистра и входу синхронизации регистра идентификатора модуля, первая группа выходов которого соединена со вторым входом первого элемента сравнения, выход которого соединен с первым входом второго дешифратора, вторая группа выходов регистра идентификатора модуля соединена со вторым входом второго элемента сравнения, выход которого подключен ко второму входу второго дешифратора, выход которого подсоединен к управляющему входу демультиплексора, третий выход блока синхронизации соединен со вторым входом элемента И и с информационным входом демультиплексора, входы модуля с первого по третий соединены с информационными входами блоков организации очереди сообщений с первого по третий соответственно, информационные выходы блоков организации очереди сообщений с первого по третий подключены к входам мультиплексора с первого по третий соответственно, управляющие выходы блоков организации очереди сообщений с первого по третий подключены к входам блока анализа очередей сообщений с первого по третий соответственно, второй выход блока синхронизации подсоединен к входам синхронизации блоков организации очереди сообщений с первого по третий, выходы первого дешифратора с первого по третий подключены ко входам опроса блоков организации очереди сообщений с первого по третий соответственно, каждый блок организации очереди сообщений включает k регистров (где k - максимальная длина очереди сообщений), k-1 блоков элементов ИЛИ, группу из k элементов И, группу из k элементов ИЛИ, регистр длины очереди, элемент И, элемент ИЛИ, элемент задержки, причем первый разряд информационного входа блока подключен к первым входам элементов И группы с первого по k-й и первому входу элемента ИЛИ, выход которого подсоединен к входу элемента задержки, выход которого подключен к входу синхронизации регистра длины очереди, выход которого подсоединен к управляющему выходу блока, выходы блоков элементов ИЛИ с первого по (k-1)-й подключены к информационным входам регистров с первого по (k-1)-й соответственно, выходы регистров с второго по k-й соединены с вторыми входами блоков элементов ИЛИ с первого по (k-1)-й соответственно, выход первого регистра соединен с информационным выходом блока, выходы элементов И группы с первого по k-й соединены с первыми входами элементов ИЛИ группы с первого по k-й соответственно, выходы которых подключены к входам синхронизации регистров с первого по k-й соответственно, вход синхронизации и вход опроса блока подключены соответственно к первому и второму входам элемента И, выход которого подключен к вторым входам элементов ИЛИ группы с первого по k-й и второму входу элемента ИЛИ, блок элементов И, группа из k элементов ИЛИ-НЕ, элемент И-НЕ, причем с второго по (m+1)-й разряды информационного входа блока (m - разрядность кода сообщения) подключены к первому входу блока элементов И, выход которого подключен к информационному входу k-го регистра и к первым входам блоков элементов ИЛИ с первого по (k-1)-й, выход элемента И соединен с вторым входом блока элементов И, выходы регистров с первого по k-й соединены с входами элементов ИЛИ-НЕ группы с первого по k-й соответственно, выходы которых подсоединены к вторым входам элементов И группы с первого по k-й соответственно, входу элемента И-НЕ и информационному входу регистра длины очереди, выходы элементов ИЛИ-НЕ группы с первого по (k-1)-й соединены с третьими входами элементов И группы с второго по k-й соответственно, выход элемента И-НЕ подключен к управляющему выходу блока, отличающийся тем, что в него дополнительно введен (k-1) элемент сравнения, первая группа из (k-1) блоков элементов И, второй элемент задержки, элемент ИЛИ, вторая группа из (k-1) блоков элементов И, первая группа из (k-1) элементов И, вторая группа из (k-1) элементов И, третья группа из (k-1) элементов И, четвертая группа из (k-1) элементов И, причем первые входы каждого из (k-1) элементов сравнения подключены к выходам соответствующих (k-1) регистров, соединенных с информационными входами первой группы из (k-1) блоков элементов И, а вторые входы - к выходу блока элементов И, выходы каждого из (k-1) элементов сравнения подключены к прямому входу соответствующего элемента И третьей группы из (k-1) элементов И, инверсный вход которого подключен к инверсному выходу элемента ИЛИ, при этом выход (i)-го элемента третьей группы подключен к прямому (управляющему) входу i-го блока элементов И первой группы, инверсному (управляющему) входу (i-1)-го блока элементов И второй группы, ко входу i-го элемента И четвертой группы, на второй вход которого подается первый разряд информационного входа блока, а выход подключен к первому дополнительному входу i-го элемента ИЛИ в группе из k элементов ИЛИ, выходы элементов И второй группы подключены к первым входам первой группы из (k-1) элементов И, вторые входы которых подключены к выходу дополнительно введенного второго элемента задержки, на вход которого подается первый разряд информационного входа блока, выходы первой группы дополнительно введенных (k-1) элементов И подключены к вторым дополнительным входам элемента ИЛИ в группе из k элементов ИЛИ за исключением первого, выход i-го блока элементов И первой группы подключен к дополнительно введенным входам (i+1) элемента ИЛИ из состава (k-1) блоков элементов ИЛИ, а также дополнительно введенного элемента ИЛИ, выход которого подключен к информационному входу k-го регистра.