Способ и устройство для уменьшения потребляемой мощности в ассоциативной памяти

Иллюстрации

Показать всеИзобретение относится к блокам ассоциативной памяти. Техническим результатом является уменьшение потребляемой мощности. Схема ассоциативной памяти содержит множество линий совпадения более низкого уровня, множество линий совпадения более высокого уровня и схему восстановления линий совпадения. Линии совпадения более низкого уровня конфигурируются, чтобы восстанавливаться в состояние, предшествующее определению, во время периода, предшествующего определению. Линии совпадения более высокого уровня конфигурируются, чтобы фиксировать состояние оценки соответствующих групп из одной или более линий совпадения более низкого уровня во время периода оценки и восстанавливаться в состояние, предшествующее определению, во время периода, предшествующего определению; схема восстановления линий совпадения конфигурируется так, чтобы предотвратить восстановление по меньшей мере одной из линий совпадения более низкого уровня в состояние, предшествующее определению, в ответ на соответствующую информацию разрешения, например, один или более битов, указывающих, должны ли быть использованы результаты поиска линии совпадения. 3 н. и 17 з.п. ф-лы, 5 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение в целом относится к блокам ассоциативной памяти (АП, CAM) и в частности относится к сокращению потребляемой мощности блоками ассоциативной памяти, без неблагоприятного воздействия на производительность АП.

Уровень техники

В отличие от оперативной памяти (ОЗУ, RAM), в которой оперативная память возвращает слово данных, сохраненное по адресу, подаваемому в оперативную память, ассоциативная память (АП) ищет во всей своей памяти шаблон данных, который соответствует поисковому слову, введенному в АП. Если шаблон данных найден, АП возвращает список из одного или более адресов памяти, где это слово было найдено. В некоторых АП также возвращаются слово данных или другие ассоциированные данные. Таким образом, АП являются часто используемым ассоциативным массивом.

Схемы АП содержат множество записей, где каждая запись имеет ряд ячеек АП, выполненных с возможностью хранения данных. Ячейки АП могут быть двоичными (хранят данные в двоичном коде) или троичными (хранят данные в двоичном коде или в «неопределенном» состоянии). Каждая ячейка АП подсоединена к линии совпадения. Во время операции поиска в АП поисковое поле подается в АП. В ответ на ввод поискового поля каждая линия совпадения указывает, содержит ли ее соответствующая ячейка АП данные, совпадающие с некоторой частью поискового поля. После того как операция поиска завершается, линии совпадения обычно восстанавливаются в состояние, предшествующее определению, чтобы повысить производительность АП во время последующего поиска. Например, линии совпадения обычно предварительно «высоко заряжают» до значения логической единицы во время периода, предшествующего определению.

Во время последующей операции поиска АП линии совпадения, ассоциированные с ячейками АП, которые не содержат данные совпадения, разряжаются. Только те линии совпадения, подсоединенные к ячейкам АП, которые хранят данные совпадения, остаются «высоко» заряженными. Как таковая, только одна ячейка АП, ассоциированная с записью, должна содержать несовпадающие данные для этой записи, которая будет идентифицирована как содержащая несовпадающий шаблон данных. Это называется промахом. Наоборот, если каждая ячейка в записи выдает совпадение, запись идентифицируется как содержащая шаблон совпадения, что называется как попадание.

Некоторые обычные АП содержат множественные уровни иерархических линий совпадения, чтобы уменьшить емкостную загрузку на линии совпадения, которая влияет на производительность и потребляемую мощность АП. В таких многоуровневых иерархических АП локальные линии совпадения, обслуживающие группу ячеек АП, подсоединяются к единственной глобальной линии совпадения. Несовпадение, указанное одной или более локальными линиями совпадения, отражается соответствующей глобальной линией совпадения. Также глобальная линия совпадения указывает промах, если любая из ее соответствующих локальных линий совпадения указывает промах. Наоборот, глобальная линия совпадения указывает попадание, если все ее соответствующие локальные линии совпадения указывают попадание. В зависимости от размера АП один или более промежуточных уровней линий совпадения могут быть включены между локальными линиями совпадения и соответствующей глобальной линией совпадения, чтобы дополнительно уменьшить емкостную загрузку.

Независимо от конкретной архитектуры АП некоторые приложения, которые обрабатывают результаты поиска АП, могут нуждаться только в поисковых результатах для поднабора записей АП. Например, некоторые приложения могут отказаться или проигнорировать результаты попадания/промаха при поиске для некоторых частей конкретных записей АП, в то же время используя результаты поиска, ассоциированные с другими частями этих записей. Один обычный подход для игнорирования результатов поиска попадание/промах для конкретных ячеек АП заключается в отключении ячеек АП, не представляющих интерес, от их соответствующих линий совпадения. Например, транзисторное устройство может быть размещено последовательно между выходным узлом ячейки АП и ее соответствующей линией совпадения. Когда транзистор выключен, ячейка АП отсоединена от ее линии совпадения. Также содержимое этой ячейки АП не влияет на состояние линии совпадения этой ячейки АП. Таким образом, линия совпадения остается в своем состоянии, предшествующем определению, например, предварительно высоко заряженном состоянии, независимо от того, содержит ли ее соответствующая ячейка АП данные совпадения или нет. Однако энергия потребляется при предварительной зарядке линии совпадения ячейки АП во время периода, предшествующего определению, даже при том, что результаты поиска, ассоциированные с этой ячейкой АП, будут проигнорированы. Кроме того, когда разрешающий транзистор включается, этот транзистор подсоединяет выходной узел ячейки АП к линии совпадения. Такая конфигурация добавляет дополнительную емкость к выходному узлу ячеек АП, таким образом замедляя операции линии совпадения и потребляя дополнительную энергию.

Другой обычный подход для игнорирования конкретных результатов поиска в многоуровневых иерархических АП заключается в блокировке схемы разрешения глобальной линии совпадения, ассоциированной с локальными линиями совпадения, не представляющими интерес. Например, синхросигнал, который управляет, может ли предварительно заряженная глобальная линия совпадения быть разряжена, стробируется сигналом разрешения. Если синхросигнал запрещен, глобальная линия совпадения остается в своем предварительно заряженном состоянии независимо от состояния локальных линий совпадения, подсоединенных к ней. В результате только на глобальные линии совпадения, которые разрешены во время периода оценки АП, оказывается влияние посредством состояния их соответствующих локальных линий совпадения. Мощность все еще потребляется, предварительно заряжая соответствующие глобальные и локальные линии совпадения, когда схема разрешения глобальной линии совпадения блокирована.

Сущность изобретения

Согласно способам и устройству, раскрытому в настоящем описании, схема многоуровневой иерархической ассоциативной памяти (АП), включает в себя схему подсоединения линий совпадения, чтобы уменьшить потребляемую мощность, не влияя неблагоприятно на работу АП. Схема подсоединения линий совпадения уменьшает потребляемую мощность посредством предотвращения восстановления линий совпадения АП, не представляющих интерес, в состояние, предшествующее определению, например, посредством предотвращения предварительной зарядки линии совпадения. Таким образом, во время периода, предшествующего определению, в цикле обращения к АП только линии совпадения, представляющие интерес, восстанавливаются в их состояние, предшествующее определению.

Информация разрешения, принятая или иначе полученная схемой подсоединения линий совпадения, указывает, какие линии совпадения не представляют интерес. В одном варианте осуществления информация разрешения непосредственно указывает, какие линии совпадения не представляют интерес. В другом варианте осуществления информация разрешения косвенно указывает, какие линии совпадения не представляют интерес, например, посредством идентификации линий совпадения, представляющих интерес. Вне зависимости от этого информация разрешения может содержать любую информацию, подходящую для указания, представляют ли интерес конкретные линии совпадения АП или нет, например, индикатор определенного/неопределенного состояния, один или более маскирующих битов, один или более битов действительности/недействительности и т.д.

В дополнение к предотвращению восстановления некоторых линий совпадения и таким образом сохранению энергии, схема подсоединения линий совпадения также отсоединяет соответствующие линии совпадения более высокого уровня от линий совпадения, идентифицированных как не представляющие интерес. Это предотвращает непредсказуемое поведение, когда конкретные линии совпадения более низкого уровня не восстанавливаются в их состояние, предшествующее определению, в качестве части вышеупомянутых операций сохранения энергии.

Согласно одному варианту осуществления уменьшения потребляемой мощности в схеме многоуровневой иерархической АП получают информацию разрешения, ассоциированную с одной или более линиями совпадения АП, включенными в схему многоуровневой иерархической АП. Отдельные линии совпадения АП предотвращаются от восстановления в состояние, предшествующее определению, в ответ на информацию разрешения. Согласно одному варианту осуществления многоуровневой иерархической схемы АП, схема АП содержит множество линий совпадения более низкого уровня, множество линий совпадения более высокого уровня и схему восстановления линий совпадения. Линии совпадения более низкого уровня конфигурируются, чтобы восстанавливаться в состояние, предшествующее определению, во время периода, предшествующего определению. Линии совпадения более высокого уровня конфигурируются, чтобы фиксировать состояние определения (оценки) соответствующих групп из одной или более линий совпадения более низкого уровня во время периода оценки (определения) и восстанавливаться в состояние, предшествующее определению, во время периода, предшествующего определению. Схема восстановления линий совпадения конфигурируется, чтобы предотвратить по меньшей мере одну из линий совпадения более низкого уровня от восстановления в состояние, предшествующее определению, в ответ на соответствующую информацию разрешения, например, когда линия совпадения распознается как соответствующая неопределенному (маскированному) или недействительному содержимому.

Схема многоуровневой иерархической АП может быть включена в или ассоциирована с различными видами запоминающих устройств, такими как кэши и буферы. Согласно одному варианту осуществления буфера динамической трансляции (TLB) такой TLB содержит схему многоуровневой иерархической АП, имеющую множество записей и соответствующих линий совпадения. Схема многоуровневой иерархической АП конфигурируется так, чтобы хранить информацию разрешения, ассоциированную с записями, и преобразовывать (транслировать) адреса виртуальной памяти в соответствующие адреса физической памяти. Информация разрешения в текущем контексте TLB соответствует одному или более битам, которые указывают достоверность записей TLB. Схема многоуровневой иерархической АП конфигурируется так, чтобы препятствовать тому, чтобы отдельные линии совпадения были восстановлены в состояние, предшествующее определению, в ответ на информацию разрешения.

Конечно, настоящее изобретение не ограничивается вышеупомянутыми признаками и преимуществами. Специалистам будут понятны дополнительные признаки и преимущества после прочтения нижеследующего подробного описания и после рассмотрения сопроводительных чертежей.

Краткое описание чертежей

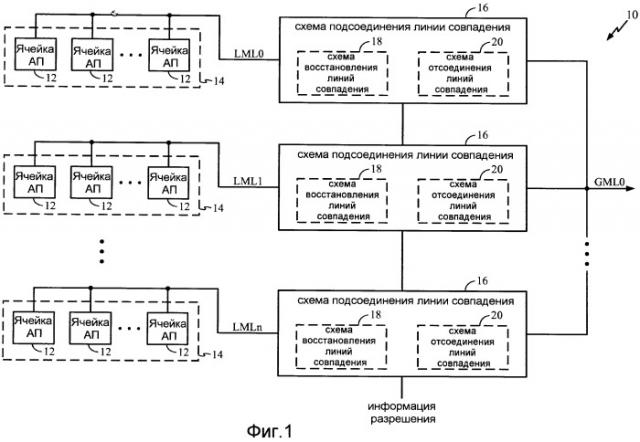

Фиг. 1 - частичная блок-схема, иллюстрирующая вариант осуществления схемы многоуровневой иерархической ассоциативной памяти (АП), имеющей схему подсоединения линий совпадения, которая уменьшает потребляемую мощность.

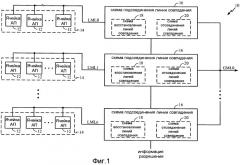

Фиг. 2 - схема последовательности операций, иллюстрирующая вариант осуществления программной логики, чтобы уменьшить потребляемую мощность в схеме многоуровневой иерархической АП.

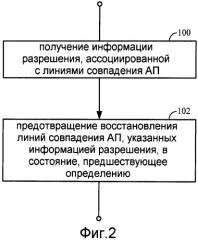

Фиг. 3 - блок-схема, иллюстрирующая один вариант осуществления схемы подсоединения линий совпадения, включенной в многоуровневую иерархическую АП.

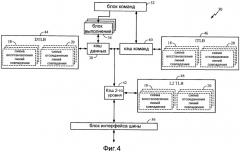

Фиг. 4 - блок-схема, иллюстрирующая вариант осуществления микропроцессора, включающего в себя схему подсоединения линий совпадения АП.

Фиг. 5 - блок-схема, иллюстрирующая другой вариант осуществления схемы подсоединения линий совпадения, включенной в многоуровневую иерархическую АП.

Подробное описание

Фиг. 1 частично иллюстрирует вариант осуществления схемы 10 многоуровневой иерархической ассоциативной памяти (АП), которая уменьшает потребляемую мощность во время работы АП. Схема 10 АП имеет множественные ячейки памяти 12, такие как двоичные или троичные ячейки АП, для хранения данных. Ячейки АП 12 упорядочены в группы 14. Каждая ячейка АП 12 в группе 14 подсоединяется к Локальной Линии Совпадения (LML). Схема 16, включенная в схему 10 АП, подсоединяет LML к линии совпадения более высокого уровня, например, LML0-LMLn подсоединены к Глобальной Линии Совпадения (GML0) на фиг. 1. В одном варианте осуществления соответствующие LML непосредственно подсоединяются к GML через схему 16 подсоединения линий совпадения. Согласно этому варианту осуществления, схема 10 АП содержит два иерархических уровня линий совпадения (локальные и глобальные линии совпадения). В другом варианте осуществления соответствующие LML подсоединяются к Промежуточной Линии Совпадения (IML). Соответствующие IML затем прямо или косвенно подсоединяются к соответствующей GML. Согласно этому варианту осуществления схема 10 АП содержит более двух иерархических уровней линий совпадения (линии LML, по меньшей мере один уровень из линий IML, и линии GML).

Независимо от количества уровней линий совпадения схема 16 подсоединения линий совпадения содержит схему 18 восстановления линий совпадения и схему 20 отсоединения линий совпадения. Только для простоты объяснения схема 16 подсоединения линий совпадения описывается ниже со ссылками на подсоединение линий LML к линиям GML. Однако специалистам понятно, что схема 16 подсоединения, описанная здесь, может подсоединить любой иерархически более низкий уровень линий совпадения к линиям совпадения более высокого уровня.

Имея это в виду, схема 18 восстановления линий совпадения определяет, должны ли конкретные LML быть восстановлены в состояние, предшествующее определению, после операции поиска АП. Таким образом, не все LML могут представлять интерес во время конкретной операции поиска АП. Например, содержимое одной или более записей АП (не показаны) или части записей АП может быть маркировано как недействительное или маскировано во время оценки (определения). Линии LML, соответствующие этим записям или частичным записям, не представляют интерес. Результаты поиска, обеспеченные линиями LML, не представляющими интерес, обычно игнорируются или отвергаются во время операции поиска АП. Информация разрешения, например, один или более битов действительности или маскирующих битов, ассоциированных с каждой записью АП, выдается схеме 18 восстановления линий совпадения, чтобы указать, какие LML не представляют интерес. В одном варианте осуществления информация разрешения непосредственно указывает, какие линии совпадения не представляют интерес. В другом варианте осуществления информация разрешения косвенно указывает, какие линии совпадения не представляют интерес, например, при идентификации линий совпадения, представляющих интерес. Независимо от этого схема 18 восстановления линий совпадения использует информацию разрешения, чтобы идентифицировать линии совпадения, которые будут проигнорированы во время операции поиска АП.

Если конкретная схема 18 восстановления линий совпадения определяет, что ее соответствующие LML не представляют интерес, она препятствует тому, чтобы эти LML были восстановлены в состояние, предшествующее определению, по существу блокируя эти LML. В одном варианте осуществления схема 18 восстановления линий совпадения препятствует тому, чтобы LML были предварительно заряжены. В другом варианте осуществления схема 18 восстановления линий совпадения препятствует тому, чтобы LML были предварительно разряжены. Поскольку результаты поиска, ассоциированные с этими LML, не представляют интерес, предотвращение их восстановления в состояние, предшествующее определению, уменьшает потребляемую мощность без неблагоприятного воздействия на работу схемы 10 АП. Информация разрешения, используемая схемой 18 восстановления линий совпадения, может быть сохранена в схеме 10 АП, например, как один или более битов действительности, включенных в каждую запись в схеме 10 АП, или может быть выдана в схему 10 АП.

Информация разрешения также используется схемой 20 отсоединения линий совпадения. Схема 20 отсоединения линий совпадения использует информацию разрешения, чтобы предотвратить LML, не представляющие интерес, от воздействия на соответствующие им GML. Отсоединение LML, не представляющей интерес, от ее GML гарантирует, что эта LML не будет влиять на состояние ее GML. Вместо этого только разрешенные LML, подсоединенные к GML, могут влиять на состояние GML, например, разряжая ее. Это предотвращает нестабильное поведение схемы 10 АП, в то же время сокращая потребляемую мощность.

В одном варианте осуществления схема 20 отсоединения линий совпадения предотвращает группу LML, которые были блокированы схемой 18 восстановления линий совпадения, от воздействия на состояние GML, к которой они подсоединены. Если информация разрешения указывает, что группа LML, ассоциированная с конкретной GML, должна быть проигнорирована во время операции поиска АП, то схема 20 отсоединения линий совпадения отсоединяет эту группу LML от этой GML. Также схема 20 отсоединения линий совпадения препятствует тому, чтобы отдельные группы LML влияли на состояние соответствующих GML, когда эти LML не представляют интерес.

Ниже приведен неограничивающий пример, основанный на схеме 10 АП, показанный на фиг. 1, чтобы продемонстрировать, как схемы 18, 20 восстановления и отсоединения линий совпадения функционируют во время операции АП поиска. В течение периода, предшествующего определению, при операции поиска АП схема 10 АП получает информацию разрешения линий совпадения, как иллюстрируется этапом 100 на фиг. 2. В одном варианте осуществления схема 10 АП обращается к ячейке памяти в каждой записи схемы 10 АП, чтобы получить соответствующий бит действительности, который указывает действительность этих записей. В существующем примере информация разрешения указывает, что все LML, за исключением LML1, представляют интерес. На основании этой информации разрешения схема 18 восстановления линий совпадения, ассоциированная с LML1, препятствует тому, чтобы LML1 была восстановлена в ее состояние, предшествующее определению, в то время как другие схемы 18 восстановления линий совпадения разрешают восстановление их соответствующих LML, как иллюстрируется этапом 102 на фиг. 2. Кроме того, схема 20 отсоединения линий совпадения, ассоциированных с LML1, препятствует тому, чтобы LML1 влияла на состояние GML0 во время последующего периода оценки (определения). Таким образом, на состояние GML0 может влиять каждая LML, кроме LML1.

Фиг. 3 иллюстрирует один вариант осуществления схемы 16 подсоединения линий совпадения, включенной в схему 10 АП. Схема 16 подсоединения линий совпадения включает в себя схему предварительной зарядки LML (полевой транзистор p-типа T1), инвертор (полевой транзистор p-типа T2 и полевой транзистор n-типа T3), схему предварительной зарядки GML (полевой транзистор p-типа T4) и схему оценки (определения) GML (полевые транзисторы n-типа T5 и T6). Схема 16 подсоединения линий совпадения также включает в себя схемы 18, 20 восстановления и отсоединения линий совпадения. Согласно этому варианту осуществления схема 18 восстановления линий совпадения содержит полевой транзистор p-типа (T7), включенный между источником напряжения (Vdd) и узлами «исток» схемы предварительной зарядки LML и инвертора. Схема 20 отсоединения линий совпадения содержит полевой транзистор n-типа (T8), подсоединенный к одному входу затвора схемы оценки GML. Логическими вентилями (затворами) схем 18, 20 восстановления и отсоединения линий совпадения управляет разрешающий сигнал (LML_ENABLE).

Этот разрешающий сигнал указывает, представляет ли эта LML интерес или нет. Когда разрешающий сигнал является логической единицей, это приводит к блокировке предварительной зарядки LML и приводит к отсоединению LML от ее GML. В частности, если разрешающий сигнал указывает, что результаты поиска, ассоциированные с LML, представляют интерес, схема 18 восстановления линий совпадения активизируется (например, полевой транзистор p-типа T7 включается). При активизации схема 18 восстановления линий совпадения разрешает работу схемы предварительной зарядки LML и инвертора посредством зарядки их соответствующих узлов-истоков до логического значения единица (Vdd). Это разрешает схеме предварительной зарядки LML выполнить предварительную зарядку LML до логического значения единица в ответ на активный сигнал восстановления (RESTORE) во время периода, предшествующего определению. В отличие от некоторых способов работы обычных схем схема 18 восстановления линий совпадения неблагоприятно не воздействует на производительность схемы 10 АП при активизации. В частности, схема восстановления линий совпадения не добавляет дополнительную емкость к выходному узлу ячейки АП (не показано), подсоединенной к LML, при активизации. Поскольку схема 18 восстановления линий совпадения не включается в активное соединение тракта передачи сигналов LML к выходному узлу ячейки АП, это не приводит к дополнительной емкостной нагрузке.

Когда LML представляет интерес, разрешающий сигнал также вызывает деактивизацию схемы 20 отсоединения линий совпадения (например, полевой транзистор n-типа T8 выключается). Когда схема 20 отсоединения линий совпадения деактивируется, на состояние GML влияет LML. В результате, когда полевой транзистор n-типа T6 схемы определения (оценки) GML активизируется в ответ на синхросигнал разрешения (GML_CLK), состояние этой LML управляет тем, включается или выключается полевой транзистор n-типа T5 схемы оценки GML. Если полевой транзистор n-типа T5 включен, GML разряжается до уровня напряжения «земля». Наоборот, GML остается не затронутой LML независимо от состояния LML, когда полевой транзистор n-типа T5 выключен. В результате схема 20 отсоединения линий совпадения не влияет на состояние GML, когда она деактивирована. Вместо этого состояние GML отражает состояние только разрешенных LML.

Если LML не представляет интерес, схема 18 восстановления линий совпадения деактивируется (например, полевой транзистор p-типа T7 выключается). При деактивации схема 18 восстановления линий совпадения отсоединяет узлы-истоки схемы предварительной зарядки LML и инвертора от источника питания. Схема предварительной зарядки LML неспособна предварительно зарядить LML, когда источник питания отсоединен от его узла-истока, таким образом уменьшая ненужную потребляемую мощность. Дополнительно LML блокируется, когда схема 18 восстановления линий совпадения деактивирована.

Кроме того, разрешающий сигнал активизирует схему 20 отсоединения линий совпадения, когда LML блокирована. Схема 20 отсоединения линий совпадения устанавливает входной сигнал затвора полевого транзистора n-типа T5 схемы оценки GML до значения низкого логического уровня (Vss). Когда входной сигнал затвора полевого транзистора n-типа T5 низкий, состояние LML не влияет на вход GML, и таким образом LML отсоединяется от ее GML. В частности, полевой транзистор n-типа T5 не может проводить достаточный ток, когда его входной сигнал затвора имеет низкий уровень. Также GML, которая была предварительно заряжена во время предшествующего периода «не определения», не может быть разряжена этой конкретной схемой оценки GML независимо от состояния LML. При активизации схема 20 отсоединения линий совпадения также предотвращает непредсказуемое поведение посредством схемы 10 АП при снижении входного сигнала затвора полевого транзистора n-типа T5 схемы оценки GML. Если входной сигнал затвора полевого транзистора n-типа T5 не снижается, выходной узел инвертора (lml_sns), может неблагоприятно влиять на состояние GML. Например, выходной узел инвертора GML может иметь неопределенное состояние («плавать») или иначе действовать неочевидно, когда источник питания был отключен от его узла-истока. Схема 20 отсоединения линий совпадения предотвращает такое спорадическое поведение из-за неблагоприятного воздействия на GML посредством воспрепятствования этой LML влиять на состояние GML, когда LML не представляет интерес.

Схемы 18, 20 восстановления и отсоединения линий совпадения могут быть включены в или ассоциированы с различными видами запоминающих устройств, такими как кэши и буфера. Фиг. 4 иллюстрирует один вариант осуществления микропроцессора 30, имеющего схему ассоциативной памяти или подобную ассоциативную память, которая включает в себя один или более экземпляров схем 18, 20 восстановления и отсоединения линий совпадения. Более подробно, микропроцессор 30 включает в себя модуль 32 команд, одно или более устройств 34 выполнения, блок 36 интерфейса шины, кэш 38 данных, кэш 40 команд и кэш 42 высокого уровня (L2). Модуль 32 команд обеспечивает централизованное управление потока команд к устройствам 34 выполнения. Устройства 34 выполнения выполняют команды, отправленные модулем 32 команд. Блок 36 интерфейса шины обеспечивает механизм передачи данных, команд, адресов и управляющих сигналов к и от микропроцессора 30. Кэши 38, 40 данных и команд хранят данные и команды, соответственно. Кэш 42 L2 обеспечивает быстродействующий буфер памяти между кэшами 38, 40 данных и команд и памятью (не показана), внешней для микропроцессора 30.

У кэшей 38, 40 и 42 есть соответствующие буфера динамической трансляции (TLB) 44, 46 и 48 для выполнения переадресации во время операций доступа к кэшу. Каждый TLB 44, 46 и 48 имеет один или более экземпляров схем 18, 20 восстановления и отсоединения линий совпадения. Альтернативно, объединенный TLB (не показан) может выполнить переадресацию для кэшей 38, 40 и 42. Независимо, TLB 44, 46 и 48 являются основанными на АП в том, что виртуальный адрес, представляющий интерес, выдается на TLB 44, 46 и 48 и TLB 44, 46 и 48 выдают в ответ соответствующие результаты попаданий и промахов. В случае попадания формируется физический адрес, соответствующий полю поиска виртуального адреса. В случае промаха происходит обработка таблицы страниц.

TLB 44, 46 и 48 имеют записи (не показаны), которые содержат информацию для использования при преобразовании виртуального адреса в физические адреса. В одном варианте осуществления каждая запись TLB содержит поле виртуального адреса, соответствующее поле физического адреса и бит действительности. Если поле поиска виртуального адреса соответствует записи в одном из TLB 44, 46 и 48, выводится соответствующее поле физического адреса. Иначе происходит обработка таблицы страниц. Бит действительности определяет, действительна ли конкретная запись TLB или нет. Если не действительна, содержимое записи игнорируется или отвергается во время переадресации. Другие биты разрешения, такие как биты размера страницы, могут определять, должны ли соответствующие части битов виртуальных адресов участвовать в переадресации.

Фиг. 5 иллюстрирует один вариант осуществления схемы 16 подсоединения линий совпадения для использования в TLB 44, 46 и 48. Согласно этому варианту осуществления бит действительности (VAILD), извлеченный из записи TLB 44, 46 и 48, управляет работой схем 18, 20 восстановления и отсоединения линий совпадения. Когда конкретная запись TLB 44, 46 и 48 является действительной, ее бит действительности разрешает работу схемы 18 восстановления линий совпадения. Когда разрешено, схема 18 восстановления линий совпадения восстанавливает ее LML в состояние, предшествующее определению, после операции поиска TLB. Кроме того, схема 18 восстановления включает в себя второй полевой транзистор p-типа (T9), чтобы предварительно зарядить соответствующую GML, когда разрешено. Наоборот, когда бит действительности указывает, что запись недействительна, LML отсоединяется от своей GML.

Согласно этому варианту осуществления LML отсоединяется от ее GML, когда полевой транзистор p-типа 10 схемы 10 отсоединения линий совпадения устанавливает входной сигнал схемы инвертора GML (полевой транзистор p-типа T2 и полевой транзистор n-типа T3) в значение низкого логического уровня (Vss). Когда схема 20 отсоединения линий совпадения устанавливает входной сигнал инвертора до значения низкого логического уровня, LML фактически отсоединяется от ее GML. Таким образом, LML больше не влияет на состояние GML, так как инвертор выдает логическую единицу независимо от состояния LML. При установке входного сигнала инвертора в значение низкого логического уровня GML разряжается, когда ее входной сигнал тактового генератора (GML_CLK) является активным. Когда GML разряжается, это интерпретируется как несовпадение. Таким образом, этот вариант осуществления схемы 16 подсоединения препятствует обработке ложных попаданий, когда записи TLB 44, 46 и 48 недействительны. Альтернативно, вариант осуществления схемы 16 подсоединения, проиллюстрированный на фиг. 3, может быть включен в TLB 44, 46 и 48, чтобы предотвратить восстановление недействительных LML и отсоединить недействительные LML от их соответствующих GML.

В вышеописанном множестве разновидностей и применений должно быть понятно, что настоящее изобретение не ограничивается предшествующим описанием, и при этом оно не ограничивается сопроводительными чертежами. Вместо этого настоящее изобретение ограничивается только нижеследующей формулой изобретения и ее эквивалентами.

1. Устройство многоуровневой иерархической ассоциативной памяти, содержащее:множество линий совпадения более низкого уровня, включающих в себя первую группу связанных линий совпадения более низкого уровня, сконфигурированных восстанавливаться в состояние, предшествующее определению, во время периода, предшествующего определению;линию совпадения более высокого уровня, соединенную с первой группой связанных линий совпадения более низкого уровня, причем линия совпадения более высокого уровня сконфигурирована с возможностью фиксировать состояние оценки отдельных линий совпадения более низкого уровня в пределах первой группы связанных линий совпадения более низкого уровня во время периода определения и восстанавливаться в состояние, предшествующее определению, во время периода, предшествующего определению; исхему восстановления линий совпадения, сконфигурированную предотвращать восстановление, по меньшей мере, одной из линий совпадения более низкого уровня в пределах первой группы в состояние, предшествующее определению, в ответ на информацию разрешения, ассоциированную с линиями совпадения более низкого уровня в пределах первой группы.

2. Устройство по п.1, в котором схема восстановления линий совпадения сконфигурирована предотвращать восстановление, по меньшей мере, одной из линий совпадения более низкого уровня в пределах первой группы в состояние, предшествующее определению, в ответ на информацию разрешения посредством предотвращения предварительной зарядки линии совпадения.

3. Устройство по п.1, в котором схема восстановления линий совпадения сконфигурирована предотвращать восстановление, по меньшей мере, одной из линий совпадения более низкого уровня в пределах первой группы в состояние, предшествующее определению, в ответ на информацию разрешения посредством предотвращения предварительной разрядки линии совпадения.

4. Устройство по п.1, в котором схема восстановления линий совпадения дополнительно сконфигурирована предотвращать восстановление одной или более промежуточных линий совпадения в состояние, предшествующее определению, в ответ на информацию разрешения.

5. Устройство по п.1, дополнительно содержащее схему отсоединения линий совпадения, сконфигурированную отсоединять одну или более линий совпадения более низкого уровня в пределах первой группы в ответ на информацию разрешения от линии совпадения более высокого уровня.

6. Устройство по п.5, в котором схема отсоединения линий совпадения сконфигурирована отсоединять одну или более линий совпадения более низкого уровня в пределах первой группы в ответ на информацию разрешения от линии совпадения более высокого уровня посредством предотвращения влияния состояния, предшествующего определению, линии совпадения более высокого уровня на отдельные линии совпадения более низкого уровня в пределах первой группы.

7. Устройство по п.6, в котором схема отсоединения линий совпадения сконфигурирована предотвращать влияние состояния, предшествующего определению, линии совпадения более высокого уровня на отдельные линии совпадения более низкого уровня в пределах первой группы посредством предотвращения отдельных линий совпадения более низкого уровня в пределах первой группы от разрядки линии совпадения более высокого уровня.

8. Устройство по п.5, в котором схема отсоединения линий совпадения сконфигурирована отсоединять одну или более линий совпадения более низкого уровня в пределах первой группы, в ответ на информацию разрешения от линии совпадения более высокого уровня посредством отсоединения одной или более промежуточных линий совпадения от линии совпадения более высокого уровня.

9. Устройство по п.5, в котором информация разрешения содержит один или более битов, которые указывают, должны ли быть использованы результаты поиска, ассоциированные с отдельными линиями совпадения более низкого уровня.

10. Устройство по п.1, в котором множество линий совпадения более низкого уровня содержит локальные линии совпадения, и линия совпадения более высокого уровня содержит глобальную линию совпадения.

11. Микропроцессор, включающий в себя устройство по п.1.

12. Устройство многоуровневой иерархической ассоциативной памяти, содержащее:множество линий совпадения более низкого уровня, включающих в себя первую группу связанных линий совпадения более низкого уровня, сконфигурированных восстанавливаться в состояние, предшествующее определению, во время периода, предшествующего определению;линию совпадения верхнего уровня, соединенную с первой группой связанных линий совпадения более низкого уровня, причем линия совпадения верхнего уровня сконфигурирована восстанавливаться в состояние, предшествующее определению, во время периода, предшествующего определению; исхему соединения линий совпадения, способную предотвращать восстановление, по меньшей мере, одной из линий совпадения более низкого уровня в пределах первой группы в состояние, предшествующее определению, в ответ на информацию разрешения, ассоциированную с линиями совпадения более низкого уровня в пределах первой группы, причем схема соединения линий совпадения включает в себя:цепь предварительной зарядки линии совпадения более низкого уровня, соединенную с первой группой связанных линий совпадения более низкого уровня;цепь инвертора, соединенную с цепью предварительной зарядки линии совпадения более низкого уровня;цепь предварительной зарядки линии совпадения верхнего уровня, соединенную с линией совпадения верхнего уровня;цепь определения линии совпадения верхнего уровня, соединенную с линией совпадения верхнего уровня.

13. Устройство по п.12, дополнительно содержащее схему восстановления линий совпадения и схему отсоединения линий совпадения.

14. Устройство по п.13, в котором схема восстановления линий совпадения сконфигурирована предотвращать восстановление, по меньшей мере, одной из линий совпадения более низкого уровня в пределах первой группы в состояние, предшествующее определению, в ответ на информацию разрешения, ассоциированную с линиями совпадения более низкого уровня, посредством предотвращения предварительной зарядки линии совпадения.

15. Устройство по п.13, в котором схема восстановления линий совпадения сконфигурирована предотвращать восстановление, по меньшей мере, одной из линий совпадения более низкого уровня в пределах первой группы в состояние, предшествующее определению, в ответ на информацию разрешения, ассоциированную с линиями совпадения более низкого уровня, посредством предотвращения предварительной разрядки линии совпадения.

16. Устройство по п.13, в котором схема восстановления линий совпадения включает в себя первый транзистор, подсоединенный между источником напряжения и узлами "исток" схемы предварительной зарядки линии совпадения более низкого уровня и схемы инвертора соответственно.

17. Устройство по п.16, в котором схема отсоединения линий совпадения вклю