Дифференциальный усилитель с повышенным коэффициентом усиления

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях (ОУ), компараторах). Технический результат: повышение в 8-20 раз коэффициента усиления по напряжению при использовании низкоомных двухполюсников нагрузки (например, R5=R6=700 Ом). Дифференциальный усилитель содержит входной дифференциальный каскад (ДК) (1) с первым (2) и вторым (3) токовыми выходами, связанными с первой шиной (4) источника питания (ИП) через первый (5) и второй (6) двухполюсники нагрузки, первый (7) и второй (8) выходные транзисторы (Т), базы которых объединены, коллекторы соединены с соответствующими первым (2) и вторым (3) токовыми выходами ДК (1), а эмиттеры связаны со второй шиной (9) ИП, буферный усилитель (10), вход которого соединен со вторым (3) токовым выходом ДК (1). В схему введены первый (11) и второй (12) дополнительные Т, эмиттеры которых соединены с первым дополнительным токостабилизирующим двухполюсником (ТД) (13), базы связаны с соответствующими первым (2) и вторым (3) токовыми выходами ДК (1), коллектор Т (12) соединен через второй ТД (14) с первой шиной (4) ИП и подключен ко входу дополнительного неинвертирующего усилителя, выход которого соединен с объединенными базами первого Т (7) и второго Т (8). 10 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях (ОУ), компараторах).

В современной аналоговой микроэлектронике широко применяются дифференциальные усилители (ДУ) с активными нагрузками в виде токовых зеркал на биполярных транзисторах, тип проводимости которых противоположен типу проводимости входных транзисторов ДУ. Однако SiGe технический процесс SGB25VD, внедряемый в настоящее время в ряде российских предприятий для производства РЭА нового поколения, не обеспечивает возможности построения схем с p-n-p транзисторами. Это не позволяет применять традиционные активные нагрузки в ОУ СВЧ диапазона. Как следствие, в качестве элементов коллекторной цепи входного каскада ОУ весьма часто разрешается использовать только пассивные элементы - резисторы [1-25]. В конечном итоге это требование ограничивает коэффициент усиления по напряжению (Kу) входного дифференциального каскада ОУ и всей схемы ОУ в целом.

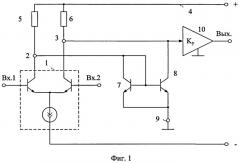

Наиболее близким по технической сущности к заявляемому устройству является ДУ (фиг.1), рассмотренный в патенте США №4.418.290. Он содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, связанными с первой 4 шиной источника питания через первый 5 и второй 6 двухполюсники нагрузки, первый 7 и второй 8 выходные транзисторы, базы которых объединены, коллекторы соединены с соответствующими первым 2 и вторым 3 токовыми выходами входного дифференциального каскада 1, а эмиттеры связаны со второй 9 шиной источника питания, буферный усилитель 10, вход которого соединен со вторым 3 токовым выходом входного дифференциального каскада 1.

Существенный недостаток известного ДУ состоит в том, что при реализации двухполюсников нагрузки 5 и 6 в виде низкоомных резисторов (500-1000 Ом) его коэффициент усиления получается небольшим.

Основная задача предполагаемого изобретения состоит в повышении в 8-20 раз коэффициента усиления по напряжению при использовании низкоомных двухполюсников нагрузки (например, R5=R6=700 Ом).

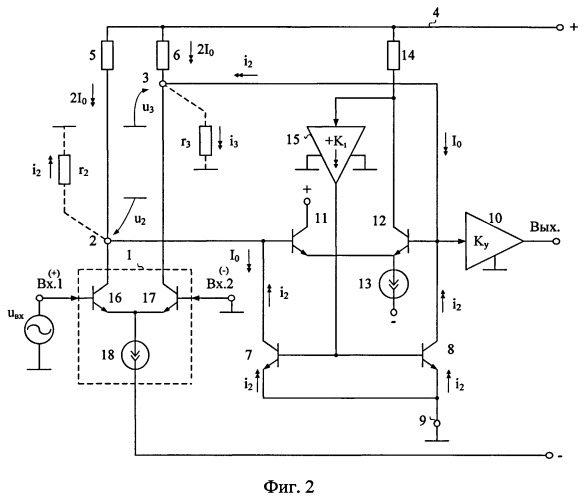

Поставленная задача достигается тем, что в дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, связанными с первой 4 шиной источника питания через первый 5 и второй 6 двухполюсники нагрузки, первый 7 и второй 8 выходные транзисторы, базы которых объединены, коллекторы соединены с соответствующими первым 2 и вторым 3 токовыми выходами входного дифференциального каскада 1, а эмиттеры связаны со второй 9 шиной источника питания, буферный усилитель 10, вход которого соединен со вторым 3 токовым выходом входного дифференциального каскада 1, предусмотрены новые элементы и связи - в схему введены первый 11 и второй 12 дополнительные транзисторы, эмиттеры которых соединены с первым 13 дополнительным токостабилизирующим двухполюсником, базы связаны с соответствующими первым 2 и вторым 3 токовыми выходами входного дифференциального каскада 1, коллектор второго 12 дополнительного транзистора соединен через второй 14 дополнительный токостабилизирующий двухполюсник с первой 4 шиной источника питания и подключен ко входу дополнительного неинвертирующего усилителя 15, выход которого соединен с объединенными базами первого 7 и второго 8 выходных транзисторов.

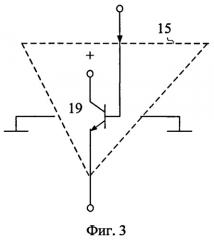

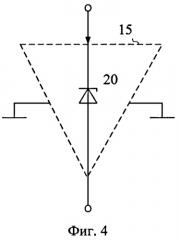

Схема заявляемого устройства, соответствующего формуле изобретения, показана на фиг.2. На фиг.3, 4 показаны частные случаи реализации дополнительного неинвертирующего усилителя 15.

На фиг.5 - 6 показаны схема ДУ-прототипа (фиг.5) и

схема заявляемого ДУ (фиг.6) в среде компьютерного моделирования Cadence на моделях интегральных транзисторов IHP, а на фиг.7 - зависимость коэффициента усиления по напряжению сравниваемых схем (фиг.5, 6) без элементов частотной коррекции. Данные графики показывают, что несмотря на применение низкоомных двухполюсников нагрузки 5 и 6 (R5=R6=600 Ом) коэффициент усиления по напряжению предлагаемого ДУ улучшается более чем на порядок (на 29,0 дБ) в сравнении с Kу известного устройства. Это важное достоинство предлагаемого ДУ при его реализации в рамках технологического процесса SGB25VD.

На фиг.8 приведена зависимость коэффициента усиления по напряжению сравниваемых схем (фиг.5, 6) с элементами частотной коррекции (Скор=4 пФ).

На фиг.9 приведена зависимость коэффициента усиления по напряжению сравниваемых схем (фиг.5, 6) со 100% отрицательной обратной связью без элементов частотной коррекции.

На фиг.10 приведена зависимость коэффициента усиления по напряжению сравниваемых схем (фиг.5, 6) со 100% отрицательной обратной связью с элементом частотной коррекции (Скор=4 пФ).

Дифференциальный усилитель с повышенным коэффициентом усиления фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, связанными с первой 4 шиной источника питания через первый 5 и второй 6 двухполюсники нагрузки, первый 7 и второй 8 выходные транзисторы, базы которых объединены, коллекторы соединены с соответствующими первым 2 и вторым 3 токовыми выходами входного дифференциального каскада 1, а эмиттеры связаны со второй 9 шиной источника питания, буферный усилитель 10, вход которого соединен со вторым 3 токовым выходом входного дифференциального каскада 1. В схему введены первый 11 и второй 12 дополнительные транзисторы, эмиттеры которых соединены с первым 13 дополнительным токостабилизирующим двухполюсником, базы связаны с соответствующими первым 2 и вторым 3 токовыми выходами входного дифференциального каскада 1, коллектор второго 12 дополнительного транзистора соединен через второй 14 дополнительный токостабилизирующий двухполюсник с первой 4 шиной источника питания и подключен ко входу дополнительного неинвертирующего усилителя 15, выход которого соединен с объединенными базами первого 7 и второго 8 выходных транзисторов. В частном случае на фиг.2 входной дифференциальный каскад 1 реализован на транзисторах 16, 17 и двухполюснике 18. Дополнительный неинвертирующий усилитель тока может выполняться на транзисторе 19 (фиг.3) или стабилитроне 20 (фиг.4).

Рассмотрим работу предлагаемого устройства фиг.2.

В статическом режиме коллекторные токи (Iкi) транзисторов 16, 17 устанавливаются двухполюсником 18:

где I0=I18/2.

Через двухполюсники нагрузки 5 и 6 при введении общей отрицательной обратной связи протекают статические токи, равные 2I0.

Определим коэффициент усиления по напряжению схемы ДУ фиг.2.

Если на вход Bx.(+)1 подается напряжение uвх, то это вызывает увеличение коллекторного тока транзистора 16 и уменьшение коллекторного тока транзистора 17. Как следствие, напряжение на токовом выходе 3 увеличивается (u3>0). При этом за счет отрицательной обратной связи через дополнительный неинвертирующий усилитель 15 обеспечивает равенство u3≈u2, где u2 - приращение напряжения на первом 2 токовом выходе.

Изменение u2 приводит к изменению тока i2 через эквивалентное сопротивление r2 в цепи первого 2 токового выхода входного дифференциального каскада 1:

где r2=R5||Rвыx.2||Rвыx.7,

R5 - сопротивление двухполюсника нагрузки 5;

Rвых.2 - выходное сопротивление входного дифференциального каскада 1 по первому 2 токовому выходу;

Rвых.7 - выходное сопротивление транзистора 7.

Причем

где Uэрли - напряжение Эрли транзистора 7;

r16=rэ17=2φт/I18 - сопротивления эмиттерных переходов транзисторов 16 и 17;

µ12 - коэффициент внутренней обратной связи транзистора 16.

Приращение тока i2 за счет отрицательной обратной связи через дополнительный неинвертирующий усилитель 15 поступает в коллектор транзистора 7 и далее на его выход - в цепь второго 3 токового выхода входного дифференциального каскада 1. Следует обратить внимание на то, что в заявляемой схеме вследствие ее структурных особенностей обеспечивается равенство переменных напряжений

Поэтому в узле 3 происходит взаимная компенсация тока через r3 током через r2=r3.

Если в частном случае выбрать r2=r3, то эквивалентное сопротивление в узле 3 (R3.экв), влияющее на Kу, будет практически определяться сопротивление нагрузки ДУ, приведенным к узлу 3.

Поэтому коэффициент усиления по напряжению предлагаемой схемы фиг.2 слабо зависит от сопротивлений двухполюсников 5 и 6, которые могут быть достаточно низкоомными.

Таким образом, в схеме фиг.2 на один-два порядка уменьшается влияние сопротивлений двухполюсников нагрузки 5 и 6 на коэффициент усиления Kу по напряжению ДУ.

В результате предлагаемое схемотехническое решение улучшает более чем на порядок Kу.max (на 29 дБ), причем это обеспечивается при использовании низкоомных резисторов в качестве двухполюсников 5 и 6 (R5=R6=600 Ом), а также при низковольтном напряжении питания (±2 В).

Представленные на фиг.7, 8, 9, 10 графики подтверждают данные теоретические выводы.

Таким образом, предлагаемое устройство при его реализации в рамках техпроцесса SGB25VD имеет существенные преимущества по коэффициенту усиления по напряжению Kу в сравнении с известным ДУ.

Источники информации

1. Патент Франции №2409640.

2. Патент США №5.886.577.

3. Патент Англии GB 2008883.

4. Патентная заявка США US 2009/108882, fig.3.

5. Патент Японии JP 54079553.

6. Патент WO 9621271.

7. Патент США №4276485.

8. Патентная заявка US 2006/0181347, fig.2.

9. Патентная заявка WO 2009/042474A2, fig.5.

10. Патент США №6.396.346.

11. Патент США №4.001.608, fig.1.

12. Budyakov A. Design of Fully Differential OpAmps for GHz Range Applications [Текст] / Budyakov A., Schmalz K., Prokopenko N., Scheytt C., Ostrovskyy P. // Проблемы современной аналоговой микросхемотехники: сб. материалов VI Международного научно-практического семинара. В 3-х ч. Ч.1. Функциональные узлы аналоговых интегральных схем и сложных функциональных блоков / под ред. Н.Н.Прокопенко. - Шахты: Изд-во ЮРГУЭС, 2007 - С.106-110.

13. S.P.Voinigescu, et al. Design Methodology and Applications of SiGe BiCMOS Cascode Opamps with up to 37-GHz Unity Gain Bandwidth, IEEE CSICS, Techn. Digest, pp.283-286, Nov. 2005, фиг.2.

14. S.P.Voinigescu, et al. SiGe BiCMOS for Analog, High-Speed Digital and Millimetre-Wave Applications Beyond 50 GHz, IEEE BCTM, p.1-8, Oct. 2006.

15. Патент США №4.274.394, фиг.2.

16. Патент США №3.619.797.

17. Патент США №3.622.902.

18. Патент США №3.440.554.

19. А.с. СССР №299013.

20. Патент Англии №1.175.329, Н3Т.

21. Патент США №3.304.512.

22. Патент США №4.371.93.

23. А.с. СССР №421105.

24. А.с. СССР №764100.

25. А.с. СССР №669471.

Дифференциальный усилитель с повышенным коэффициентом усиления, содержащий входной дифференциальный каскад с первым и вторым токовыми выходами, связанными с первой шиной источника питания через первый и второй двухполюсники нагрузки, первый и второй выходные транзисторы, базы которых объединены, коллекторы соединены с соответствующими первым и вторым токовыми выходами входного дифференциального каскада, а эмиттеры связаны со второй шиной источника питания, буферный усилитель, вход которого соединен со вторым токовым выходом входного дифференциального каскада, отличающийся тем, что в схему введены первый и второй дополнительные транзисторы, эмиттеры которых соединены с первым дополнительным токостабилизирующим двухполюсником, базы связаны с соответствующими первым и вторым токовыми выходами входного дифференциального каскада, коллектор второго дополнительного транзистора соединен через второй дополнительный токостабилизирующий двухполюсник с первой шиной источника питания и подключен ко входу дополнительного неинвертирующего усилителя, выход которого соединен с объединенными базами первого и второго выходных транзисторов.